时钟树综合前的时钟网络如图8.27所示,呈发射状。为了平衡寄存器到时钟端口的延时,时钟树综合通过许多专用的时钟缓冲单元来搭建平衡的网状结构。也就是基于如上原因,时钟树综合这一步骤在数字物理设计流程中,一般在布局完成后进行。具体到Encounter工具,Encounter的时钟树工具现在版本使用的有两个时钟树综合引擎,两者均有读入SDC约束的能力。......

2023-06-26

本节以CK engine为例来详细介绍Encounter时钟树综合的方法。CK engine需要的输入文件为ctstch文件,控制时钟树生成的级数、长度和单元等信息。

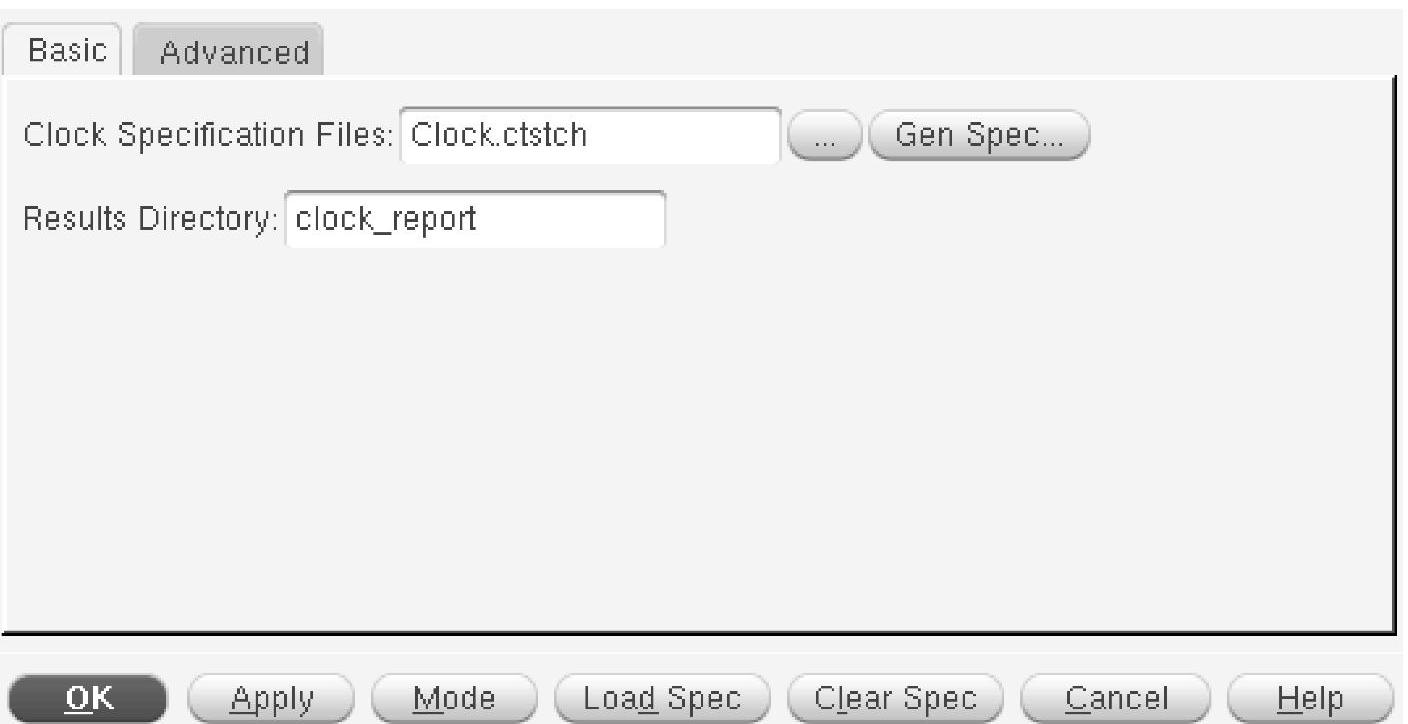

首先使用操作clock-synthesize clock tree,出现synthesize clock tree窗口,如图8.28所示。

图8.28 synthesize clock tree窗口

可单击“...”按钮选择ctstch文件路径,也可选择“Gen Spec...”按钮生成一份新的ctstch文件模板,在此基础上进行简单修改即可成为一份可行的ctstch文件。

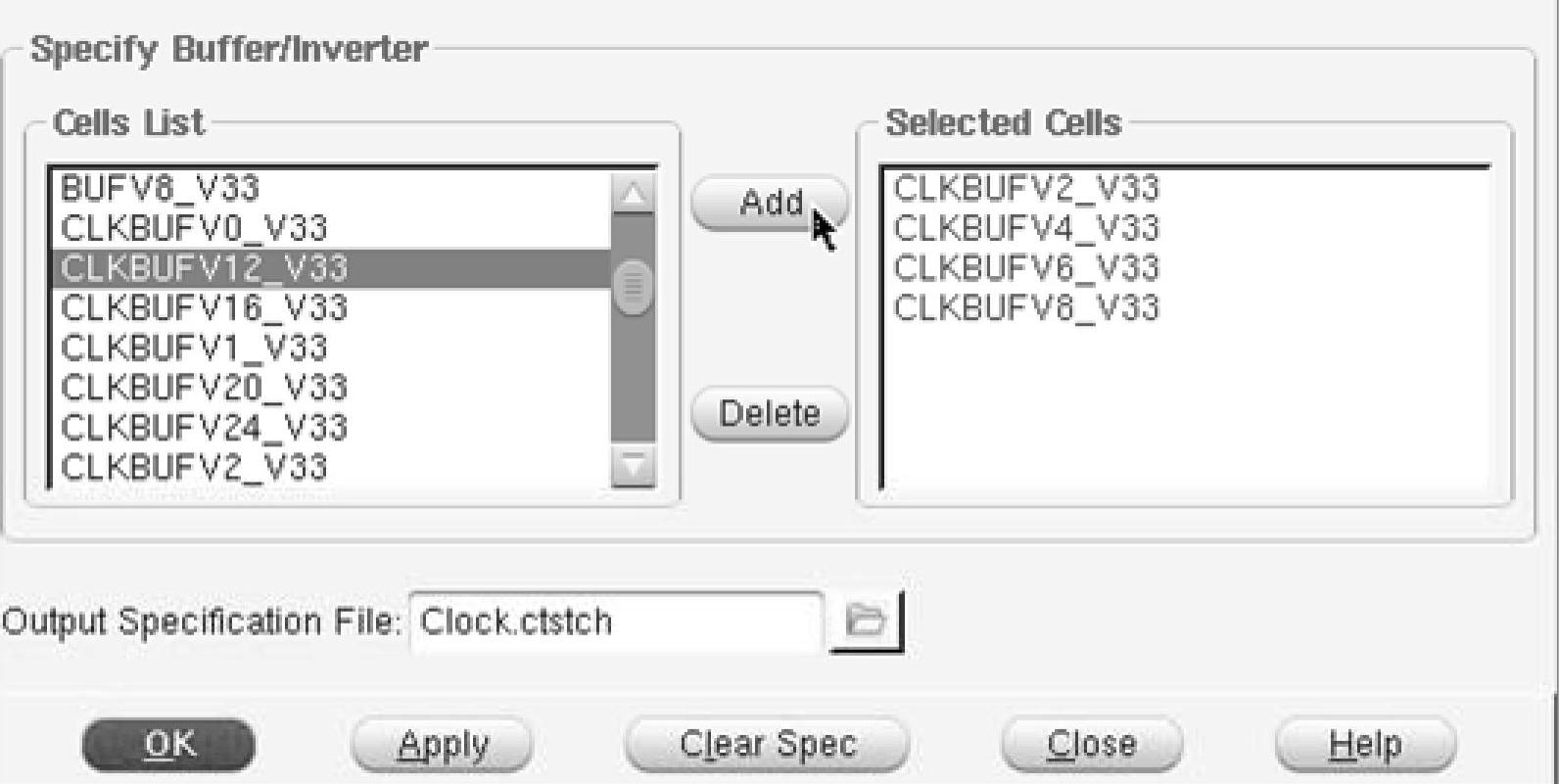

图8.29即为generate clock spec窗口。首先在Output Specification File中选择ctstch文件的存储位置,其次在Cells List中选择时钟树的cell,一般选择中等驱动能力的时钟树专用Buffer和Inverter作为时钟树单元。本节选择CLKBUFV2_V33、CLKBUFV4_V33、CLKBUFV6_V33、CLKBUFV8_V33和CLKBUFV12_V33等5个单元,单击“Add”按钮将Cells List中的单元加入Selected Cells中。请注意CLKBUF由于单元延时较小,应用于设计中会使得面积增大,所以一般使用set-DontUse在非时钟树生成阶段加以禁用。最后,单击选择“OK”按钮,保存ctstch文件,并返回到synthesize clock tree窗口。此时可使用Vi等文本编辑工具编辑ct-stch文件的内容,使得时钟树的约束结果最优化。

图8.29 generate clock spec窗口

在返回到synthesize clock tree窗口之后,单击“OK”按钮开始时钟树综合(CTS)并完成时钟树相关布线。

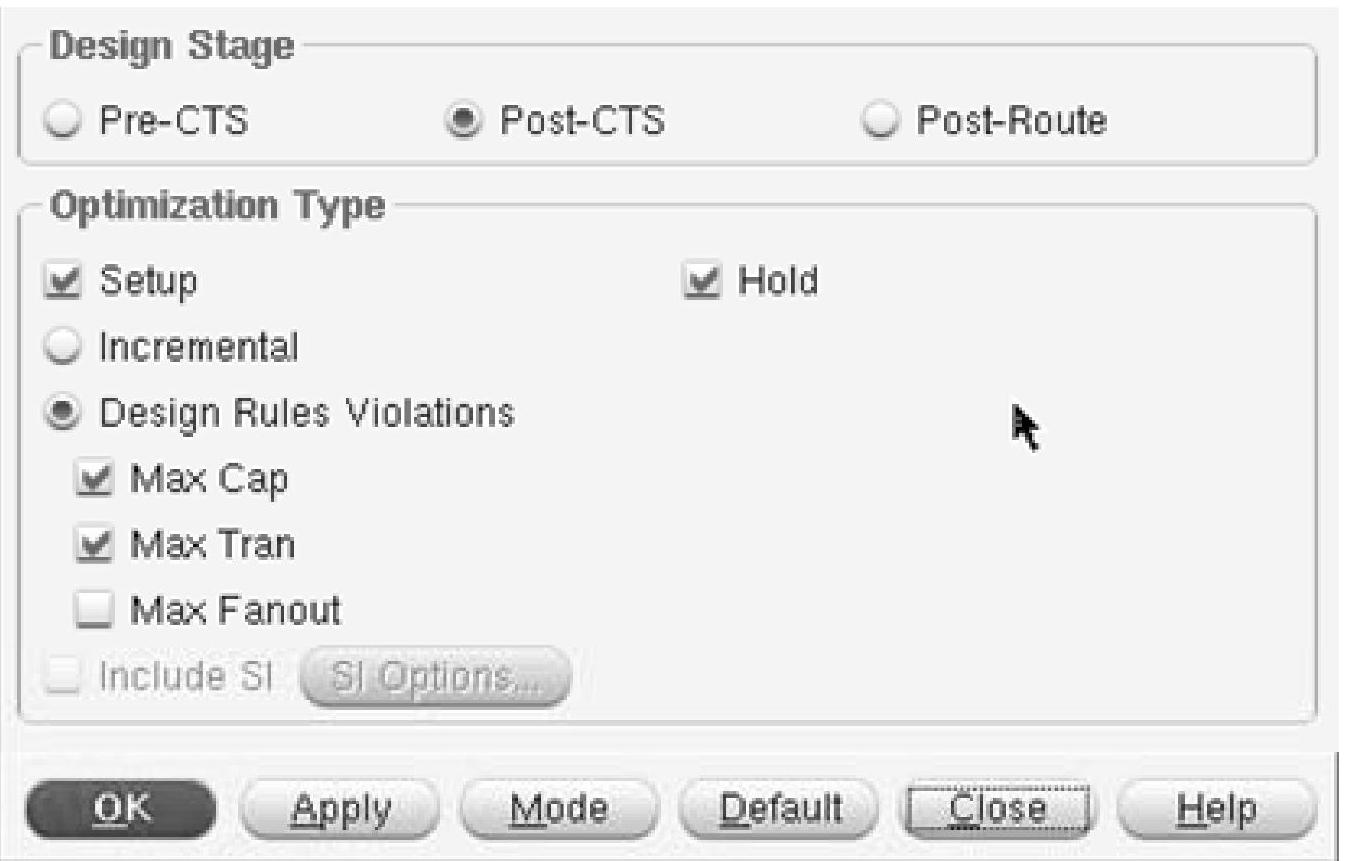

时钟树综合完成后,进行CTS后时序优化。使用操作选择Optimize→Optimize Design,调出Optimization窗口,如图8.30所示。将Design Stage选择为Post-CTS,Optimization Type选择Setup和Hold,其他选项使用默认值即可。

图8.30 generate clock spec窗口

进行完此步骤后可使用Browser clock tree等工具观察时钟树结构并进行优化。至此时钟树综合相关内容告一段落。

有关CMOS集成电路EDA技术的文章

时钟树综合前的时钟网络如图8.27所示,呈发射状。为了平衡寄存器到时钟端口的延时,时钟树综合通过许多专用的时钟缓冲单元来搭建平衡的网状结构。也就是基于如上原因,时钟树综合这一步骤在数字物理设计流程中,一般在布局完成后进行。具体到Encounter工具,Encounter的时钟树工具现在版本使用的有两个时钟树综合引擎,两者均有读入SDC约束的能力。......

2023-06-26

随后便可进行时钟树综合的相关设置,主要设置步骤如下:1.设置时钟树综合相关的DRC值在一个设计中,时钟网络往往会需要比其他电路更为严格的DRC要求,以保证时钟树上的延时和transition相对稳定,使得最终的skew不超过设计预期。......

2023-06-26

完成了上述设置后,就可以进行时钟树生成的3个核心命令。随后可以通过report_timing/report_constraint-all来检查各个scenario下的时序情况,通常而言,如果时钟树相关的设置没有大的问题,setup不会有较大的违例,但是由于之前一直将时钟网络视为零延时网络,会在初步时钟树生成后产生hold违例。......

2023-06-26

特殊布线分为电源布线以及时钟树布线。根据EDI的数字流程,电源布线在布图规划的时候进行;而时钟树布线在时钟树生成之后进行,先于时钟树生成后的时序优化以及信号线的布线。综上所述,顶层金属更适合用作电源布线,电源线的宽度需要通过设计评估最大工作电流、最大瞬态电流以及电流密度计算而得。......

2023-06-26

如图6.34所示,时钟周期定义为10ns,按设计规格,加法器的延迟为6个时钟周期。图6.34 多时钟电路设计如图6.35所示,DC将会仅仅在第6个时钟上升沿,即60ns处,建立时序分析。图6.36 多时钟保持时间约束保持时间将会提早5个时钟周期,所以加法器d允许延迟为Thold<加法器允许的延迟<60-Tsetup。图6.37是另一个多时钟周期的例子,图中乘法器运算为2个时钟周期,加法器运算为1个时钟周期,其约束为图6.37 多时钟电路设计......

2023-06-26

如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。图6.27 多时钟同步设计CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。图6.30 多时钟同步输出约束DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。......

2023-06-26

单级萃取萃取剂与水经一次充分混合接触,达到平衡后即进行分相,称为单级萃取。多级逆流萃取只在最后一级使用新鲜的萃取剂,其余各级都是与后一级萃取过的萃取剂接触,以充分利用萃取剂的能力。这种流程体现了逆流萃取传质推动力大、分离程度高、萃取剂用量少的特点,因此,这种方法也称为多级多效萃取,简称多效萃取。......

2023-06-19

相关推荐