Timing菜单内是与时序相关的选项。其中Floorplan View主要应用于Floorplan规划,Omoeba View主要是为了观察设计层次以及模块位置,Physical View为了观察芯片最终状态与布线信息。基本工具栏的第二行是对于版图的操作工具栏。图8.7 EDI工具栏下面讲述使用EDI进行设计的读入的方法。图8.9 设计读入后显示界面设计的读入与存储分别可以通过File→Restore Design与File→Save Design来加以实现。......

2023-06-26

布图规划与布局流程主要使用菜单栏Floorplan、Power、Place三个菜单指令下的操作内容。基本操作包括:任意形状Floorplan的编辑,相关block的放置;特殊单元的放置;Global net connect的制定;Power ring和Stripe的编辑,Follow pins的连接;布局;布局后优化。下面将详述如何利用EDI进行上述基本操作。

1)Floorplan编辑。Floorplan编辑常用操作主要有下面3条:选择Floorplan→Specify Floorplan、选择Floorplan→Relative Floorplan-Edit Constraint、选择Floorplan→Clear Floorplan。其中,第一个操作主要功能为制定Floorplan的形状和大小。第二个操作主要功能为制定几个不同模块间的尺寸约束。第三个操作主要功能为全部或者指定部分清除Floorplan中内容。下面分别加以讲述。

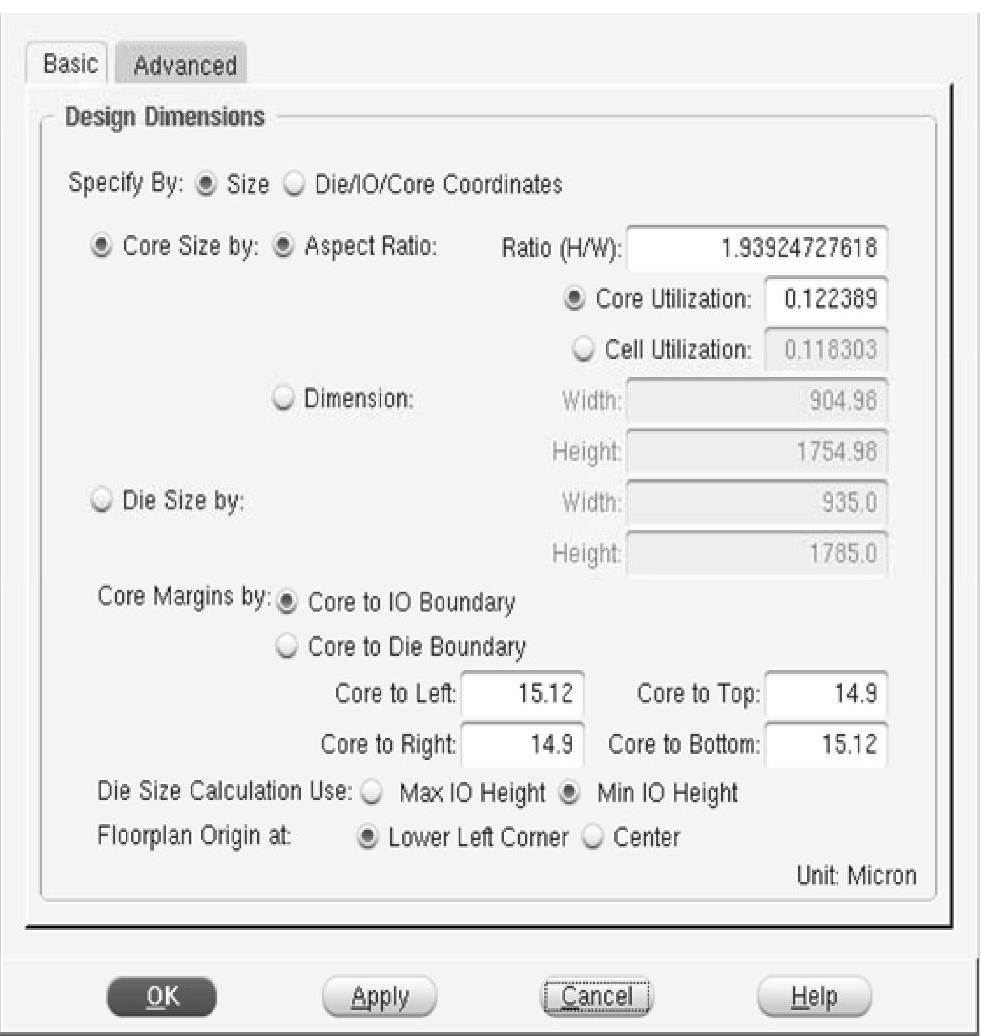

首先选择Floorplan→Specify Floorplan选项,打开Specify Floorplan窗口如图8.15所示,选择使用Size的方式来进行设计:Specify→Size。选择使用Core的Size来定义设计:Core Size by→Aspect Ratio,设置Ratio为1.94,设置Core Utilization为0.122。选择适当的Core到Boundary为Power ring留出空余。设置Core Margins by→Core to Boundary到Left Right Top Bottom为15μm(可根据设计实际情况进行微调)。

图8.15 Specify Floorplan窗口

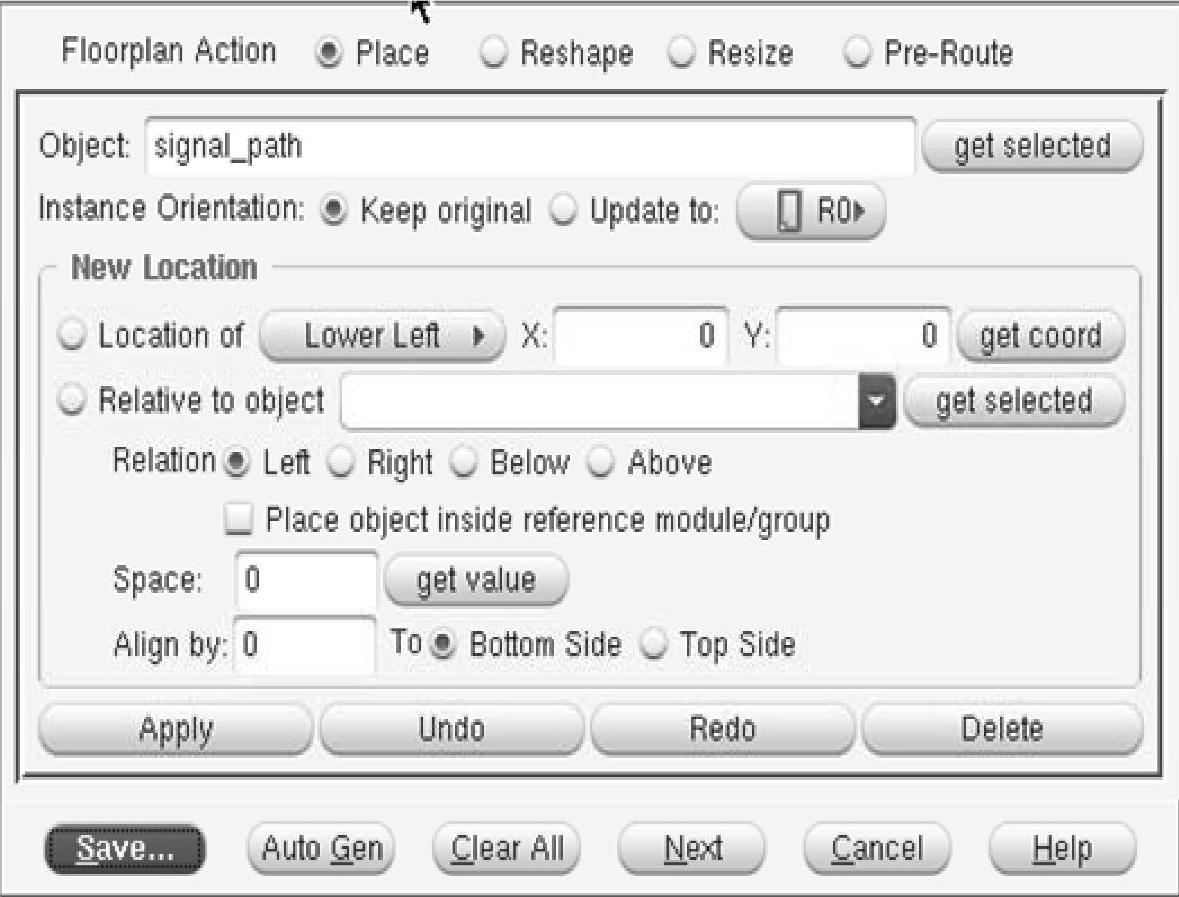

其次,选择Floorplan→Relative Floorplan→Edit Constraint,打开Relative Floor-plan窗口,如图8.16所示。但由于本次设计中只有一个Hard macro,并不用对于几个macro距离进行约束,所以无须对于Relative Floorplan进行设置。

图8.16 Relative Floorplan窗口

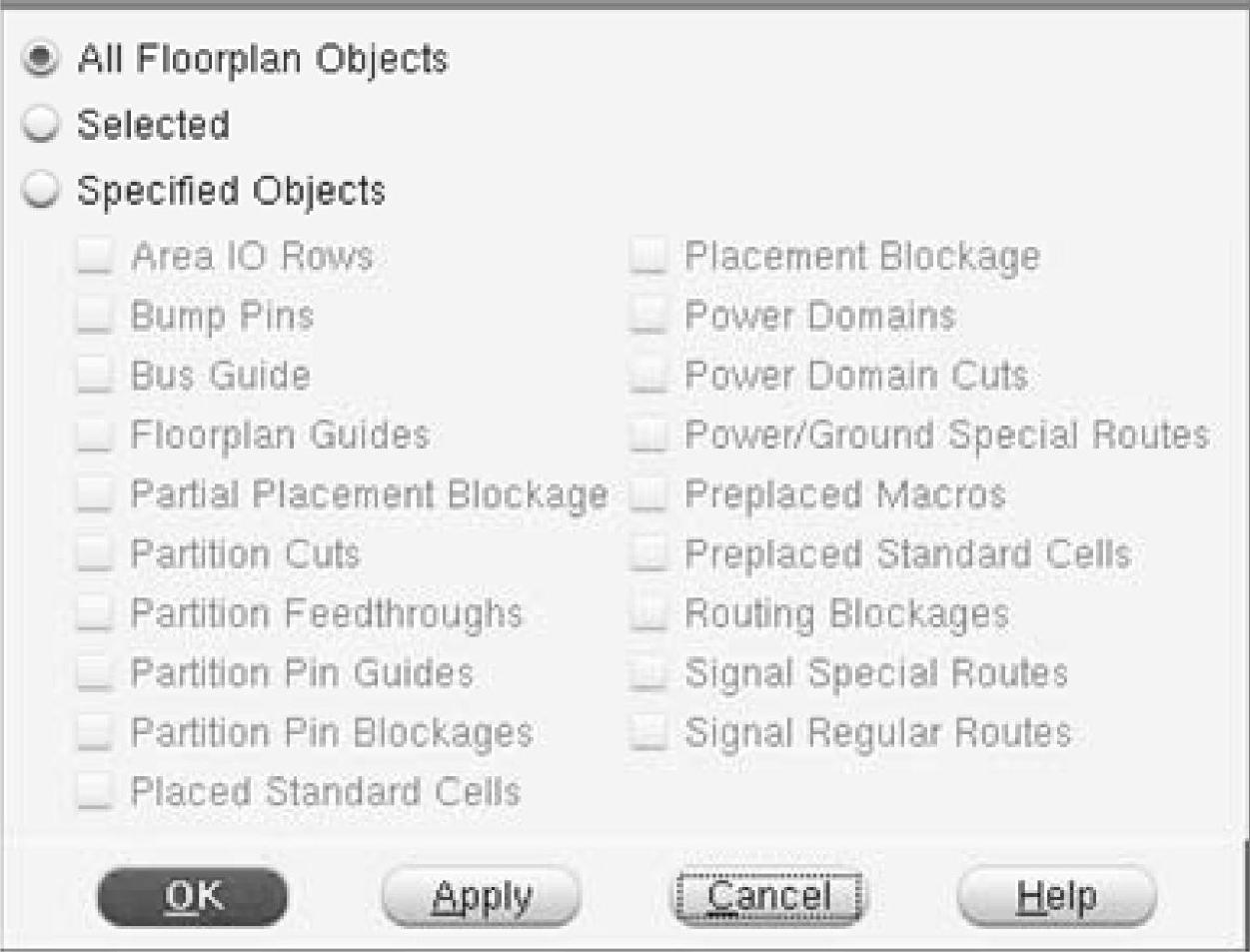

如果需要清除Floorplan局部,例如Power Special Routes,可选择Floorplan→Clear Floorplan进行修改,弹出的Clear Floorplan窗口,如图8.17所示。

图8.17 Clear Floorplan窗口

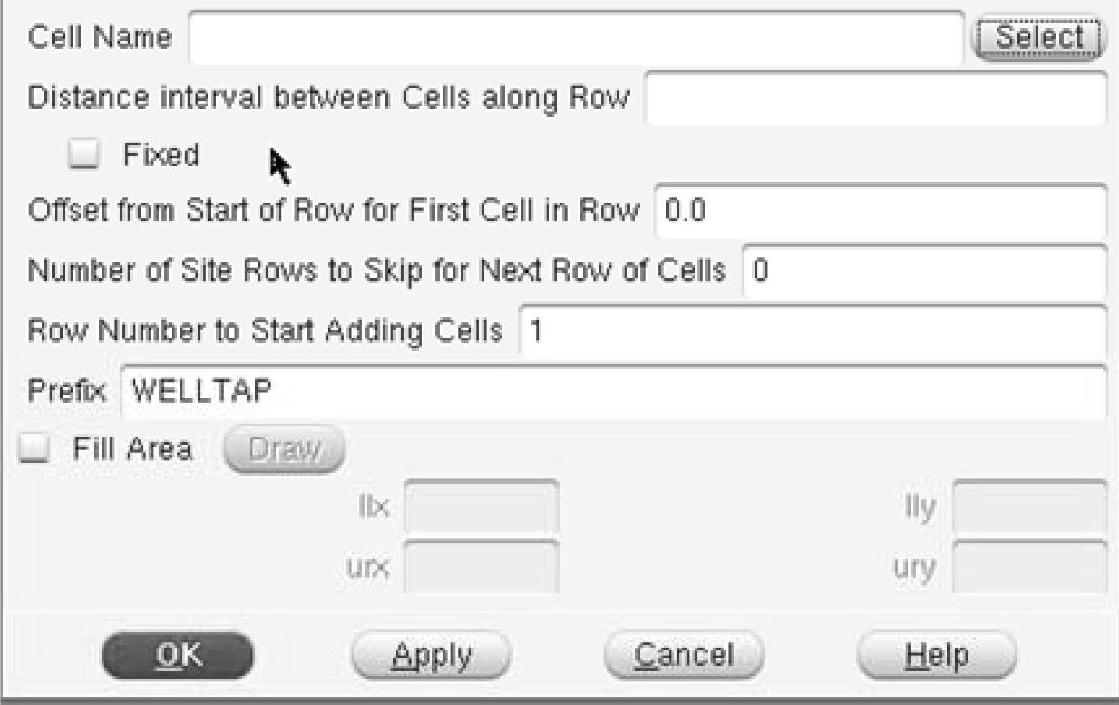

2)特殊单元的放置:在Floorplan阶段,会有部分特殊单元需要首先放置在芯片的Core区域内部。其中,最普遍的两类为Tie High/Tie Low单元和Welltap单元,前者的作用是作为网表中1’b0和1’b1的输入,使得输入Pin不直接与电源、地连接。后者是标准单元区域的衬底接触,通过多个单元共用一个衬底接触来节约设计区域的面积。Tie High/Tie Low单元的添加可使用操作Place→Tie hi/lo cell→Add来进行添加,Welltap可利用操作Place→Physical cell→Add Well Tap打开Add Well Tap Instance窗口来增加。Add Well Tap Instance窗口如图8.18所示。

3)Global net connect的制定:Global net connect是对于电源与地连接关系的定义。该定义可以通过Power→Connect Global nets打开Global net connection窗口加以定义。Global net connection窗口如图8.19所示。

4)Power Ring和Stripe的编辑:在此步骤主要使用的操作分别为Power→Pow-er Planning→Add ring、Power→Power Planning→Add Stripe与Route→Special Route。它们的作用分别为:增加设计需求尺寸的Power ring到芯片设计区域,增加设计需求尺寸的Stripe到芯片设计区域,使用Special Route进行Followpins与电源环线与电源条线的连接。

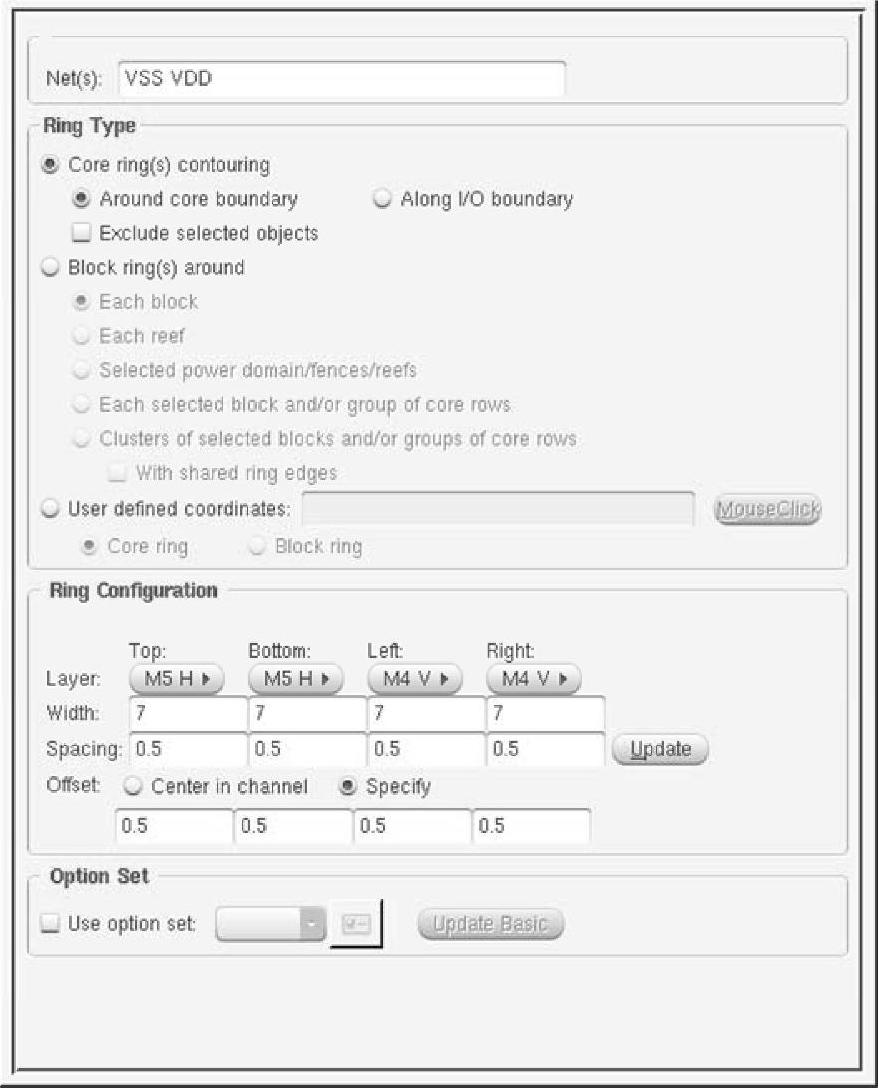

首先是Power ring的形成,选择操作Power→Power Planning→Add Ring,弹出Add Rings窗口如图8.20所示。在Nets填入VDD VSS,即需要生成Power Ring的电源与地的Global net名称。由于本章节设计均不包含IO cell,所以Power Ring选择紧贴core区域即可,因此在ring type区域选择around core boundary。在ring con-figuration区域,由于本设计选择工艺顶层金属为M5,所以选择Top与Bottom使用M5横向走线,Left与Right使用M4纵向走线,Width与Spacing分别设置为7μm与0.5μm。以上数值在实际设计中均可酌情调整。

图8.18 Add Well Tap Instance窗口

图8.19 Global net connection窗口

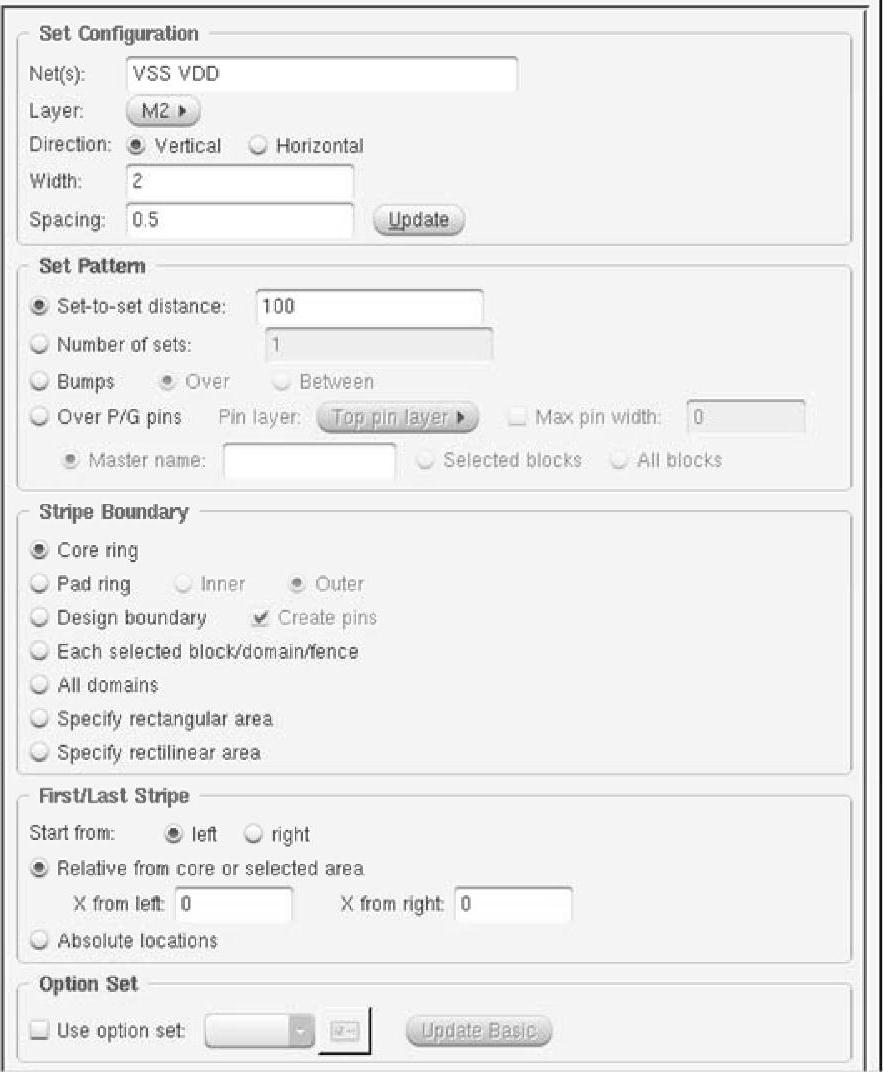

其次是Stripe的形成,使用操作Power→Power Planning→Add Stripe,弹出Add Stripe窗口如图8.21所示。与Power ring的添加类似,Nets选择VDD VSS,由于Stripe

图8.20 Add Rings窗口

图8.21 Add Stripe窗口

横向添加相对会占用更多布线资源,所以选择纵向添加,并使用M4生成电源条线。操作为在Layer选择M4,Direction选择Vertical。Set-to-set distance为两组Stripe之间的间距,本设计将此值设定为100μm。其余选项均使用默认值即可。

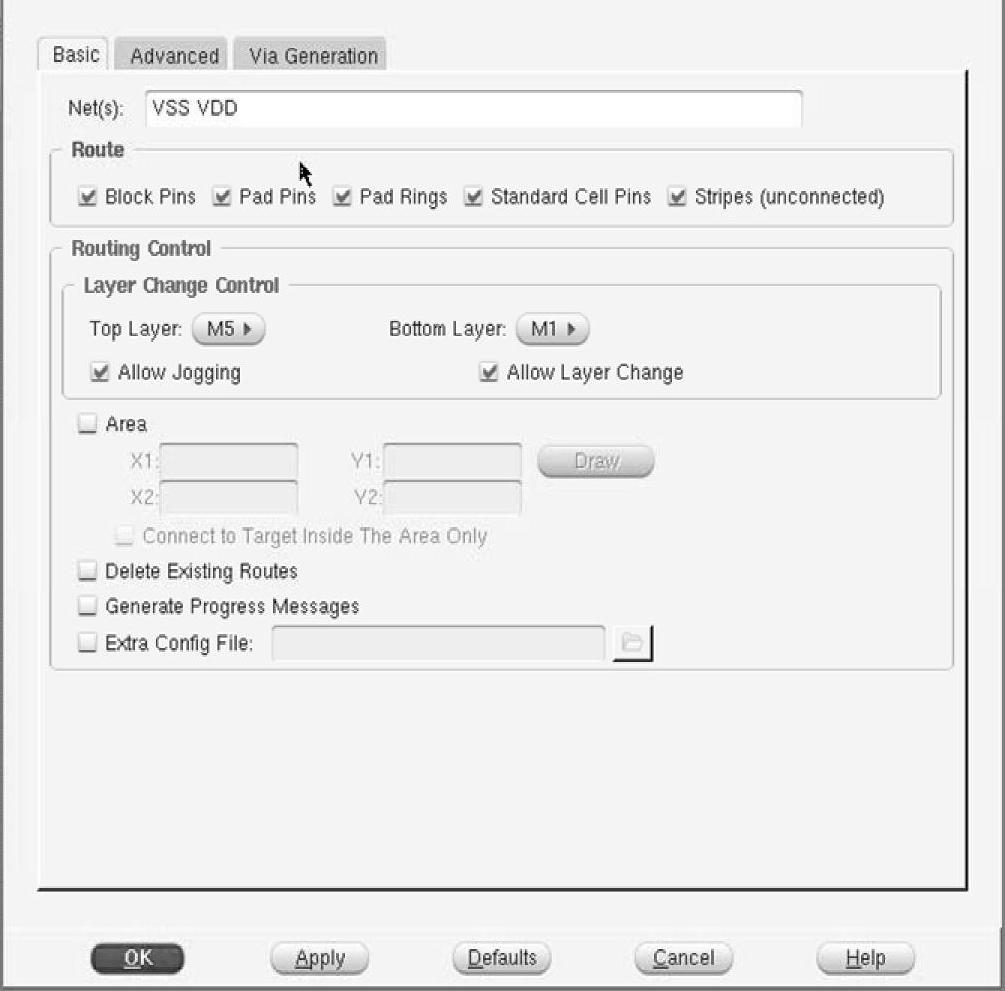

最后进行Follow pins的生成:使用操作route-special route,弹出Sroute窗口如图8.22所示。在Net处选择VDD VSS。其余使用默认值即可。

图8.22 Sroute窗口

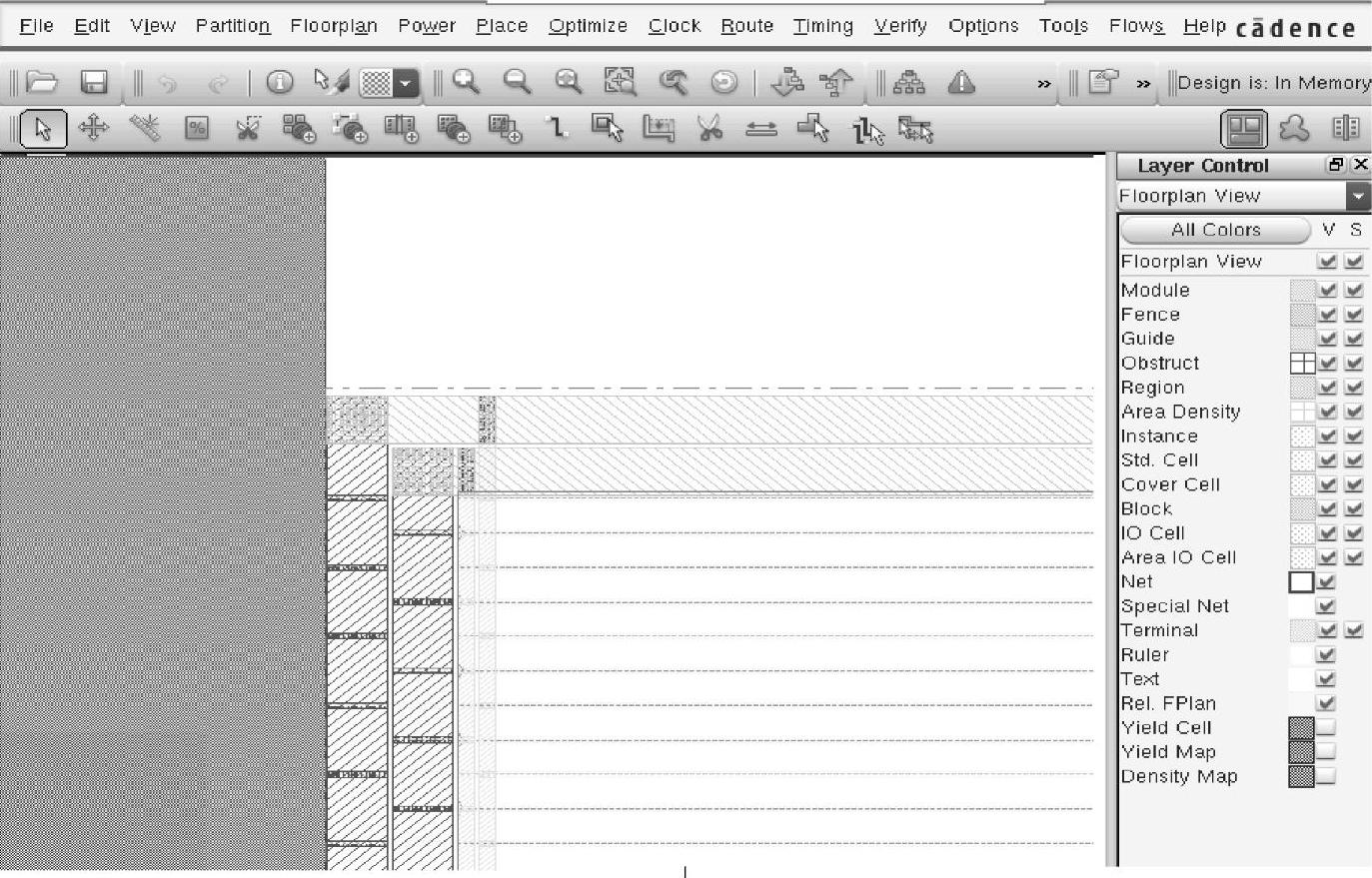

在完成本步骤之后的芯片设计版图局部如图8.23所示(已使用Zoom In功能进行放大)。

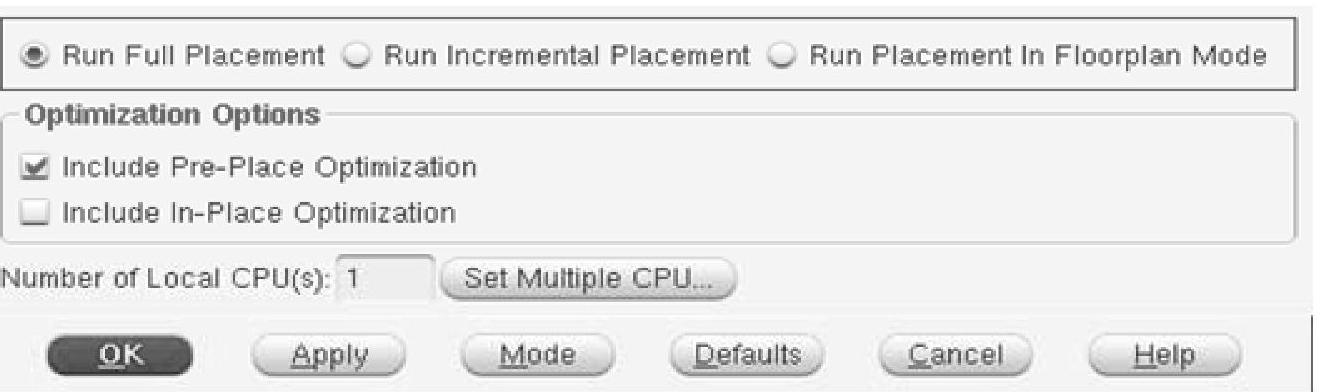

5)布局:使用操作Place→Place Standard Cell,调出Place窗口如图8.24所示。使用默认值即可。

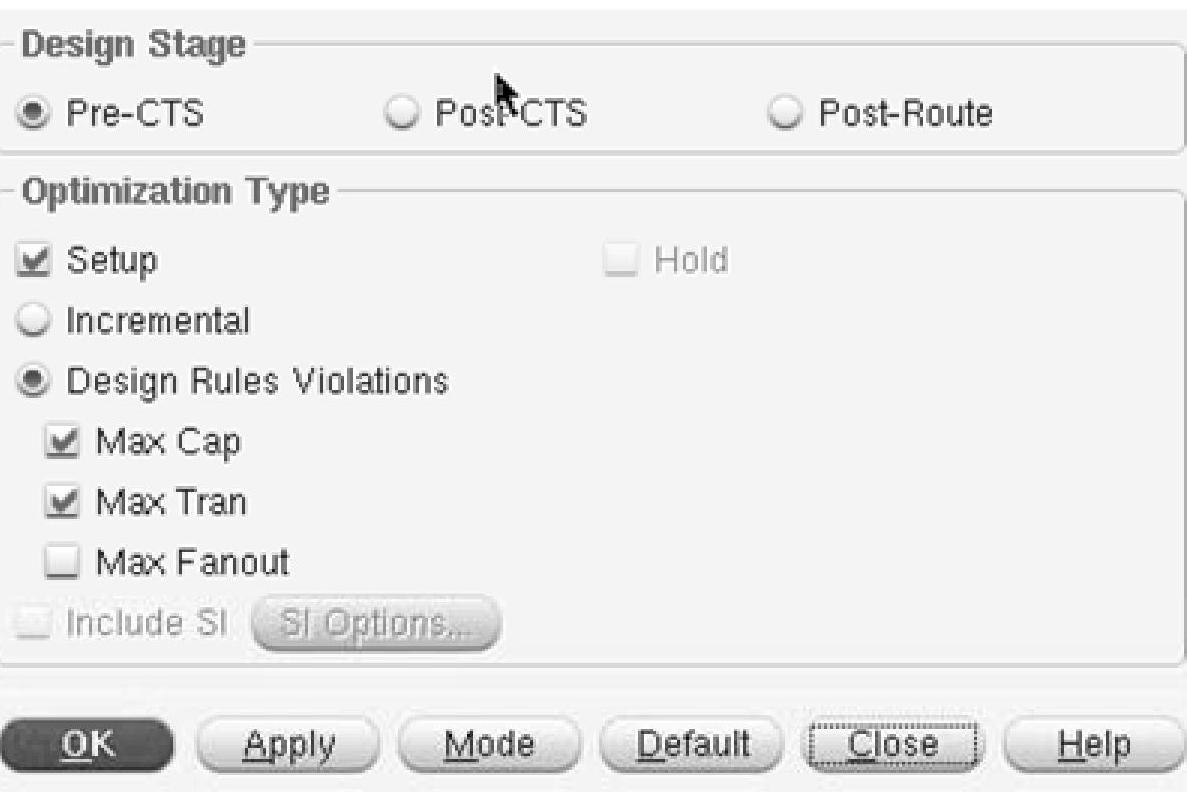

6)布局后优化:使用操作Optimize→Optimize Design,调出Optimization窗口如图8.25所示。使用默认值即可。即Design Stage选择Pre-CTS,Optimization Type选择Setup。

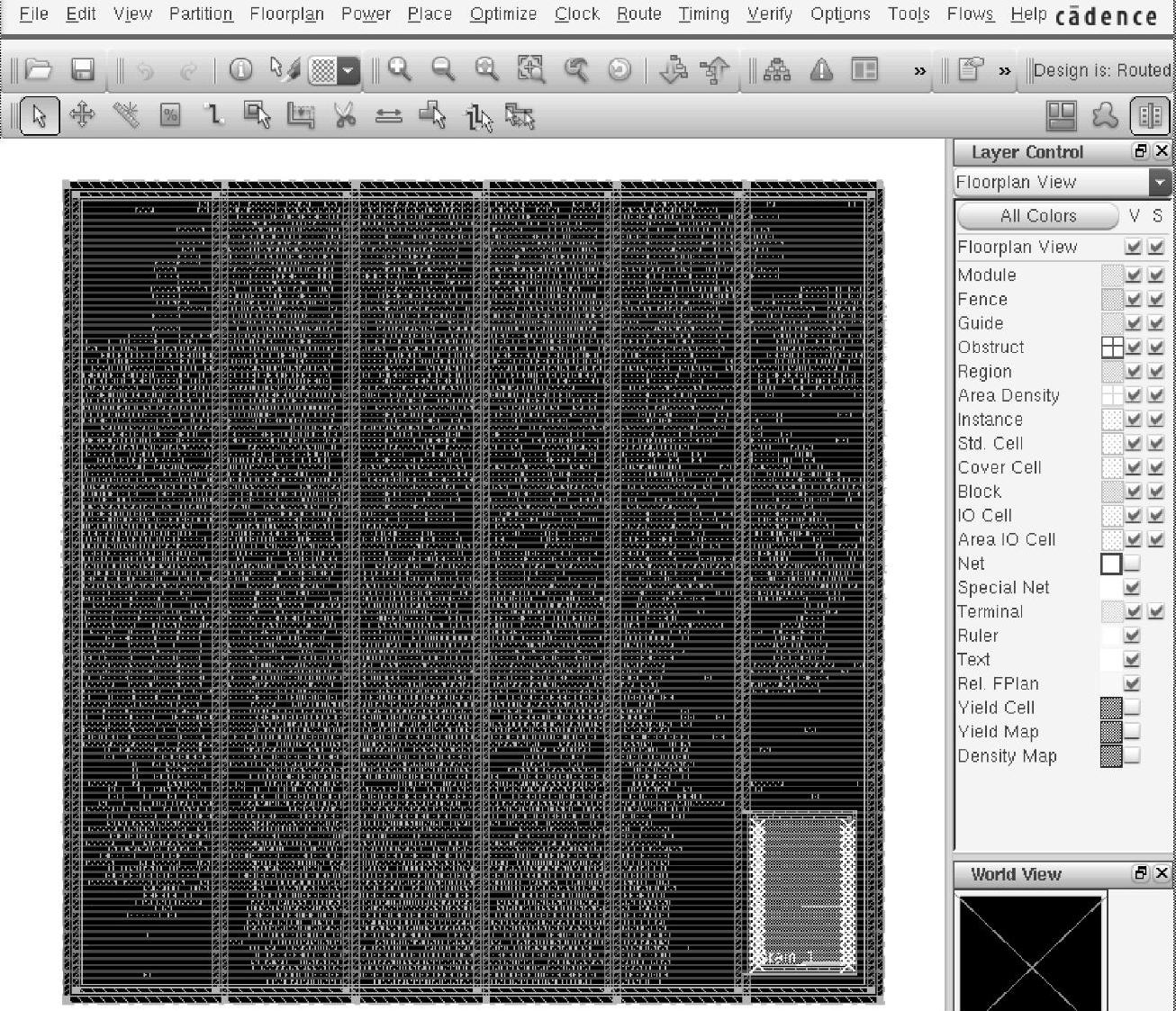

到此步骤完成后的芯片如图8.26所示。

图8.23 完成Power plan后芯片局部

图8.24 Place窗口

图8.25 Optimization窗口

图8.26 Optimization后芯片局部

有关CMOS集成电路EDA技术的文章

Timing菜单内是与时序相关的选项。其中Floorplan View主要应用于Floorplan规划,Omoeba View主要是为了观察设计层次以及模块位置,Physical View为了观察芯片最终状态与布线信息。基本工具栏的第二行是对于版图的操作工具栏。图8.7 EDI工具栏下面讲述使用EDI进行设计的读入的方法。图8.9 设计读入后显示界面设计的读入与存储分别可以通过File→Restore Design与File→Save Design来加以实现。......

2023-06-26

图8.11 数字芯片结构针对Pad limited的设计,如何正确排布输入输出端口顺序使其与产品封装一致,如何复用端口尽量减小输入输出端口数目,是否采用交错型结构代替线性型结构来在单位宽度放入更多的IO数目等往往在实际设计中是工程师较为关注的重点。图8.12 两种IO的比较而Core limited的设计,按照模拟IP形状或者数字设计规模作为制约芯片设计的关键因素加以区分。图8.13 IP放置位置对于布线的影响......

2023-06-26

SYNOPSYS公司的IC Compiler和Cadence公司SoC Encounter是工业界和学术界常用的两种版图布局布线工具。IC CompilerIC Compiler是SYNOPSYS公司开发的新一代布局布线工具。Astro解决方案由于布局、时钟树和布线独立运行,有其局限性。SoC Encounter严格地说,SoC Encounter不仅仅是一个版图布局布线工具,它还集成了一部分逻辑综合和静态时序分析的功能。作为布局布线工具,SoC Encounter在支持28nm先进工艺的同时,还支持1亿门晶体管的全芯片设计。......

2023-06-26

图2.27小型公园与其他公园不同的连接方式自20世纪80年代以来,生态廊道与遗产廊道、游憩通道相结合,形成了综合性多目标的绿道概念,并成为现代城市绿地系统规划中的重要内容。现代绿地系统规划中,绿道规划的内容包括4个方面:①对风景资源、现存绿色通道和历史通道网络的分析。②绿道各组成要素评价。④绿道布局确定。图2.28“珠三角”绿道......

2023-10-11

跳转指令用于实现程序流程的跳转。ARM指令集中的跳转指令跳转的地址空间为当前指令地址32MB。跳转指令有以下四个方面。BL指令用于子程序调用。例如:3.BLX指令BLX{cond}label或RmBLX指令从ARM指令集跳转到label或者Rm指定的地址处执行,并将处理器的工作状态由ARM状态切换到Thumb状态,同时将下一条指令的地址复制到链接寄存器R14中。例如:4.BX指令BX{cond}Rm带状态切换的跳转指令使程序跳转到指令中Rm指定的地址执行程序,Rm的第0位复制到CPSR中T位,bit[31∶1]移入PC。......

2023-11-19

第一节城市布局与规划一、城区布局根据1954年《兰州市总体初步规划》和1988年西固区规划,城区范围东起深沟桥,西至西柳沟,南至山根,北临黄河,面积32.9平方公里。规划确定城市供水规模为56.31万吨/日,主要供水干管采用环状网,局部地区及某些边缘地区采用支状网,以节省资源,使供水普及率在规划期内达100%。中共十一届三中全会后,兰州市召开村镇规划建设工作会议,会后,全区乡镇、村庄全面开展规划建设。......

2023-11-29

1)满足改善城市生态环境的要求改善城市生态环境是城市绿地的首要功能,这项功能的发挥与绿地的布局形式密切相关。4)满足美化城市的要求城市绿地的布局还应考虑与城市的山体、水系、道路、广场、建筑等的结合,形成自然与人工结合的城市环境特色,体现城市特有的自然景观及文化历史,丰富城市轮廓线,衬托建筑,美化市容。......

2023-10-11

监理部组建后,按照DL/5111—2000《水电水利工程施工监理规范》建立正常的工作和文件处理程序,明确了处理期限,首先对监理工作进行了规范化管理。对于每一道工序进行“三检”,并将“三检”结果送交监理工程师,并经签字认可后,方可进行下道工序的施工。施工当中各类报表根据各监理单位规定按时报送。现场出现质量和安全事故,承建单位应及时上报,任何质量事故(缺陷)和安全事故均不得隐瞒监理工程师而自行处理。......

2023-06-21

相关推荐