【摘要】:图8.11 数字芯片结构针对Pad limited的设计,如何正确排布输入输出端口顺序使其与产品封装一致,如何复用端口尽量减小输入输出端口数目,是否采用交错型结构代替线性型结构来在单位宽度放入更多的IO数目等往往在实际设计中是工程师较为关注的重点。图8.12 两种IO的比较而Core limited的设计,按照模拟IP形状或者数字设计规模作为制约芯片设计的关键因素加以区分。图8.13 IP放置位置对于布线的影响

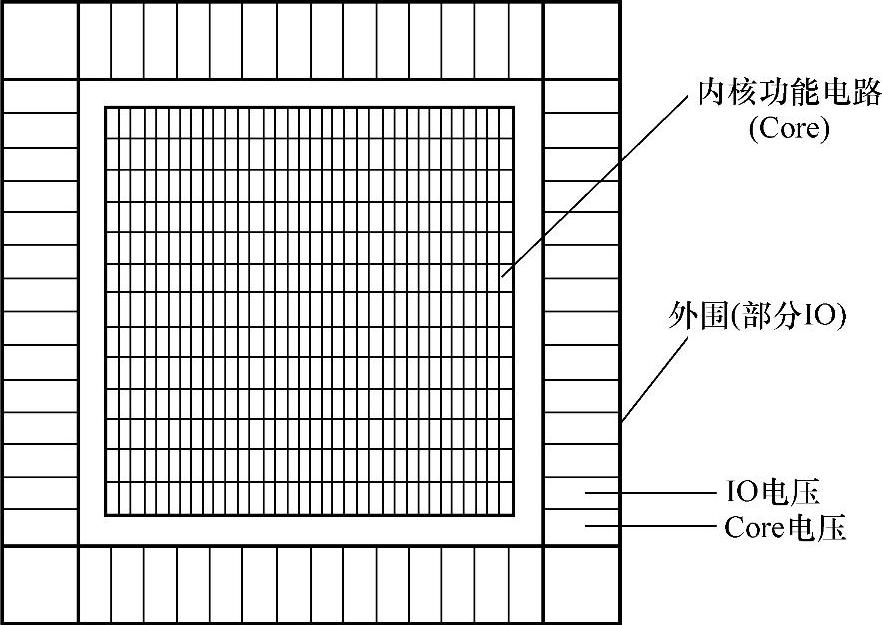

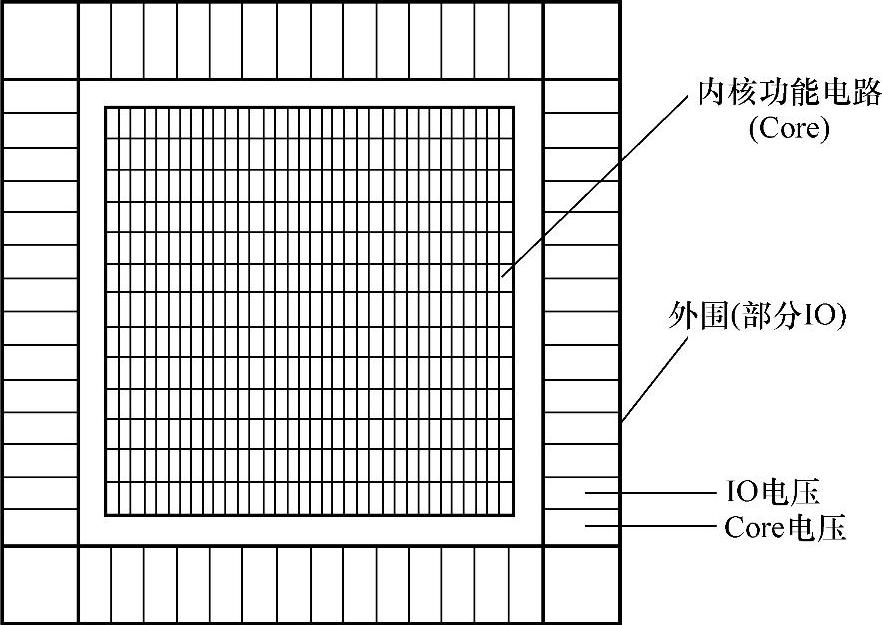

数字芯片结构一般如图8.11所示,包含内核功能电路与外围IO(输入输出)电路。布图规划,首先就需要确定设计的类型。由于设计复杂度不同,芯片一般分为Pad limited和Core limited两类。所谓Pad limited,就是相对的设计较少而输入输出端口较多,造成输入输出单元成为限制芯片最终面积的瓶颈。而所谓Core limit-ed,就是相对输入输出端口较少,而设计复杂度较高,造成设计的面积成为限制芯片最终面积的瓶颈。

图8.11 数字芯片结构

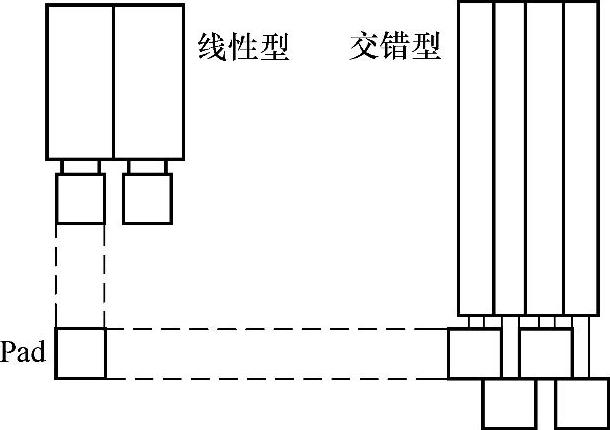

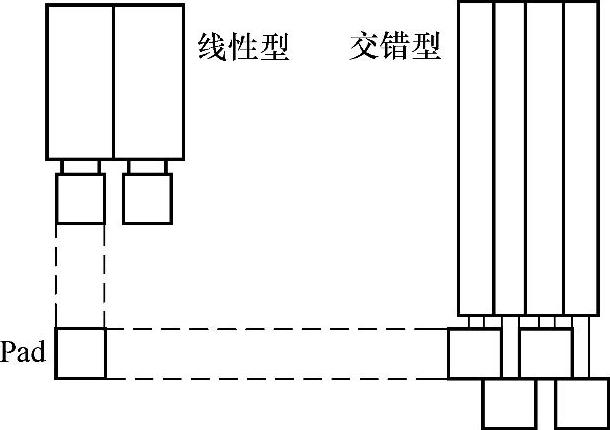

针对Pad limited的设计,如何正确排布输入输出端口顺序使其与产品封装一致,如何复用端口尽量减小输入输出端口数目,是否采用交错型结构(stagger)代替线性型(liner)结构来在单位宽度放入更多的IO数目等往往在实际设计中是工程师较为关注的重点。而线性型和交错型的比较如图8.12所示。

图8.12 两种IO的比较

而Core limited的设计,按照模拟IP形状或者数字设计规模作为制约芯片设计的关键因素加以区分。针对模拟IP形状限制了芯片面积的情况,实际设计中,一般是数字物理设计工程师与模拟版图设计工程师进行沟通和协作优化,将模拟IP形状优化成为数字APR流程中较为容易进行Floorplan的形状;而数字设计规模限制芯片面积的情况,则需要逻辑综合工程师与数字前端工程师进行充分的沟通,进行设计的充分优化。

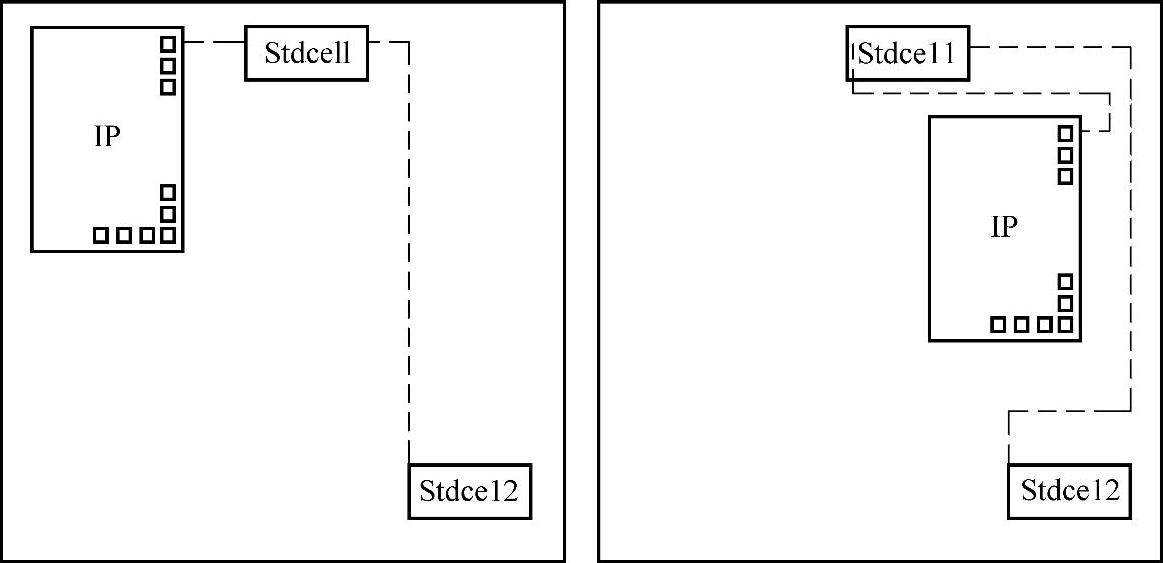

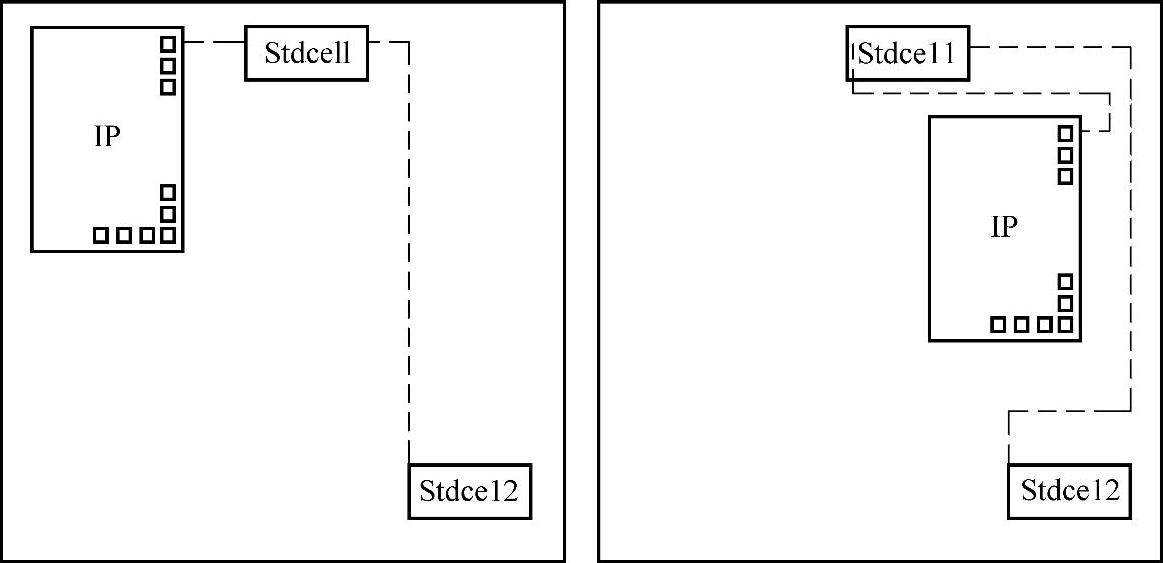

在IP的摆放规律上,一般业界都是遵循“金角银边草肚皮”的原则,模拟IP尽量放置在芯片角落及边缘,以求标准单元在布局的时候能拥有一个较为规整的形状及拥有更多的布线资源。当然,此原则也需要模拟IP的出pin位置尽量满足布线的要求,否则会对后续步骤中的布线带来较大困难。如图8.13所示,Stdcell1和Stdcell2假定为两个位置固定的标准单元,则可看到IP位置的移动,对于三者之间的连线(图中虚线所示)有着较大的影响。IP放置在芯片角落及边缘的时候,连线的总布线长度会减小很多。

图8.13 IP放置位置对于布线的影响

相关推荐