CMOS模拟集成电路设计与传统分立元件模拟电路设计最大的不同在于,所有的有源和无源器件都是制作在同一块硅衬底上,尺寸极其微小,无法再用电路板进行设计验证。模拟集成电路设计包括若干个阶段,图1.1所示为CMOS模拟集成电路设计的一般流程。图1.1 CMOS模拟集成电路设计流程1)系统规格定义;2)电路设计;3)电路仿真模拟;4)版图实现;5)物理验证;6)参数提取后仿真;7)导出设计文件、流片;8)芯片制造;9)测试和验证。......

2023-06-26

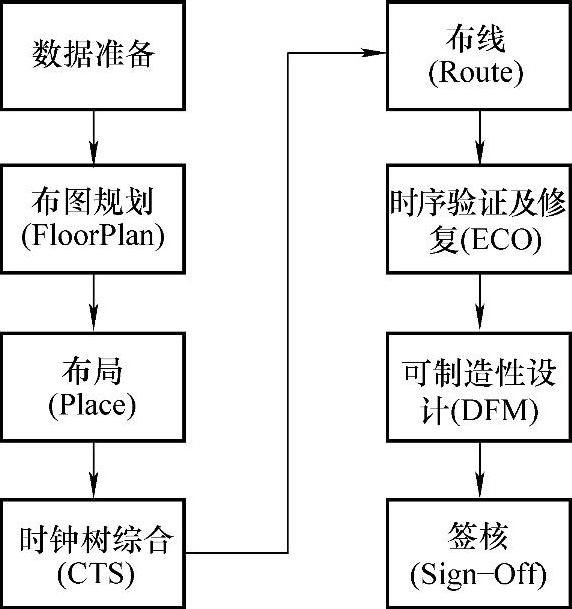

使用Encounter进行后端物理实现的设计流程如图8.1所示。

首先是数据准备方面的工作,对于EDI来说,APR(Automatic Place&Route)之前需要准备的数据主要有:综合后的门级网表(.v)、具有时钟定义及时序约束的综合约束文件(.sdc)、物理库文件(.lef)和时序库文件(.lib)等。详细的文件内容、格式等介绍8.3节会有涉及。

在数据准备完毕并导入工具之后,即可开始布图规划(FloorPlan)。布图规划主要包含下面4方面内容:完成对电源域及电源网络方面的定义(power-plan);宏模块(Macro)的摆放及约束;标准输入输出单元(IO)的摆放;标准单元(standard cell)布局(Place)约束。

图8.1 EDI APR流程

待布图规划完成后,工具会依据布图规划中的物理约束信息及SDC中的时序约束信息进行布局。

时钟树综合(CTS)在布局完成后进行,其目的是通过构造时钟网络结构来驱动芯片中所有的时序逻辑单元(例如寄存器等)。

CTS后,下一个步骤即是布线(Route),布线分为全局布线与局部布线,指在满足种种物理约束的前提下根据电路网表提供的电学连接关系将各个单元连接起来。

然而在布线后的时序分析中,往往还是存在若干时序违例(Time Violation)的时序路径。如果数目较少,一般通过小范围的改动即可使之满足要求,这种改动称作ECO(Engineering Change Order)。

时序验证以及ECO之后,需要进行芯片的可制造性设计(DFM)。DFM包含范围很广,而在APR流程中的DFM主要是进行诸如double via和spread wire width等优化,预防制造过程中由于加工的偏差使得芯片的功能失效。

后端设计最后的步骤为签核(Sign-Off),签核内容包括下面的内容:功能一致性检查、时序检查、物理验证(DRC、LVS、ERC等)、确保给出的GDS文件为正确的版本进行最终的流片。由于本章着重点在EDI的使用,关于此部分内容并不详细展开。

有关CMOS集成电路EDA技术的文章

CMOS模拟集成电路设计与传统分立元件模拟电路设计最大的不同在于,所有的有源和无源器件都是制作在同一块硅衬底上,尺寸极其微小,无法再用电路板进行设计验证。模拟集成电路设计包括若干个阶段,图1.1所示为CMOS模拟集成电路设计的一般流程。图1.1 CMOS模拟集成电路设计流程1)系统规格定义;2)电路设计;3)电路仿真模拟;4)版图实现;5)物理验证;6)参数提取后仿真;7)导出设计文件、流片;8)芯片制造;9)测试和验证。......

2023-06-26

本节采用内嵌在Cadence Virtuoso Layout Editor的菜单选项来启动Calibre PEX。图4.100 打开Miller_OTA版图4)打开Calibre PEX工具。图4.107 Calibre LVS结果查看图形界面11)在Calibre PEX运行后,同时会弹出参数提取后的主网表,如图4.108所示,此网表可以在HSPICE软件中进行后仿真。图4.108 Calibre PEX提出部分的主网表示意图以上就完成了Calibre PEX寄生参数提取的流程。......

2023-06-26

图6.2.1if语句执行流程6.2.1.html根据两个变量的大小关系,使用if条件语句输出对应提示,如下所示。图6.2.2if语句if语句中的表达式布尔值为true,执行语句console.log;,执行完成之后继续执行console.log; 。◇ 表达式expression布尔值为false时,执行语句secondStatement。◇ 支持加入多个else if条件语句。if语句的其他限制:◇ if语句是必选项,else if和else语句是可选项。......

2023-11-08

在UMAT子程序中实现Lemaitre各向同性损伤本构方程需要重点完成以下三部分内容:分别定义材料塑性和损伤的门槛值及演化规律,准确描述材料的塑性和损伤状态。在UMAT中采用一致切线模量矩阵可以保证ABAQUS主体程序采用的Newton迭代法具有二阶收敛速率,减少增量步结束时由于应变增量微小扰动引起的应力变化。图5.1应用UMAT子程序实现损伤本构描述的流程图......

2023-08-26

1)流量控制机制该机制主要用于确保发送端发送的数据量不超过接收端的最大处理能力。TCP的流量控制具体通过滑动窗口算法来实现。地面网络常用TCP的拥塞控制机制主要包括TCP-Tahoe,TCP-Reno,TCP-SACT等。......

2023-07-02

工程项目的竣工验收是建设全过程的最后一道程序,它是建设投资成果转入生产或使用的标志,是全面考核投资效益、检验设计和施工质量的重要环节。由项目经理组织有关职能人员,对拟报竣工工程的情况和条件,根据施工图要求、合同规定和验收标准进行检查验收。......

2023-06-29

⑤借贷合同及有关协议约定的其他义务。参与网络借贷的出借人,应当具备投资风险意识、风险识别能力,拥有非保本类金融产品投资的经历并熟悉互联网。(二)注册开户、开始网络借贷投资假设我们是出借人,以在宜人贷网站注册开户为例,说明网络借贷投资操作流程。出借人选中投资标的后,按照页面提示进行出借资金的操作并予以确认。完成以上五个步骤后,网络借贷投资即告成功。......

2023-07-05

PI教学法是基于概念测试题,实现在课堂上师生互动、生生互动的教学方法。使用PI教学法,教师需要让学生在课前预习,布置一些预习作业要求学生在课前完成。因此,使用PI教学法,教师上课时无须讲授课程的全部内容,学生通过自学和互学后已经掌握的课程内容不需要教师在课堂上讲解。围绕一个概念、观念或主题,使用PI教学法的规则。......

2023-10-26

相关推荐