时钟树综合前的时钟网络如图8.27所示,呈发射状。为了平衡寄存器到时钟端口的延时,时钟树综合通过许多专用的时钟缓冲单元来搭建平衡的网状结构。也就是基于如上原因,时钟树综合这一步骤在数字物理设计流程中,一般在布局完成后进行。具体到Encounter工具,Encounter的时钟树工具现在版本使用的有两个时钟树综合引擎,两者均有读入SDC约束的能力。......

2023-06-26

随后便可进行时钟树综合的相关设置,主要设置步骤如下:

1.设置时钟树综合相关的DRC值

在一个设计中,时钟网络往往会需要比其他电路更为严格的DRC要求,以保证时钟树上的延时和transition相对稳定,使得最终的skew不超过设计预期。设置针对时钟树的DRC可采用set_clock_tree_options-clock{my_clocks}-max cap|-max_tran|-max_fanout<value>,如果没有-clock,即针对全部时钟域设置。

在执行时钟树综合的核心命令clock_opt-only_cts时会分两步执行,第一步称为CTS,可以生成初步的时钟网络,并符合用户设置的时钟树DRC要求;第二步称为CTO,进行时钟树的优化,主要优化时钟树skew的匹配,并使得时钟树延时最小,默认条件下不进行DRC的检查和优化,有可能在优化skew和延时时恶化了时钟树的DRC。为了避免这种情况的发生,可以设置set_appvar cto_enable drc_fixing true,这样在CTO时依然进行DRC的检查和优化,但同时要注意这类的优化并非没有代价,有可能带来skew匹配结果的恶化以及时钟树单元的增多。

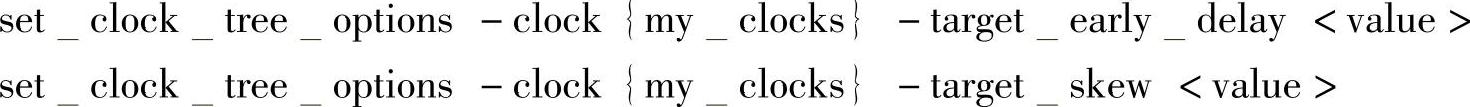

2.设置时钟树综合优化目标

如上文所述,在clock_opt-onlycts的第二步过程中会对skew和时钟树延时进行优化,在默认条件下ICC会将两者的目标都设置为0ns,这在某些设计中并非必要,反而会导致时钟树中的单元数量过多,甚至引起congestion的违例而需要重新布局。改变默认情况的方式为

同样地,如果没有-clock设置就会对所有时钟树生效。

如果需要对不同的scenario分别设置期望的skew,需要用set_clock_tree_op-timization_options-corner_target_skew来进行设置。

3.设置时钟树单元

时钟树综合与优化需要buffer单元与反相器单元,默认情况下ICC会使用tar-get_library中的所有单元进行时钟树综合,通常一个库里面不是所有的buffer与反相器都是上升/下降时间对称的,因此会引入不必要的skew,为了避免这种情况的发生,我们需要为ICC指定一组或者多组专门的buffer单元与反相器单元用于时钟树综合与优化,设置方法如下:

如果设计相对简单,可以只设置第一条,即cell_list_1,可以把所有可用于时钟树的单元都放入cell_list_1,ICC时钟树综合与优化过程中就只会使用cell_list_1中的单元。

如果设计有一定的复杂度,推荐使用全部3条设置,可以将一小部分驱动能力较大的单元放在cell_list_1中,这部分单元只会在CTS时使用;将所有驱动能力的单元放在cell_list_2中,这样在CTO的过程中ICC可以有较大的自由度来进行优化;将一些特殊类的单元如delay cell放置在cell_list_3中,专门用于hold修复。完整的设置可以避免ICC综合优化时使用设计人员不愿意看到的单元类型,实现更好的设计结果。

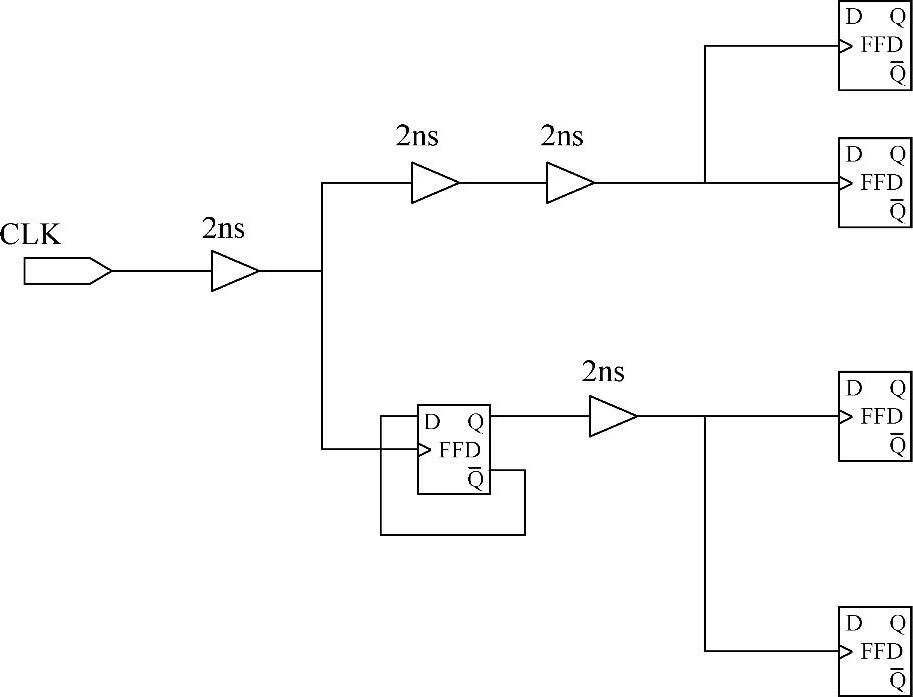

4.时钟树skew设置

在默认条件下,ICC会将同一个master_clock下的时钟树做skew匹配,如果设计中master_clock与generate_clock之间没有数据交互路径,或者相互之间已经按照异步时钟的方式处理了时钟域之间的数据交互路径,则可以将generate_clock设置为exclude_pins,这样两个时钟树会进行单独的skew匹配,降低了skew匹配的难度,减小了所需的时钟树单元数量,如图7.4所示。

如果要将图7.4中分频后的时钟与主时钟分割开来,可使用命令set_clock_tree_exceptions-exclude_pins[get_pins DIV_FF/CLK]。

图7.4 两个时钟树进行单独的skew匹配

此外,在默认条件下,ICC不会对不同master_clock之间的数据路径做skew匹配,因为在大多数情况下,两个时钟源不同就应当在设计中采用异步时钟信号处理,无须做skew匹配。然后如果设计中两组时钟虽然定义成了不同的clock,但其实有相同的来源,相互之间视为同步时钟进行数据交互,就需要对这两组时钟做skew匹配,设置的方法为set_inter_clock_delay_options-balance_group"CLK1CLK2",随后的clock_opt命令中需要添加选项-inter_clock_balance。

如果设计中使用了宏单元,需要数字电路负责提供时钟,需要保证其db文件中正确地定义了时钟端口及其时序查找表,否则ICC不会对其进行skew匹配。如果db文件中没有正确定义端口信息,又不方便修改它,则需要采用语句set_clock_tree_exception-stop_pins[get_pins my_macro/CLK]或者set_clock_tree_ex-ception-float_pins[get_pins my_macro/CLK]。两者的区别主要是stop_pins可以视为寄存器单元的时钟端口,float_pins则只是宏单元的时钟端口,距离内部寄存器单元还有内部时钟树结构。但无论采用哪种方法都可以将该端口定义成一个明确的时钟端口,随后ICC便会对该端口进行skew匹配和延时插入。

5.对已有时钟树的处理

如果在DC综合阶段,设计人员已经加入了全部或者部分的时钟树,推荐在后端设计时将其删除,重新进行时钟树的生成,删除已有时钟树的命令为remove_clock_tree-clock_tree[all_clocks]。但如果需要保留部分的时钟树单元,可以采用set_clock_tree_exceptions-dont_touch_subtrees{preserving_clk_tree}或者set_clock_tree_exceptions-dont_size_cell{dont_size_clk_cells}。

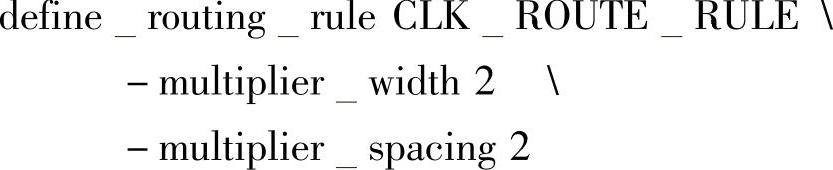

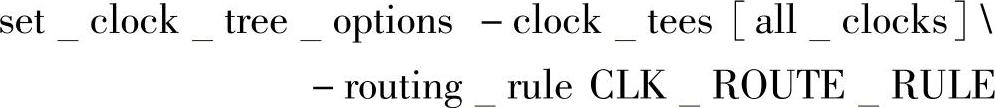

6.对时钟布线规则的定义

在ICC布线中,默认的布线规则来自于TF文件中对每一层金属的定义。由于时钟信号的特殊性,其布线规则不同于默认的布线规则,例如会采用双倍宽度、双倍间距的布线规则,使得时钟网络不容易受到信号串扰的影响,保证芯片的正常工作。定义非默认布线规则的方法为

在某些设计中还需要定义非标准的通孔规则,方法为加上选项-cuts或者-via

cuts,详细情况可参考ICC手册及具体的TF文件。定义完后还需将规则应用于具体的时钟树:

对于非默认布线规则,还可以设置shield,就是在信号线的两边再添加上保护线,用于将该信号线与其他信号线彻底隔开。如果某些时钟线频率较高或者驱动力不强,可能需要加上shield,具体的方法可以查看命令create_zrt_shield的相关介绍。

有关CMOS集成电路EDA技术的文章

时钟树综合前的时钟网络如图8.27所示,呈发射状。为了平衡寄存器到时钟端口的延时,时钟树综合通过许多专用的时钟缓冲单元来搭建平衡的网状结构。也就是基于如上原因,时钟树综合这一步骤在数字物理设计流程中,一般在布局完成后进行。具体到Encounter工具,Encounter的时钟树工具现在版本使用的有两个时钟树综合引擎,两者均有读入SDC约束的能力。......

2023-06-26

完成了上述设置后,就可以进行时钟树生成的3个核心命令。随后可以通过report_timing/report_constraint-all来检查各个scenario下的时序情况,通常而言,如果时钟树相关的设置没有大的问题,setup不会有较大的违例,但是由于之前一直将时钟网络视为零延时网络,会在初步时钟树生成后产生hold违例。......

2023-06-26

请注意CLKBUF由于单元延时较小,应用于设计中会使得面积增大,所以一般使用set-DontUse在非时钟树生成阶段加以禁用。此时可使用Vi等文本编辑工具编辑ct-stch文件的内容,使得时钟树的约束结果最优化。图8.29 generate clock spec窗口在返回到synthesize clock tree窗口之后,单击“OK”按钮开始时钟树综合并完成时钟树相关布线。时钟树综合完成后,进行CTS后时序优化。图8.30 generate clock spec窗口进行完此步骤后可使用Browser clock tree等工具观察时钟树结构并进行优化。至此时钟树综合相关内容告一段落。......

2023-06-26

特殊布线分为电源布线以及时钟树布线。根据EDI的数字流程,电源布线在布图规划的时候进行;而时钟树布线在时钟树生成之后进行,先于时钟树生成后的时序优化以及信号线的布线。综上所述,顶层金属更适合用作电源布线,电源线的宽度需要通过设计评估最大工作电流、最大瞬态电流以及电流密度计算而得。......

2023-06-26

表9.4-2 DHCP默认的通信参数2.DNS设定FS-0iD的DNS设定操作步骤如下:1)设定CNC参数PRM14880.5=1,生效CNC的DNS客户机功能,并将计算机设定为DNS服务器。图9.4-7 DHCP连接成功显示a)第一页 b)第二页在该显示页上,可进行主机名的定义。如CNC和计算机的连接失败,CNC将显示图9.4-8所示的DHCP连接出错页面,并显示“DHCP ERROR”信息。......

2023-06-25

电气原理图是转换PCB图的依据,设计好原理图非常重要。元件的属性包括序号、封装形式、引脚号定义等,下面对图7-5的元件属性进行编辑。图7-5 元件位置调整后的结果图7-6 元件属性编辑对话框在图框里设置元件各种属性:1)Lib Ref:元件库的型号,不允许修改。3)Designator:元件序号,写入“U1”。6)Part:功能块序号,此项用于多个相同功能块,而对其元件无效。设置结束后,单击“OK”按钮即可。3)电解电容:C3、22μF、RB.2/.4。......

2023-06-25

1)返回Workbench工作界面,右键单击B2,如图5.3-7a操作,将先前设好的稳态前处理文件导进来,因为流体域的定常和非定常设置仅有部分不同,这里仅需讲定常设置稍作修改即可。图5.3-7 导入流体域2)流体域分析类型设置。双向耦合时,流体域设置与定常不同之处主要为耦合面处边界条件的设置,这里主要指旋转域,即叶轮段。导流冒处的设置在进口段完成,其过程与以上完全相同。图5.3-8 设置流体域时间步长图5.3-9 设置网格变形6)求解控制。......

2023-06-26

AutoCAD绘图使用的默认线型为连续线型Continuous,其他线型则应加载后才能使用。用户可根据自己的需要为图层设置不同的线型。选择“CENTER”线型,然后,单击按钮,完成图层线型设置。图1-8对话框在作图过程中临时设置当前线型有以下三种方式:● 在工具栏的下拉列表框中选择已加载的线型,或选择选项,调出对话框,如图1-9所示,以加载所需线型。图1-9对话框下面对对话框加以必要的说明::确定在线型列表中显示哪些线型。只能删除未使用的线型。......

2023-06-21

相关推荐