在以学习者为中心的设计过程中,需要确保为学习者提供有吸引力的移动学习体验,从而吸引他们持续接受教育。教学设计、技术设计和可用性设计的最终目标是促进并保持学习者的高满意度。为了确保学习者的高满意度,移动学习设计的综合模型需要考虑地点、技术以及文化。......

2023-11-30

状态机是时序逻辑与组合逻辑完美结合的典型实例。前面章节我们介绍了DC的基础知识和基本用法,本节将通过基于第5章中状态机的交通灯实例来介绍DC是如何完成一个设计的综合的。

我们在进行综合前必须有的两个文件。一个是目标库文件,通常是.db格式的二进制文件。另外一个是交通灯的RTL源文件,也就是5.2.1节中的例5.12。

首先创建用来做综合的文件夹,取名为lab。在文件夹中添加RTL源文件,DC运行脚本,约束文件和目标库文件,当然还有DC自启动文件.synopsys_dc.setup,如图6.38所示。

图6.38 综合文件夹lab

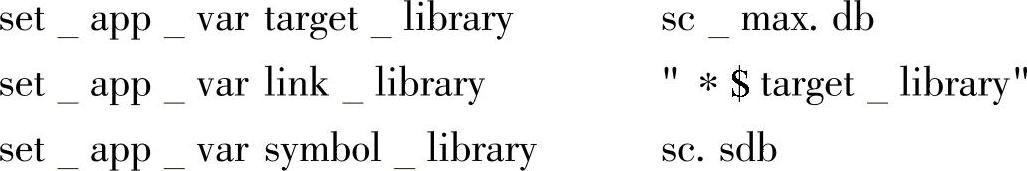

在启动脚本.synopsys_dc.setup里对各种库进行了设置,在终端运行DC即会执行脚本中的内容。该脚本设置目标库,链接库和符号库,如例6.23所示。

例6.23

在操作系统终端启动的DC后,就可以在DC终端用Tcl命令对综合器进行操作。在这里我们将这些命令都集中在DC运行脚本dc.tcl中,我们只需在DC终端用source命令启动这个脚本就可以完成全部综合任务,该脚本如例6.24所示。

例6.24

从这个脚本可以看出,首先用read_verilog读入RTL文件,并且设置顶层文件,再链接。命令source MY_DESIGN.con启动了约束文件。然后是compile_ultra命令进行综合编译。report_timing>MY_DESIGN.tim命令是将时序报告新建在一个叫作MY_DESIGN.tim的文件里。最后是将编译生成的网表以ddc格式的形式保存下来取名为MY_DESIGN.ddc。其中的约束文件MY_DESIGN.con如例6.25所示。

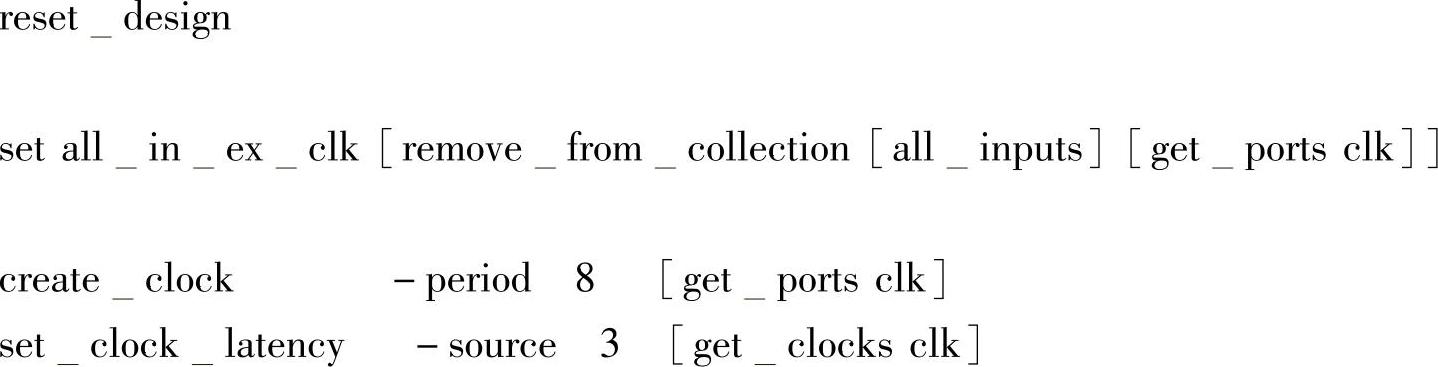

例6.25

首先该脚本用reset_design命令重置设计,也就是将DC memory中先前的约束清除。接着设置了一个名为all_in_ex_clk的变量用来表示除了时钟以外的所有输入端口。后面几条命令是创建时钟及对时钟的约束。接着用60%的时间预算约束输入输出端口逻辑的延迟。最后是设置模块的驱动部件和所带的负载。

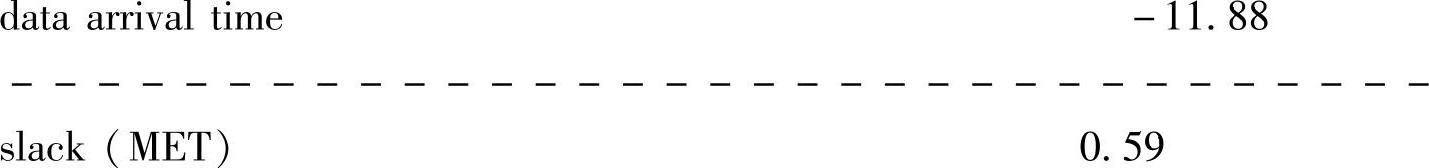

运行完这两个脚本后,得到的时序报告如例6.26所示。表头含有报告类型,默认选项信息、设计名称、工具版本号和时间信息。下方是工作环境、目标库名和线负载模型。接着下面是报告出的关键路径起点和终点、路径组和时序路径的类型。再下边就是时序报告的主体,分为三个竖栏,第一个竖栏里是时序路径上的各个节点,第二竖栏是前一个节点到本节点的时间差,最后一栏是从起点到本节点的时间累积总和。报告又分为上下两张表,上表是信号通过该时序路径到达终点的时间情况,下表是被约束时钟信号情况下,信号要求应该到达终点的时间情况。要求到达时间减去实际到达时间得到的结果为正数,则说明该时序路径没有违例,符合时序要求。否则,则表示该时序路径违例,不符合时序要求。

例6.26

完成综合后会得到一个.ddc格式的文件,如图6.39所示。这就是交通灯的门级网表,可将该文件交付给后端部门进行下一步的设计工作,综合流程到此结束。

图6.39 门级网表文件

有关CMOS集成电路EDA技术的文章

在以学习者为中心的设计过程中,需要确保为学习者提供有吸引力的移动学习体验,从而吸引他们持续接受教育。教学设计、技术设计和可用性设计的最终目标是促进并保持学习者的高满意度。为了确保学习者的高满意度,移动学习设计的综合模型需要考虑地点、技术以及文化。......

2023-11-30

(一)制定实施方案学校依据市区级综合素质评价标准制定学校校本化方案是实施综合素质评价的基础。美习拍卖会学生的习惯养成一直以来都受到学校的高度重视,为了让孩子进入梁才后能尽快养成良好的习惯,并且能长久的坚持下去,学校为孩子设计了美习卡,并以美习币的形式对孩子的表现进行评价。(四)开展师生培训梁才学校采用落实到人环环紧扣的方法扎实推进学生综合素质评价。......

2023-07-18

原型结构的综合延伸设计,是更为贴近实现服装原创设计作品的结构技术性运用。1.衣身原型结构的综合延伸设计衣身原型结构的综合延伸设计是对衣身结构各方面多种因素的考虑,其结构的设计构成关系已初具服装的丰富性和完整性。......

2023-06-24

枯水流量的时段,应根据工程设计要求和设计流域的径流特性确定。必须指出,在枯水径流进行频率计算中,当遇到Cs<2Cv或Cs<0的情况时,应特别慎重。图G1.3负偏频率曲线此外,当枯水流量经验频率曲线的范围能够满足推求设计值的需要时,也可以采用经验频率曲线推求设计枯水流量。Qp==×4.96=3.992.设计枯水位频率计算有时生产实际需要推求设计枯水位。当设计断面附近有较长的水位观测资料时,可直接对历年枯水位进行频率计算。......

2023-06-21

调查结果同时显示,综合管廊运维管理阶段的工作人员在调查中反馈BIM技术的可视化和数据集成功能有利于提高管廊运维效率,降低运维风险,减少运维成本。依托于BIM建立的可视化运维管理平台,实现综合管廊运维管理的精细化,相对于目前市场现有的综合管廊管理平台,更加适用于综合管廊的运维管理。......

2023-08-29

(一)马什的一般传播模式马什的一般传播教学设计模式把教学设计分为以下四个阶段:第一个阶段是基本设计阶段。第四个阶段教学设计者需要考虑学习者所期望的反应类型。马什认为使用音乐、彩色以及视觉组合,可以获得不同的效果,但这些因素不应增加信号的复杂性。(二)莱特和皮亚特的文本组织模式莱特和皮亚特认为,教材页面上内容的组织方式会影响学习,他们以此为基础构建了教学设计模式。......

2023-08-01

清除浮动可以理解为打破横向排列。图8.10例8.6 的运行结果_未清除浮动前说明按照之前所述的浮动的规则,secondDiv 上浮到firstDiv 右侧。假设出于某种需要,我们希望secondDiv 仍然出现在firstDiv 的下方,就像firstDiv没有设置浮动,仅为secondDiv 设置向左浮动那样。图8.11例8.7 的运行结果_清除左侧浮动说明在secondDiv 上设置了清除左侧浮动,也就是说它的左侧不能有浮动元素,这样导致它自己换行显示以满足这一规则。以下代码演示了清除右侧浮动的场景。......

2023-10-19

基于聚类分析的分类与后面几节所述的有监督学习分类的不同之处在于,它要划分的类是未知的,也就是说事先并不知晓要把目标分为哪几个具体的类别。为了达到全局最优,基于划分的聚类会要求穷举所有可能的划分。它也基于标准的统计数字自动决定聚类的数目,考虑“噪声”数据和孤立点,从而产生健壮的聚类方法。高维数据聚类分析是聚类分析中一个非常活跃的领域,同时也是一个具有挑战性的工作。......

2023-06-28

相关推荐