如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。图6.27 多时钟同步设计CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。图6.30 多时钟同步输出约束DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。......

2023-06-26

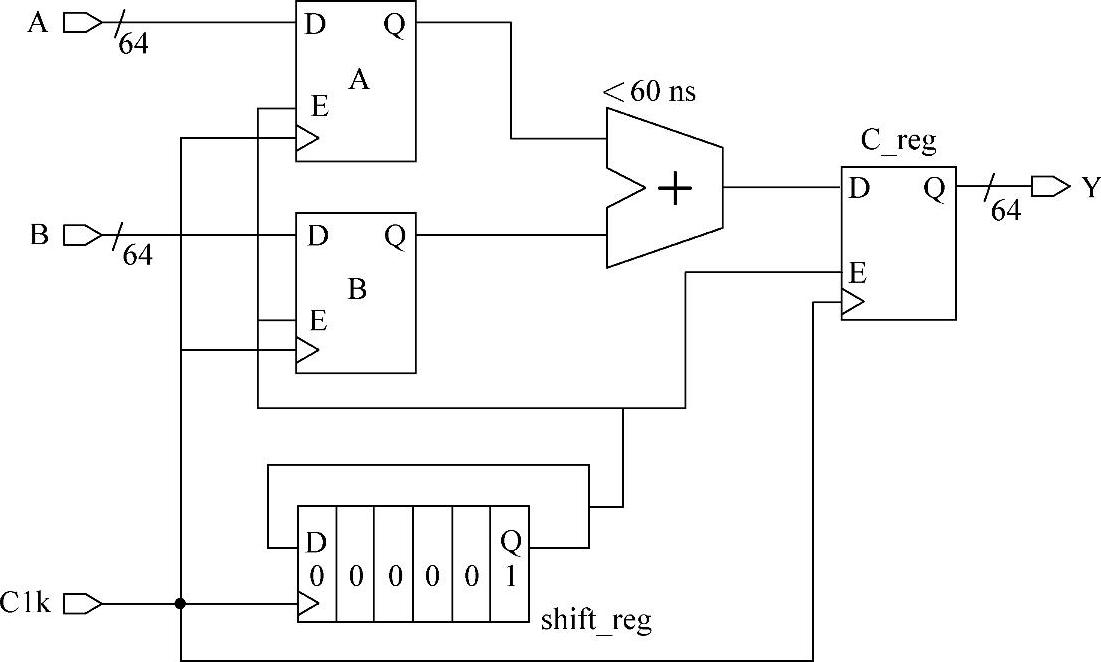

前面的设计约束中,我们默认了信号变化要在一个时钟周期内完成,并且达到稳定值,以满足寄存器建立时间和保持时间的要求。但是在有些设计中,某些特殊的路径并不能或者不需要一个时钟周期内完成。如图6.34所示,时钟周期定义为10ns,按设计规格,加法器的延迟为6个时钟周期。那么该如何约束电路呢?

图6.34 多时钟电路设计

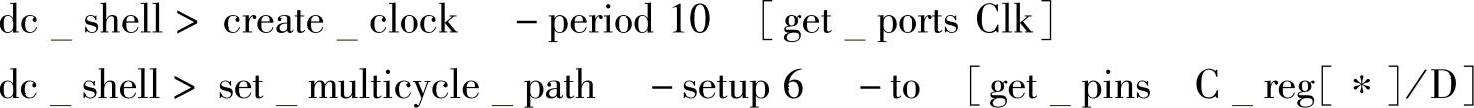

如图6.35所示,DC将会仅仅在第6个时钟上升沿,即60ns处,建立时序分析。这里允许加法器最大延迟是:60-Tsetup。

图6.35 多时钟建立时间约束

默认的保持时间分析是在建立时间分析的前一周期。如果照这样分析,DC会在50ns处分析电路有无违反保持要求,即要求加法器的最小延迟为:50+Thold。

要用DC综合出一条同时满足上述两个约束的路径会极大增加电路的复杂度。在时间为60ns的时刻,引起寄存器Creg的D引脚变化是在时钟Clk在0ns时刻的触发沿。所以应该在0ns处做保持时间检查,如图6.36所示。

图6.36 多时钟保持时间约束

保持时间将会提早5个时钟周期,所以加法器d允许延迟为Thold<加法器允许的延迟<60-Tsetup。

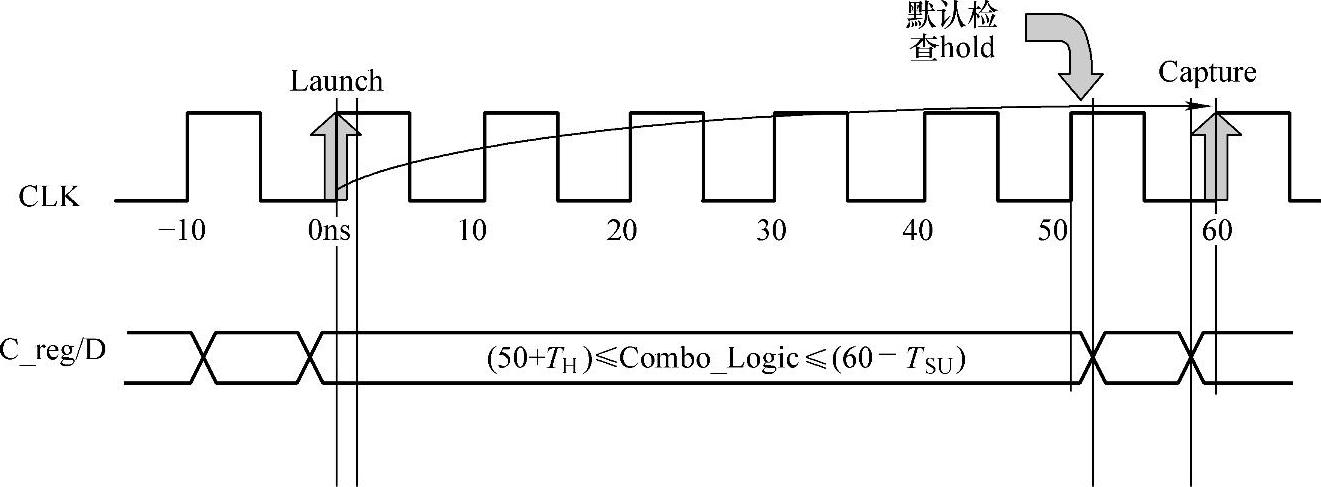

图6.37是另一个多时钟周期的例子,图中乘法器运算为2个时钟周期,加法器运算为1个时钟周期,其约束为

图6.37 多时钟电路设计

有关CMOS集成电路EDA技术的文章

如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。图6.27 多时钟同步设计CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。图6.30 多时钟同步输出约束DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。......

2023-06-26

MCS-51的时序定时单位共有4个,从小到大依次是节拍、状态、机器周期和指令周期。图2-10外部方式时钟电路图由图2-11可知,ALE引脚上出现的信号是周期性的,在每个机器周期内出现两次高电平。单周期指令的执行始于S1P2,这时操作码被锁存到指令寄存器内。图2-11给出了单字节双周期指令的时序,两个机器周期内进行4次读操作码操作。图2-11MCS-51的取指/执行时序图......

2023-11-17

接下来我们对这4种路径的时序约束逐一进行介绍。图6.14 寄存器间的时序路径图6.15 理想时钟与实际时钟uncertainty描述的是时钟跳变时间的不确定性,这种不确定性来源于3个方面,分别是jitter、skew和margin。latency指的是时钟沿到来的延迟。latency分为两种,一种是时钟源到被综合模块时钟端口之间的延迟,叫作Source Latency。图6.16 Clock Latency时钟的跳变沿在实际电路中并不是瞬时变化的,而是有一定的坡度,transition描述的就是这个坡度的持续时间,如下例所示。......

2023-06-26

为了提升防御窃听攻击能力并保障CIS信息安全,人们提出了一种基于可实现业务流切片与并行计算的MFVC的安全策略。采用基于MFVC的安全策略能有效地排除这一安全隐患,图8-4和图8-4分别展示了这一安全策略的过程与优势。因此,这种基于MFVC的安全策略可以同时增加安全性与频谱效率。图8-4一般传输模式与安全策略的对比在所提出的安全策略中,由于CIS的传输模式变成了并行传输,所以计算EP值的公式不再适用于对业务被窃听概率的评估。......

2023-06-19

主要的SDC语句包括以下几个。该命令在DC综合时的用法往往与ICC的不同,因此需要根据实际情况修改。3)set_clock_latency/set_clock_unertainty等,均用来对时钟进行描述。4)set_input_delay/set_output_delay,用来对输入电路和输出电路进行时序约束。在电路中,大多数电路处于寄存器与寄存器之间,可以由时钟周期来约束。但与芯片IO相连的组合逻辑电路不属于任何一条时钟电路能够约束的范围,因此需要用set_input_delay和set_output_delay来约束。读入SDC后需要进行时序约束检查,通常需要运行6种检查命令,分别如下。......

2023-06-26

1.终端约束令t0、tf分别为编队形成段的初始时刻与末端时刻,为保证从弹在tf时刻到达指定编队位置,需对从弹在tf时刻的相对位置x、y、z进行约束:式中,x*,y*,z*——从弹在领弹弹道坐标系下的期望编队位置。......

2023-08-02

对于数据量比较小或者提供的数据影响因素比较单一的预测,可以采用简单的时序模型预测法,比如线性回归、自回归、自回归滑动平均混合等。对实际中发生的平稳时间序列做恰当的描述,往往能够得到自回归、滑动平均或混合的模型,其阶数通常不超过二阶。......

2023-06-28

相关推荐