如图6.34所示,时钟周期定义为10ns,按设计规格,加法器的延迟为6个时钟周期。图6.34 多时钟电路设计如图6.35所示,DC将会仅仅在第6个时钟上升沿,即60ns处,建立时序分析。图6.36 多时钟保持时间约束保持时间将会提早5个时钟周期,所以加法器d允许延迟为Thold<加法器允许的延迟<60-Tsetup。图6.37是另一个多时钟周期的例子,图中乘法器运算为2个时钟周期,加法器运算为1个时钟周期,其约束为图6.37 多时钟电路设计......

2023-06-26

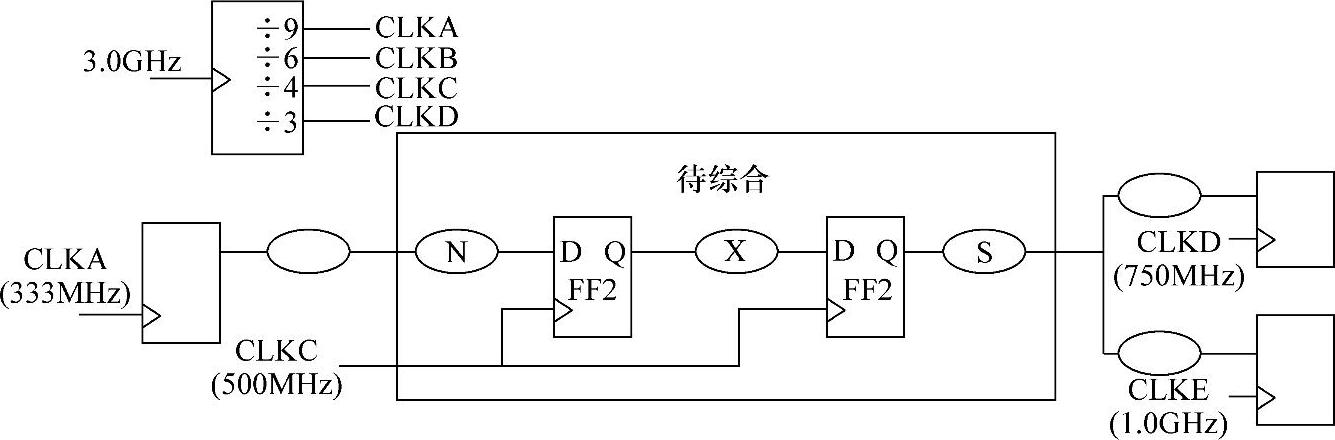

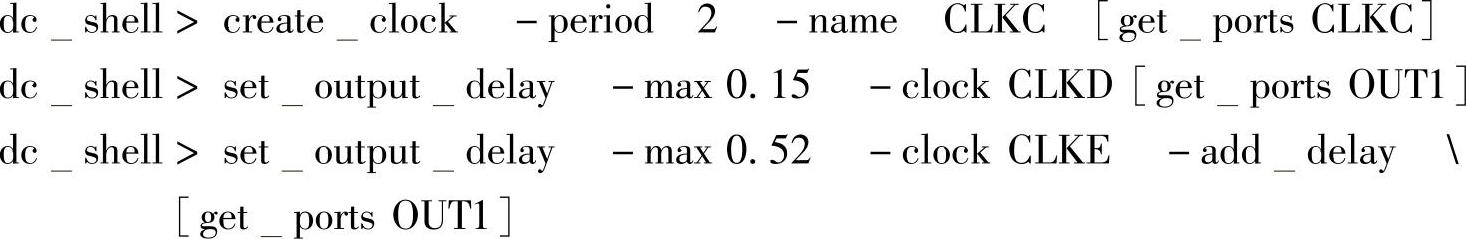

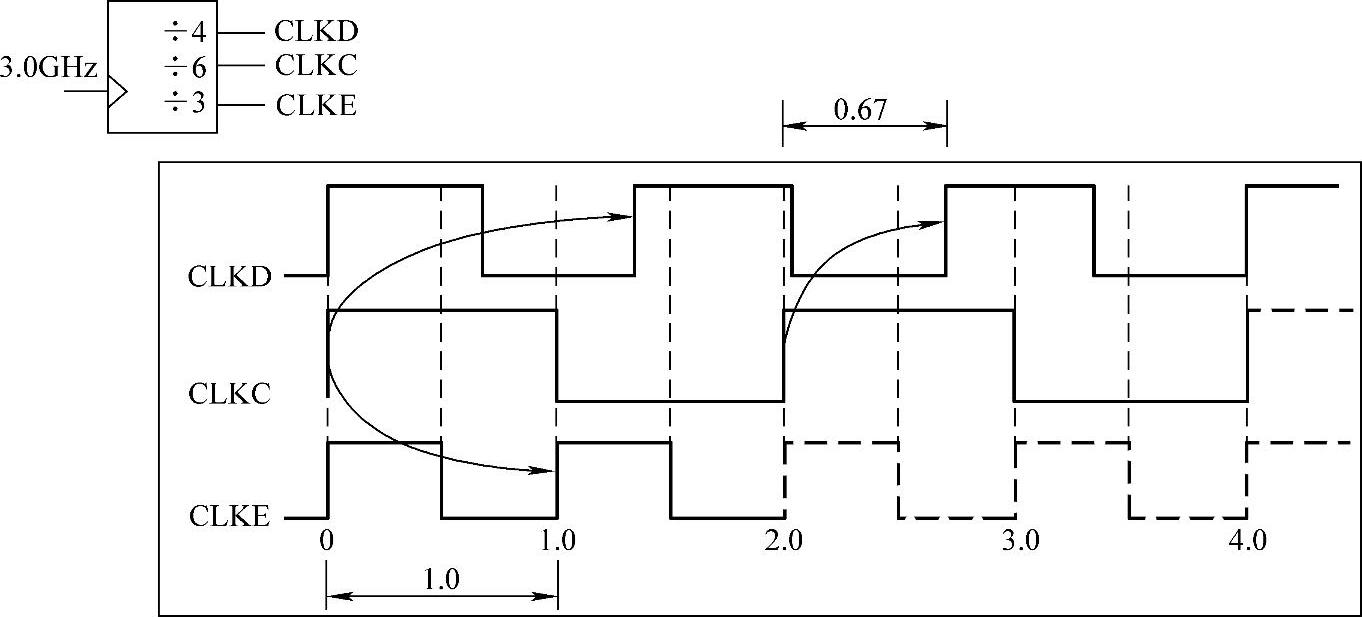

如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。但在被综合的模块中只有CLKC时钟驱动模块内的寄存器,其他的时钟都没有对应的端口。因此,它们不驱动被综合模块的任何寄存器,它们主要用于为输入/输出端口做约束,可能会出现一个端口有多个约束的情况。那么如何设置多时钟同步约束呢?

图6.27 多时钟同步设计

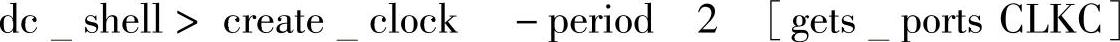

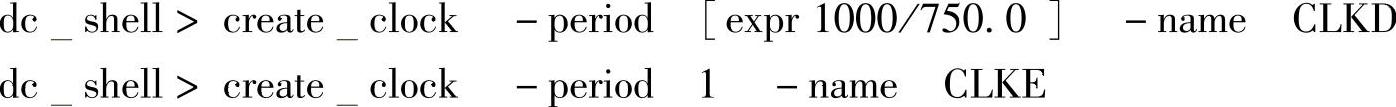

CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:

由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。虚拟时钟不驱动任何寄存器,它主要用于说明相对于时钟的I/O端口延迟。DC将根据这些约束,决定设计中最严格的约束,如图6.28所示。

图6.28 多时钟同步输入约束

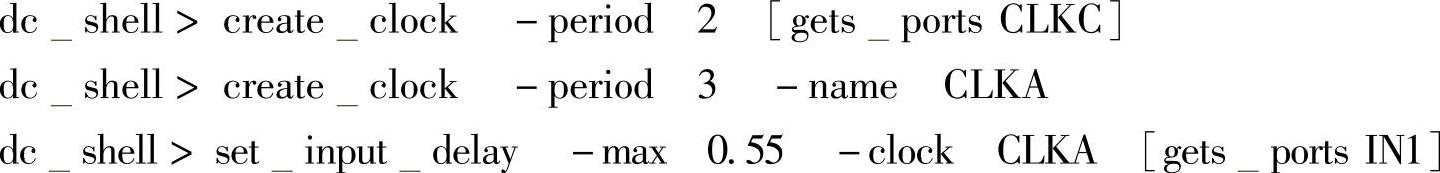

进行上述约束后,DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。如下图6.29所示,逻辑N必须满足:tN<2-0.55-tsetup和tN<1-0.55-tsetup两个不等式中最严格的情况,即:tN<1-0.55-tsetup。

图6.29 多时钟同步时钟

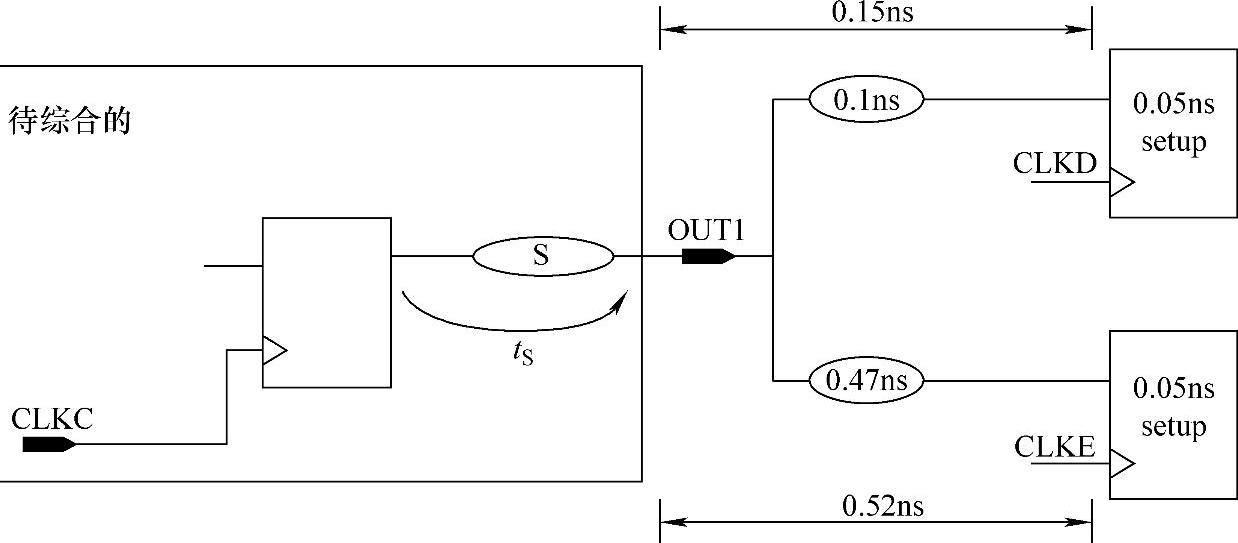

对于输出电路,我们用同样的方法定义虚拟时钟和施加约束。如图6.30所示,其中-adddelay选项的意思是输出端口OUT1有两个约束。如果不加该选项,第二个set_output_delay将覆盖第一个set_output_delay命令。

图6.30 多时钟同步输出约束

DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。如图6.31所示,逻辑S必须满足:tS<1-0.52和tS<0.67-0.15这两个不等式中最严格的情况,即:tS<0.48。

图6.31 多时钟同步时钟

有关CMOS集成电路EDA技术的文章

如图6.34所示,时钟周期定义为10ns,按设计规格,加法器的延迟为6个时钟周期。图6.34 多时钟电路设计如图6.35所示,DC将会仅仅在第6个时钟上升沿,即60ns处,建立时序分析。图6.36 多时钟保持时间约束保持时间将会提早5个时钟周期,所以加法器d允许延迟为Thold<加法器允许的延迟<60-Tsetup。图6.37是另一个多时钟周期的例子,图中乘法器运算为2个时钟周期,加法器运算为1个时钟周期,其约束为图6.37 多时钟电路设计......

2023-06-26

但为了保证电路的每一条时序路径,特别是输入/输出路径延迟约束的精确性,我们还应该提供设计的环境属性,如图6.23所示。图6.23 环境约束每一个逻辑器件的延迟都与这个器件的输出负载和输入转换时间相关,其输出转换时间也与这个器件的输出负载和输入转换时间相关。我们可以用setload指定外部电容负载为一常数值,如图6.24所示。图6.25 指定实际器件负载图6.26 指定驱动器件如上文所述,在实际设计中,由于电路比较大,需要对设计进行划分。......

2023-06-26

接下来我们对这4种路径的时序约束逐一进行介绍。图6.14 寄存器间的时序路径图6.15 理想时钟与实际时钟uncertainty描述的是时钟跳变时间的不确定性,这种不确定性来源于3个方面,分别是jitter、skew和margin。latency指的是时钟沿到来的延迟。latency分为两种,一种是时钟源到被综合模块时钟端口之间的延迟,叫作Source Latency。图6.16 Clock Latency时钟的跳变沿在实际电路中并不是瞬时变化的,而是有一定的坡度,transition描述的就是这个坡度的持续时间,如下例所示。......

2023-06-26

数字网络的同步性能对网络的工作性能至关重要,SDH对网络同步提出了更高的要求。SDH采用主从同步方式。基准定时源采用精度和稳定性好的钯原子钟,可靠的传送利用SDH帧结构中的同步状态字节和备份路由。这些不同的网络单元在SDH网中的地位和应用有很大差别,因而其同步配置和时钟要求也不同。......

2023-06-27

多因素变量配方是指一个配方中有两个或两个以上助剂的加入量影响制品性能的配方。目前常用的多因素变量设计法主要有正交设计法和中心复合试验法,本书重点介绍正交设计法。(一)正交设计法正交设计法是一种应用数理统计原理进行科学地安排与分析多因素变量的一种试验方法。[例二]PVC复合板配方正交设计本配方的组分为:聚氯乙烯、邻苯二甲酸二辛酯、三碱式硫酸铅、石蜡、硬脂酸、氯化聚乙烯及赤泥等。......

2023-06-26

1.终端约束令t0、tf分别为编队形成段的初始时刻与末端时刻,为保证从弹在tf时刻到达指定编队位置,需对从弹在tf时刻的相对位置x、y、z进行约束:式中,x*,y*,z*——从弹在领弹弹道坐标系下的期望编队位置。......

2023-08-02

经分析,采用多工位级进模进行冲压较为合理,以中间的腰圆孔为冲压时的精定距。图7-30 端罩图7-31 排样图3.模具结构设计图7-32所示为端罩多工位级进模的结构。......

2023-06-26

经分析,决定采用多工位级进模生产。图7-184 排样图3.模具结构设计图7-185所示为耳环集成式多工位级进模结构。它不同于常规的多工位级进模结构,这是在一套大模架上装有四副(Ⅰ~Ⅳ)独立的子模具。各子模具由圆柱销定位并由螺钉分别固定在大模架上。刃口有效高度小于10mm,冲压时凸模进入凹模适当多一些,正常情况下使凹模内的料不超过三片,这样对凹模寿命有利。......

2023-06-26

相关推荐