如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。图6.27 多时钟同步设计CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。图6.30 多时钟同步输出约束DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。......

2023-06-26

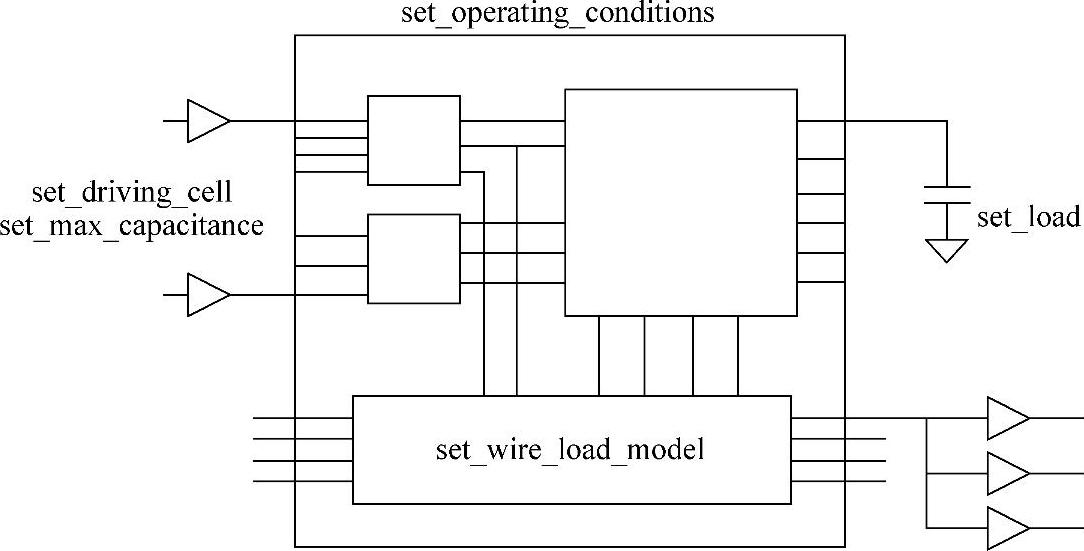

上文中我们用createclock、setinputdelay,setoutputdelay等命令来设置电路约束。但为了保证电路的每一条时序路径,特别是输入/输出路径延迟约束的精确性,我们还应该提供设计的环境属性,如图6.23所示。

图6.23 环境约束

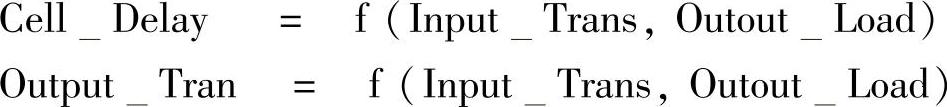

每一个逻辑器件的延迟都与这个器件的输出负载和输入转换时间相关,其输出转换时间也与这个器件的输出负载和输入转换时间相关。即:

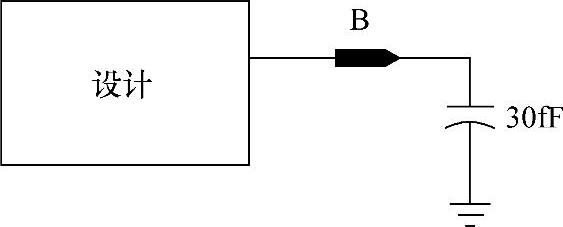

因此,为了精确地计算输出电路的时间,DC需要知道输出器件所驱动的总电容负载。在默认情况下,DC会认为输出端口外部电容负载为0。我们可以用setload指定外部电容负载为一常数值,如图6.24所示。也可以用loadof命令指定工艺库中某一器件的引脚为负载,如图6.25所示。

图6.24 指定常数负载

对于输入,为了精确计算输入电路的时间,DC需要知道到达输入端口的转换时间。在DC中用setdrivingcell命令明确说明输入端口是由一个真实的外部单元驱动。默认情况下,DC假设输入端口上外部信号对应的转换时间为0。但是如果我们用setdrivingcell命令在输入端加上了一个驱动,DC将会计算实际的转换时间,如图6.26所示。

图6.25 指定实际器件负载

图6.26 指定驱动器件

如上文所述,在实际设计中,由于电路比较大,需要对设计进行划分。在一个设计团队中,每一个设计者负责一个或几个模块。设计者往往不知道每个输入端口的驱动和输出端口的负载,因此设计者要对输入输出端口预测,预测需要遵守以下几个准则:

1)保守起见,假设输入端口由驱动能力很弱的单元驱动;

2)限制每一个输入端口的输入负载;

3)估算输出端口驱动的模块数目。

第1条和第3条上文已经介绍,对于第2条可以通过setmaxcapacitance命令限制附加在输入端口上的电容负载值。

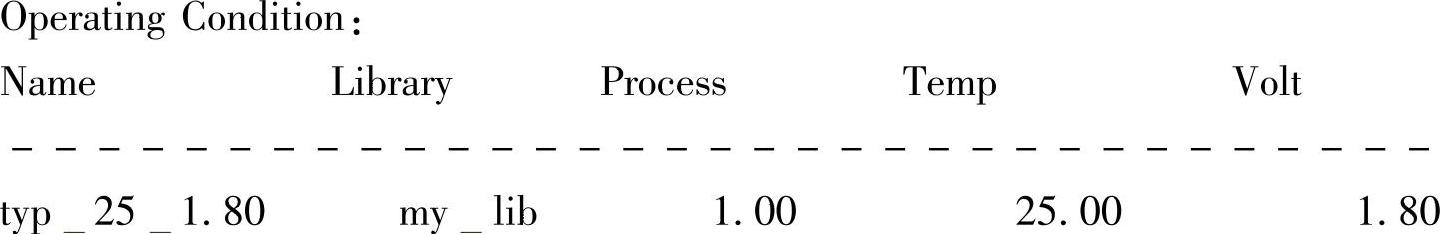

工艺库单元通常用“nominal”电压和温度来描述周围环境特性,例如:

如果电路在不同的“nominal”电压和温度的条件下工作,我们需要为设计设置条件。在半导体厂商提供的工艺库中会放入不同的工作环境,可以用setoperat-ingconditions命令把工作条件加在设计上。可以用reportlib libname命令将所有工作条件列出来,例如:

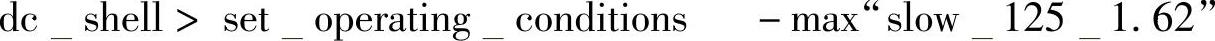

设置工作条件用下面的命令:

WLM(Wire Load Model,线负载模型)是根据连线的扇出来估算连线的RC寄生参数,一般由半导体厂商建立,用户也可以建立自己的线负载模型,例如:

设置线负载模型用下面的命令:

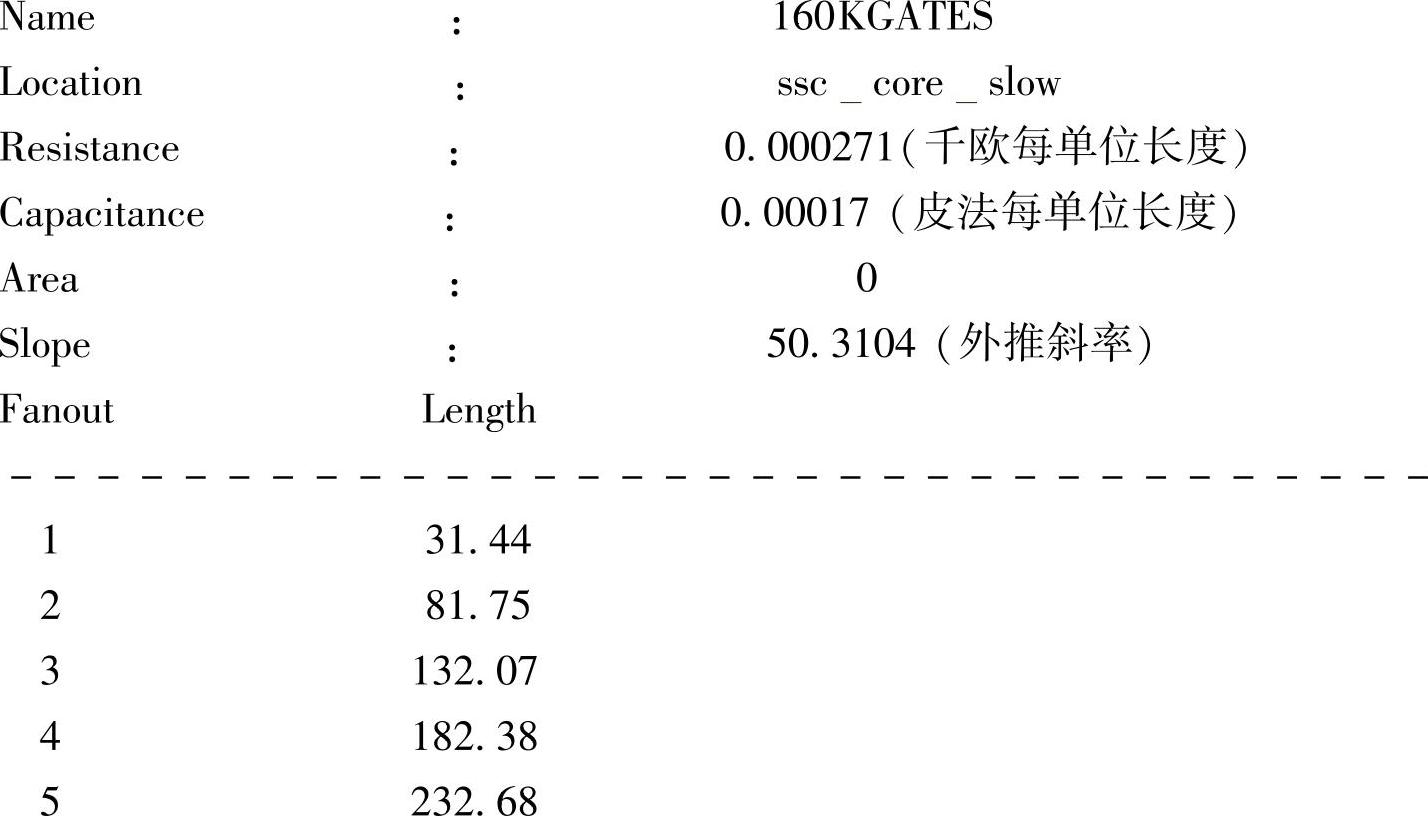

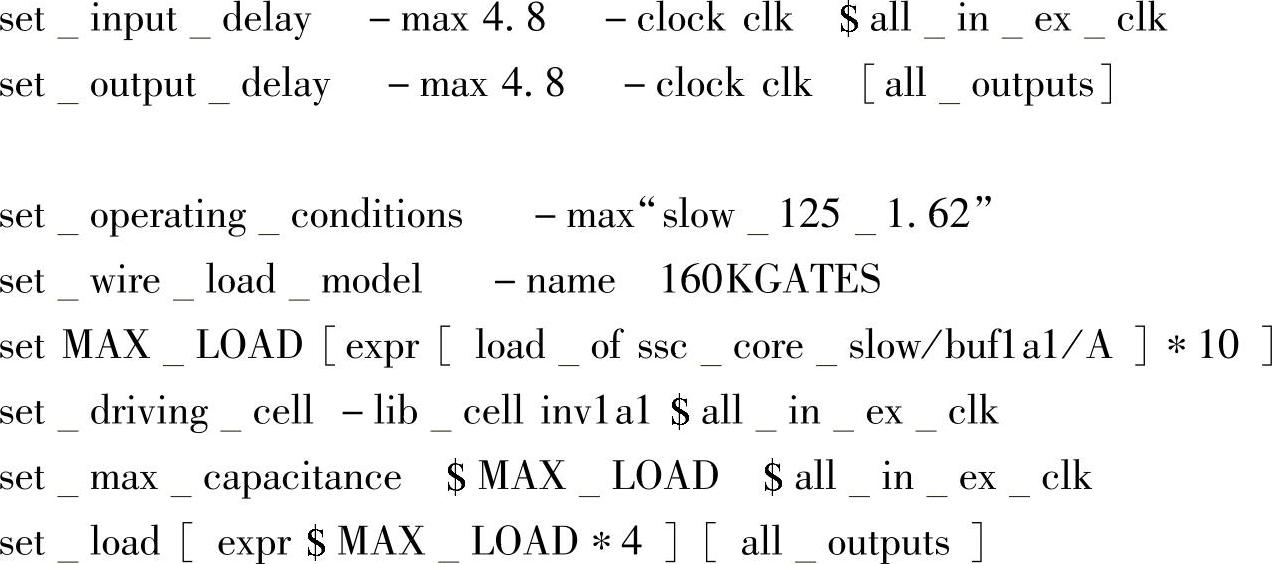

综上所述,可以将所有的设计约束建立为一个DC-Tcl脚本,在使用工具时直接用source命令执行该脚本就可以完成所有约束,如例6.22所示。

例6.22

有关CMOS集成电路EDA技术的文章

如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。图6.27 多时钟同步设计CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。图6.30 多时钟同步输出约束DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。......

2023-06-26

然而在信托受益权资产证券化交易结构中,经常采用“信托+专项资产管理计划”的双SPV交易模式,第一层SPV仅是发挥通道作用,第二层SPV采用专项资产管理计划通过证监会线条来发行证券。综上所述,对于目前我国在资产证券化中SPV设计模式的问题只有通过信托的方式才能真正实现破产隔离,使特定的资产具有独立性、排他性,有效保障资产证券化的成功运作。......

2023-07-17

固体废弃物主要包括磨屑、磨料粉尘等,液体废弃物主要是磨削液,气体废弃物主要是磨削液的烟雾、蒸汽,这些废弃物对人体和环境危害很大。在磨削加工时,含机械杂质较多的磨削液,不能用于磨削加工,必须给予净化处理才能继续使用。磨削液用水稀释后,通过加工工件、工作环境以及操作人员的手、周围空气等方式会对稀释液造成污染,所带入的微生物便开始繁殖,从而导致磨削液的腐败与劣化。......

2023-06-25

241.地方法官审判传唤案件时应遵守以下程序。经原告或被告申请,地方法官认为合适的,可以传唤任何证人出庭或提供任何文件或其他事项。法官在应任何证人的申请传召其出庭前,可要求其为审讯目的而招致的合理开支存放于法院。地方法官未依照本法第349条或第562条规定继续审判的,如其认为原告有罪,应依法宣判。......

2023-07-17

常规下承式拱桥拱肋和吊杆垂直桥面设置,大沽桥限定的1.3 m 梁高很难满足32 m 桥宽要求,因此将拱肋向内侧平移,使得人行道在拱肋外侧,拱肋间距为24 m。图2-2拱结构示意图为了使拱肋窈窕,并且满足拱的稳定问题,大沽桥单侧拱对应两排吊杆,形成三维空间结构。由于桥位处为软土地基,拱脚与钢箱梁固定,钢梁内设置系杆,形成系杆拱桥的结构方案。这种结构体系称为“敞开式四索面倾斜拱肋系杆拱桥”。......

2023-07-01

干喷湿纺喷丝板的设计与熔融纺丝喷丝板的设计有许多相似之处,因此,可以借鉴熔融纺丝喷丝板的设计经验。喷丝板设计和制作的主要参数包括导孔的形状与大小、喷丝孔的直径、长径比、喷丝孔的间距等。胀大比过大,会对纺丝工艺不利,严重时会造成纺丝细流的破裂。实际生产过程中,在固定供料量和纺丝卷绕速度的条件下,通过使用同样孔数、不同喷丝孔孔径的喷丝板来获得最佳的纺丝效果。......

2023-06-25

7.1.4.5 防渗设计1.防渗方案结合上游护坡改建,拆除原干砌石护坡,坡面整平后铺设两布一膜复合土工膜,以防止随着水库运用水位升高后,坝体浸润线升高引起坝体新的变形,导致沿坝体裂缝以及填筑接合面可能产生的集中渗漏。......

2023-06-22

相关推荐