【摘要】:如下例所示,设置了逻辑E最大延迟不超过0.4ns,逻辑G的最大延迟不超过0.2ns。图6.19 组合逻辑路径的约束另外一种情况如图6.20所示,被综合模块中没有时序逻辑器件,也没有时钟端口。为了不产生亚稳态,从FF1时钟端的上升沿,到FF4时钟端的上升沿捕获,中间信号传输限制在一个时钟周期内完成。由此可以计算出被约束逻辑Combo延迟为2ns-0.4ns-0.2ns-0.1ns=1.3ns。图6.20 组合逻辑路径的约束

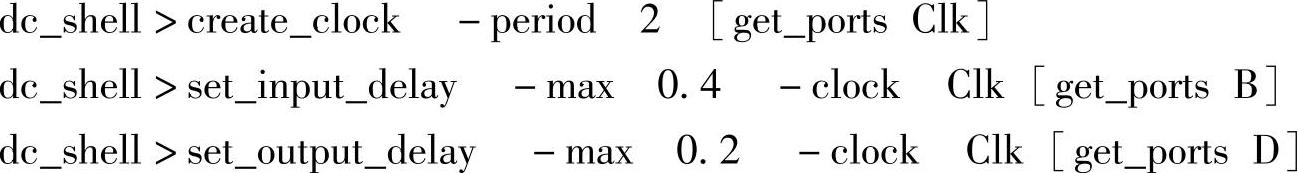

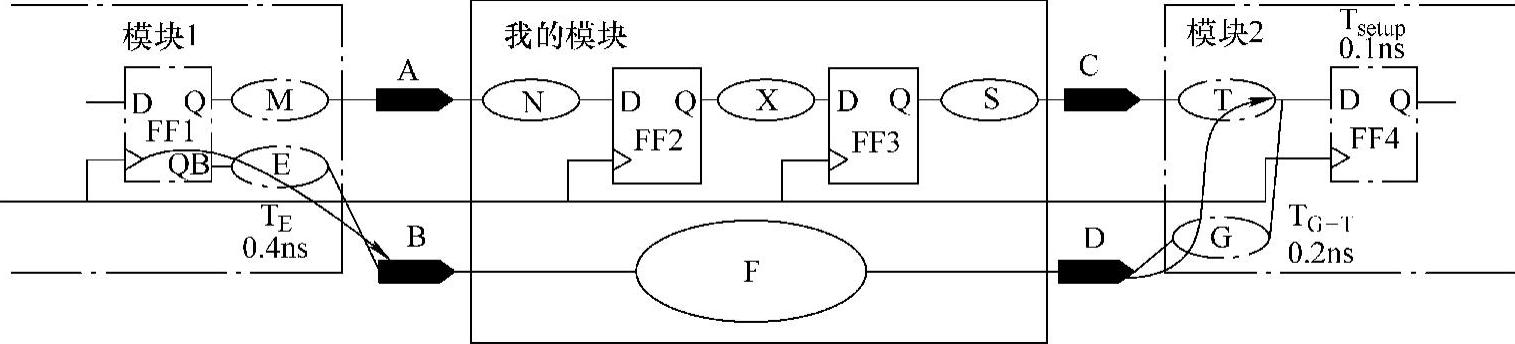

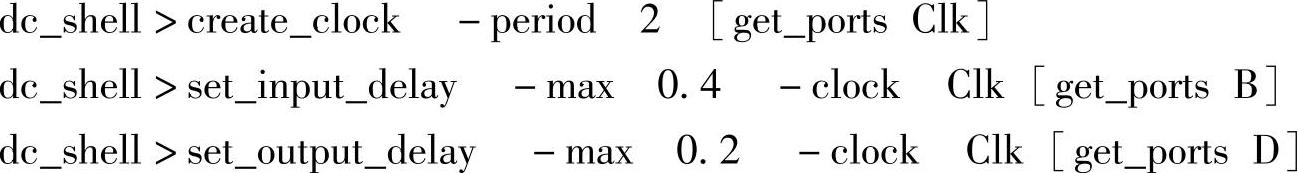

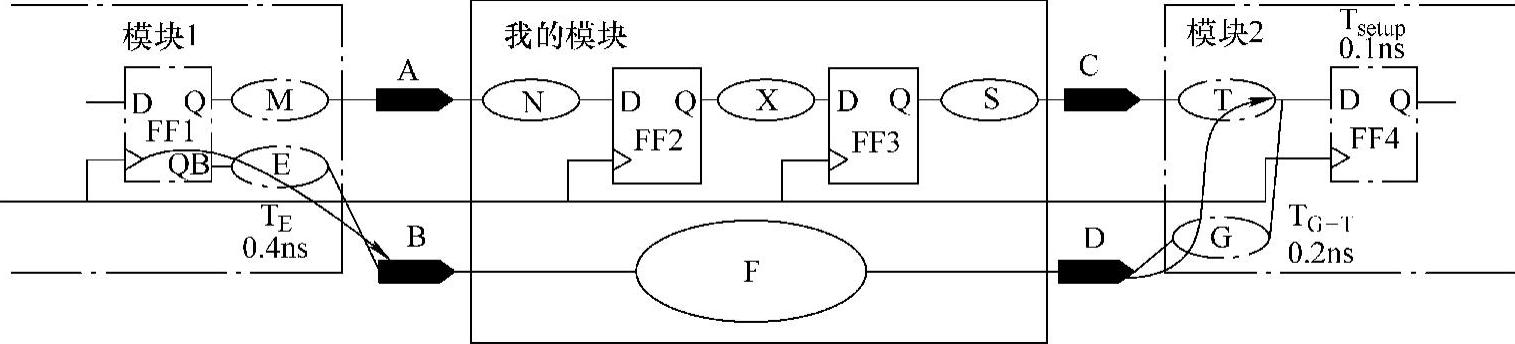

组合逻辑路径的约束有两种情况,第一种如图6.19所示,被综合模块中存在时序逻辑。要综合组合逻辑F,我们先要对前级模块中的逻辑E进行设置。其次还要对后级G逻辑进行设置。如下例所示,设置了逻辑E最大延迟不超过0.4ns,逻辑G的最大延迟不超过0.2ns。为了不产生亚稳态,从FF1时钟端的上升沿,到FF4时钟端的上升沿捕获,中间信号传输限制在一个时钟周期内完成。由此可以计算出被约束逻辑F延迟为2ns-0.4ns-0.2ns-0.1ns=1.3ns。

图6.19 组合逻辑路径的约束

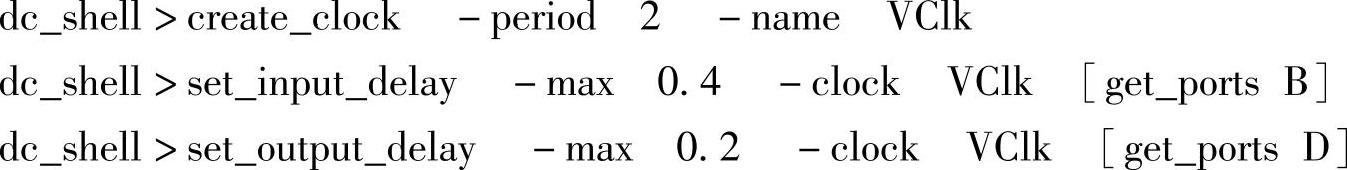

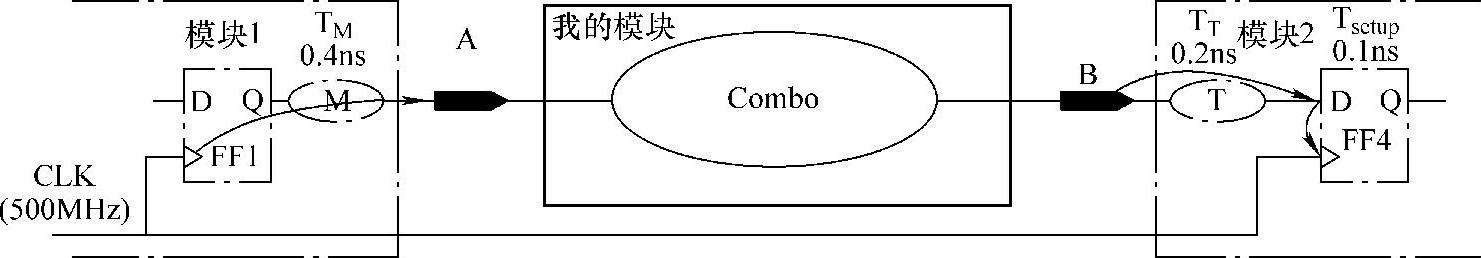

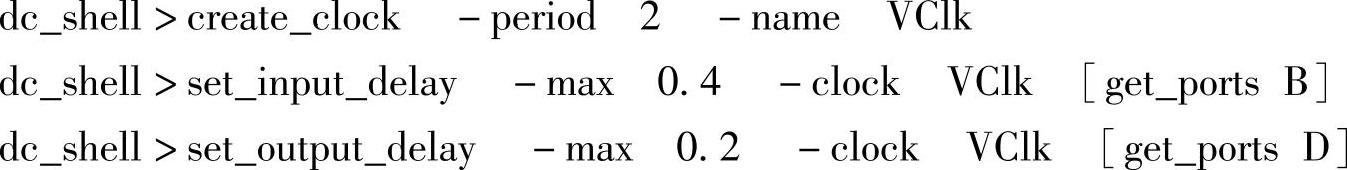

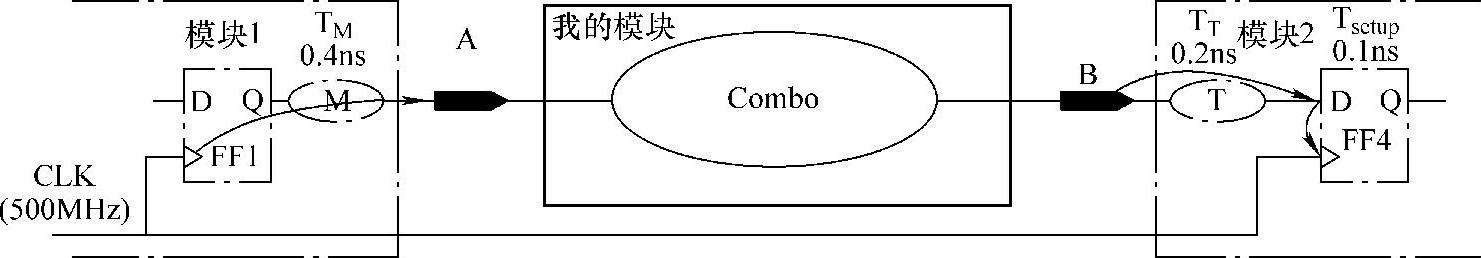

另外一种情况如图6.20所示,被综合模块中没有时序逻辑器件,也没有时钟端口。在这种情况下我们就必须设置一个虚拟时钟,才能对模块添加约束。如下例所示,我们先用create_clock命令建立了一个周期为2ns的虚拟时钟VClk,因为我们并没有指明这个时钟来自于哪个端口,所以这是一个虚拟的时钟。通过这个VClk,我们可以设置逻辑M和T的延迟。为了不产生亚稳态,从FF1时钟端的上升沿,到FF4时钟端的上升沿捕获,中间信号传输限制在一个时钟周期内完成。由此可以计算出被约束逻辑Combo延迟为2ns-0.4ns-0.2ns-0.1ns=1.3ns。

图6.20 组合逻辑路径的约束

相关推荐