如下例所示,设置了逻辑E最大延迟不超过0.4ns,逻辑G的最大延迟不超过0.2ns。图6.19 组合逻辑路径的约束另外一种情况如图6.20所示,被综合模块中没有时序逻辑器件,也没有时钟端口。为了不产生亚稳态,从FF1时钟端的上升沿,到FF4时钟端的上升沿捕获,中间信号传输限制在一个时钟周期内完成。由此可以计算出被约束逻辑Combo延迟为2ns-0.4ns-0.2ns-0.1ns=1.3ns。图6.20 组合逻辑路径的约束......

2023-06-26

上一节我们通过约束时钟来约束了寄存器间的时序路径,这一节我们要讨论的是模块输入输出路径的约束。

如图6.17所示,要综合组合逻辑N,我们必须提供给DC被综合模块前一级模块输入路径上的组合逻辑M的延迟,DC才能计算出逻辑N的最大延迟。如下例所示,我们用set_input_delay设置M逻辑的延迟在0.6ns以内,其中-max选项表示M逻辑延迟最大不超过0.6ns,后面中括号内返回的是除了时钟端口以外的所有输入端口的物集。为了不产生亚稳态,从FF1的时钟端的上升沿,到FF2时钟端的上升沿捕获,中间信号传输限制在一个时钟周期内完成。由此可以计算出被约束逻辑N延迟为2ns-0.2ns-0.6ns=1.2ns。

图6.17 输入路径的约束

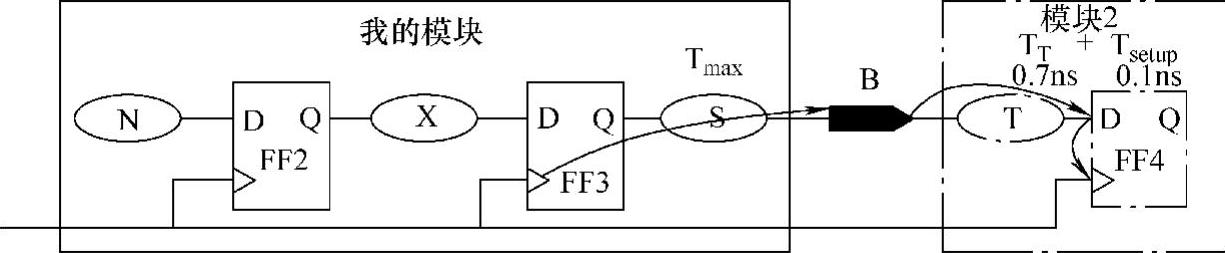

如图6.18所示,要综合组合逻辑S,我们必须提供给DC被综合模块后一级模块输入路径上的组合逻辑T的延迟,DC才能计算出逻辑S的最大延迟。如下例所示,我们用set_output_delay设置S逻辑的延迟在0.7ns以内,其中-max选项表示约束逻辑延迟最大不超过0.7ns。为了不产生亚稳态,从FF3的时钟端的上升沿,到FF4时钟端的上升沿捕获,中间信号传输限制在一个时钟周期内完成。由此可以计算出被约束逻辑S延迟为2ns-0.1ns-0.7ns=1.2ns。

图6.18 输出路径的约束

有关CMOS集成电路EDA技术的文章

如下例所示,设置了逻辑E最大延迟不超过0.4ns,逻辑G的最大延迟不超过0.2ns。图6.19 组合逻辑路径的约束另外一种情况如图6.20所示,被综合模块中没有时序逻辑器件,也没有时钟端口。为了不产生亚稳态,从FF1时钟端的上升沿,到FF4时钟端的上升沿捕获,中间信号传输限制在一个时钟周期内完成。由此可以计算出被约束逻辑Combo延迟为2ns-0.4ns-0.2ns-0.1ns=1.3ns。图6.20 组合逻辑路径的约束......

2023-06-26

PLC以循环扫描的方式工作,从PLC的输入端信号发生变化到PLC输出端对该输入变化做出反应,需要一段时间,这种现象称为PLC输入/输出响应滞后。但是PLC的扫描周期一般为几十毫秒,对于一般的工业设备不会影响系统的响应速度。即使在某个扫描周期干扰侵入并造成输出值错误,由于扫描周期时间远远小于执行器的机电时间常数,因此当它还没有来得及使执行器发生错误的动作,下一个扫描周期正确的输出就会将其纠正,使PLC的可靠性显得更高。......

2023-06-23

如图6.34所示,时钟周期定义为10ns,按设计规格,加法器的延迟为6个时钟周期。图6.34 多时钟电路设计如图6.35所示,DC将会仅仅在第6个时钟上升沿,即60ns处,建立时序分析。图6.36 多时钟保持时间约束保持时间将会提早5个时钟周期,所以加法器d允许延迟为Thold<加法器允许的延迟<60-Tsetup。图6.37是另一个多时钟周期的例子,图中乘法器运算为2个时钟周期,加法器运算为1个时钟周期,其约束为图6.37 多时钟电路设计......

2023-06-26

弘扬学校人文精神,需要从学校管理的方方面面进行统筹考虑,需要在学校办学理念设计、整体发展规划、课程与教学改革、师资队伍建设、校园文化塑造、管理制度革新等相关领域融入人文元素和人文情怀。这显然是一项极为复杂的工作,需要学校管理者的统筹设计和精心谋划。前文之中笔者的分析多集中于学校人文管理对教师发展的重要意义,这是因为从学校管理的角度出发,教师更容易成为学校管理的直接参与者与受益者。......

2023-07-19

但为了保证电路的每一条时序路径,特别是输入/输出路径延迟约束的精确性,我们还应该提供设计的环境属性,如图6.23所示。图6.23 环境约束每一个逻辑器件的延迟都与这个器件的输出负载和输入转换时间相关,其输出转换时间也与这个器件的输出负载和输入转换时间相关。我们可以用setload指定外部电容负载为一常数值,如图6.24所示。图6.25 指定实际器件负载图6.26 指定驱动器件如上文所述,在实际设计中,由于电路比较大,需要对设计进行划分。......

2023-06-26

如图6.27所示,图中有多个时钟,但这些时钟都是来自同一个时钟源。分别由3GHz的时钟通过9分频、6分频、4分频和3分频得到了CLKA、CLKC、CLKD和CLKE。图6.27 多时钟同步设计CLKC在被综合的模块中有对应的端口,则其定义就与单时钟一样,即:由于CLKA、CLKD和CLKE在要综合的模块中没有输入端口,因此需要使用虚拟时钟。图6.30 多时钟同步输出约束DC会找出波形上升沿间隔的多种情况,然后按照最严格的情况进行综合约束。......

2023-06-26

输入输出分析法又称“黑匣”或“黑箱”分析法。由于在构思方案的全过程中,设计者不断地运用发散和收敛思维,因此,输入输出分析法在构思方案时可以同时发挥两种创新思维方法的优点,既不受思考路径的限制,充分调动设计者具有的各方面的知识和经验,又能充分利用已知的知识和经验,将众多的信息逐步引导到条理化的逻辑序列中,最终得到一个合乎逻辑的设计方案。......

2023-06-26

用浮点运算器测试程序确认浮点运算器功能,应正常执行。2)模拟量输入输出模件,按以下要求寻址和精度检查:①利用测试程序对全部模件各地址逐个进行寻址和精度测量,对模拟量输入的检查,可在其输入端加入满量的0%、5%、25%、50%、75%、100%,根据CPU侧打印的数据,作出精度判断,应符合要求。......

2023-06-29

相关推荐