对1年内发生1次退回的水土保持方案编制单位提出批评,2次退回的提出警告并要求整改。......

2023-07-02

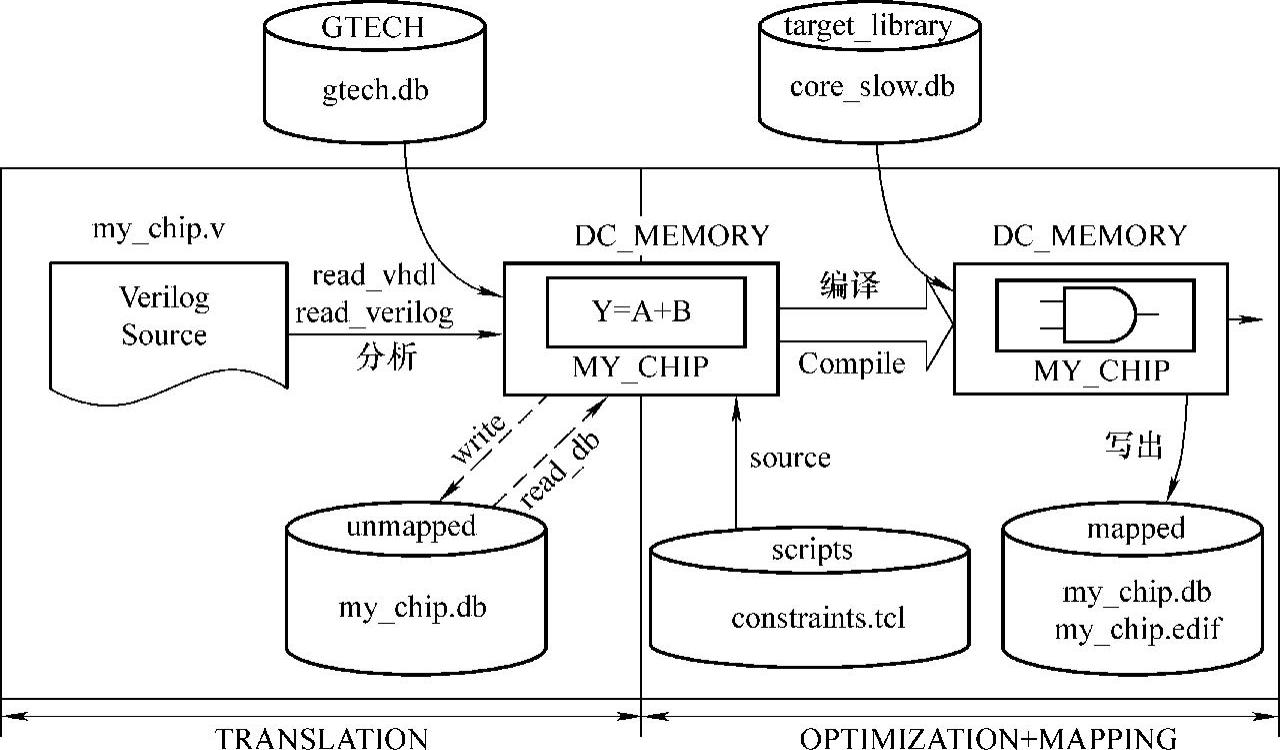

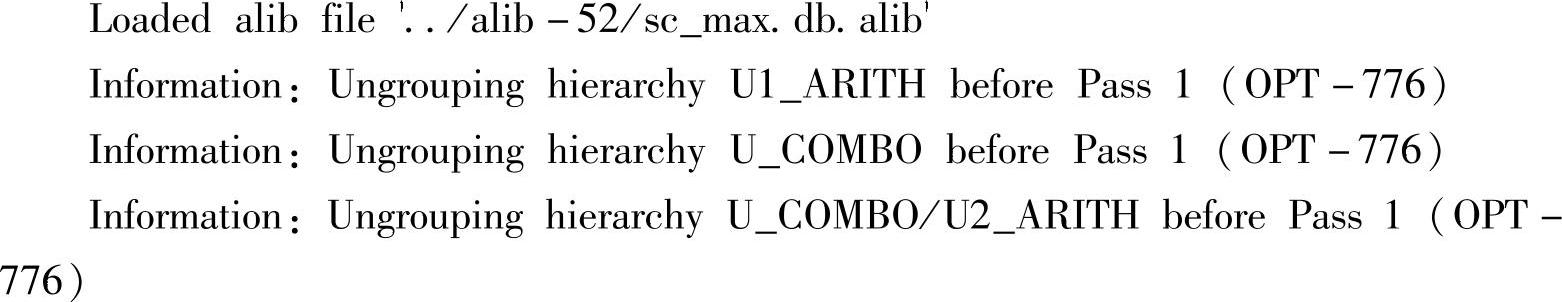

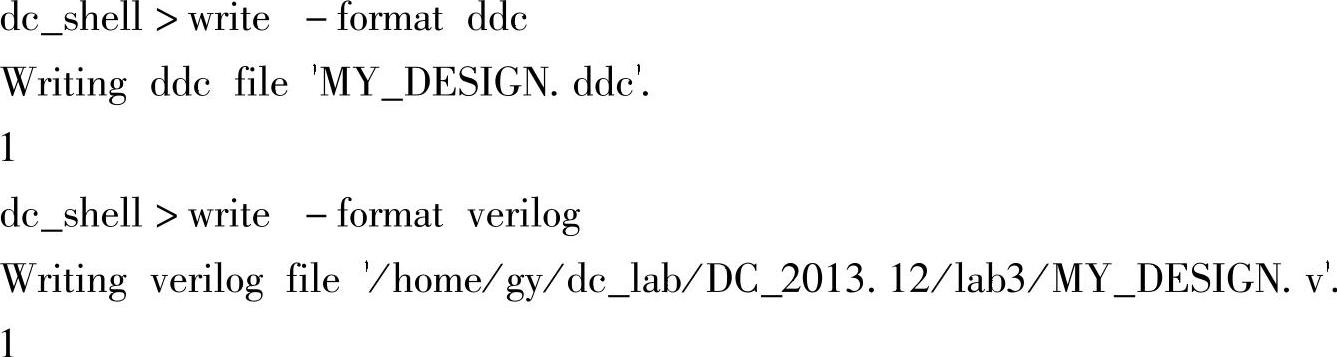

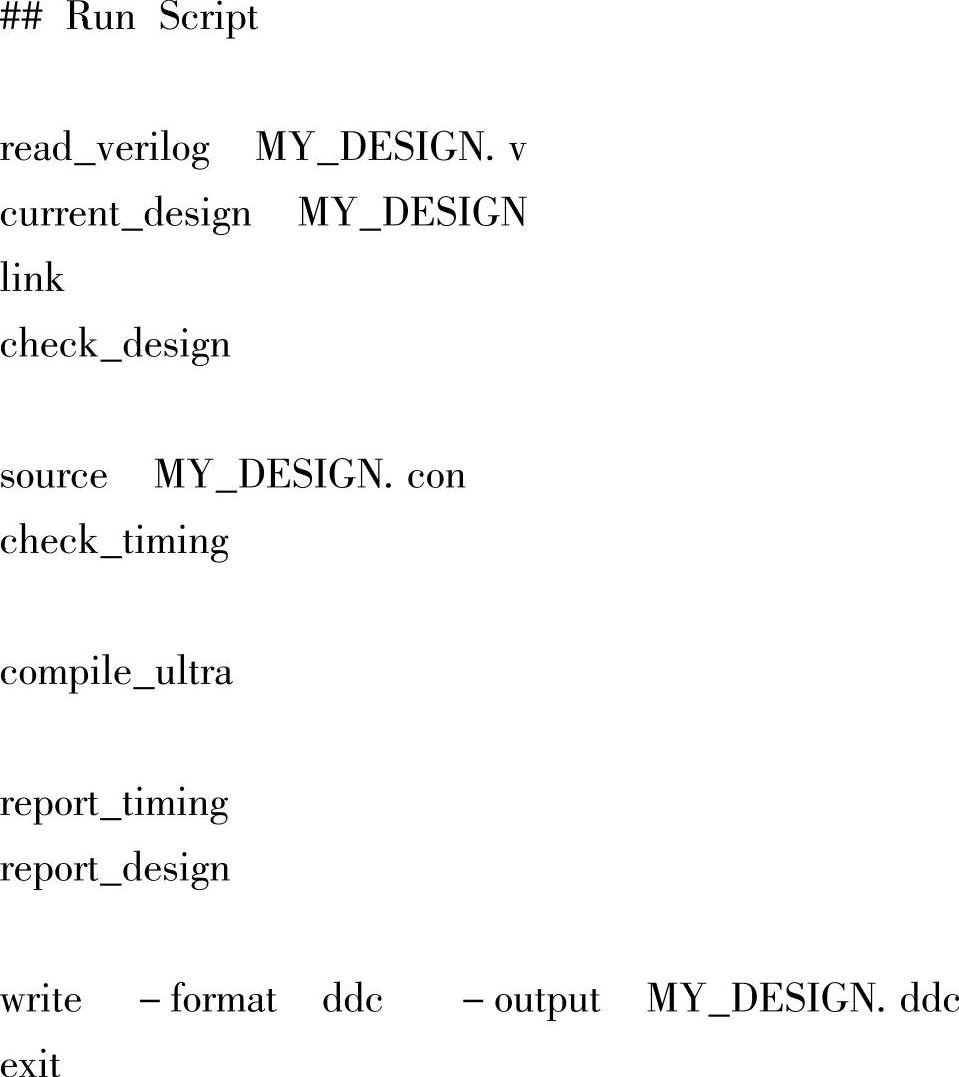

在配置好初始环境并且启动Design Compiler(DC)后,就开始了DC综合的流程。图6.8展示了DC综合几个基本的步骤,下面就这几个步骤进行介绍。

图6.8 DC综合的基本步骤

1.读入设计文件

DC综合工具的输入是RTL代码,所以在综合的第一步是将已经写好的RTL设计文件读入到DC的memory中。在读入层次化结构的设计中,综合工具需要知道哪一个文件是顶层文件,所以用户需要指定顶层文件。有两种方式完成这一步骤,一种是read_file的方式,另一种是analyze+elaborate的方式。

命令read_verilog和read_vhdl分别等价于命令read_file-format verilog和read_file-format vhdl,分别用于读取Verilog和VHDL写成的RTL设计代码(还有read_ddc,read_sverilog等)。

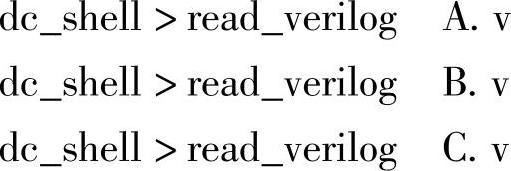

如例6.12中,先后用3个read_verilog命令读取了A.v、B.v和C.v 3个设计文件,DC会认为最后一个读取的文件C.v中的设计为顶层设计,A.v和B.v是它的子模块。

例6.12

如例6.13中,用一个read_verilog命令加花括号{}读取了A.v、B.v和C.v 3个设计文件,DC会认为花括号列表中第一个读取的文件A.v中的设计为顶层设计,B.v和C.v是它的子模块。

例6.13

为了避免人为因素导致的错误,建议用户在使用完read_file命令后用current_design命令显示指定顶层进行设计。例6.14中用current_design命令显示指定MY_TOP为顶层设计。

例6.14

将RTL代码读取到memory中并指定设计顶层后,DC会调用自己的GTECH库,将RTL转化为GTECH网表存在memory中。这个网表中的器件没有时序和负载的特性,它仅仅是DC用来表示器件的一个符号,只有DC能识别它。

另一种方式是analyze+elaborate。analyze命令首先会把Verilog或VHDL源文件读进DC的memory中,并检查语法规范,报出warning和error。然后会将RTL源代码转换成二进制格式的中间文件,存放在CWD中。elaborate命令会将analyze产生的二进制中间文件转换为GTECH网表,并且指定顶层设计。在命令中加选项-parameters能设置设计中的参数,这是在读文件过程中唯一能改变设计参数的方法。elaborate命令还自动地执行了link命令(read_file不会执行link,后文还会详细介绍这个命令),完成了链接操作。elaborate命令对于VHDL代码允许选择不同的结构体。如例6.15,设计顶层为MY_TOP,并且用户指定的参数设置会代替源代码中的默认参数。

例6.15

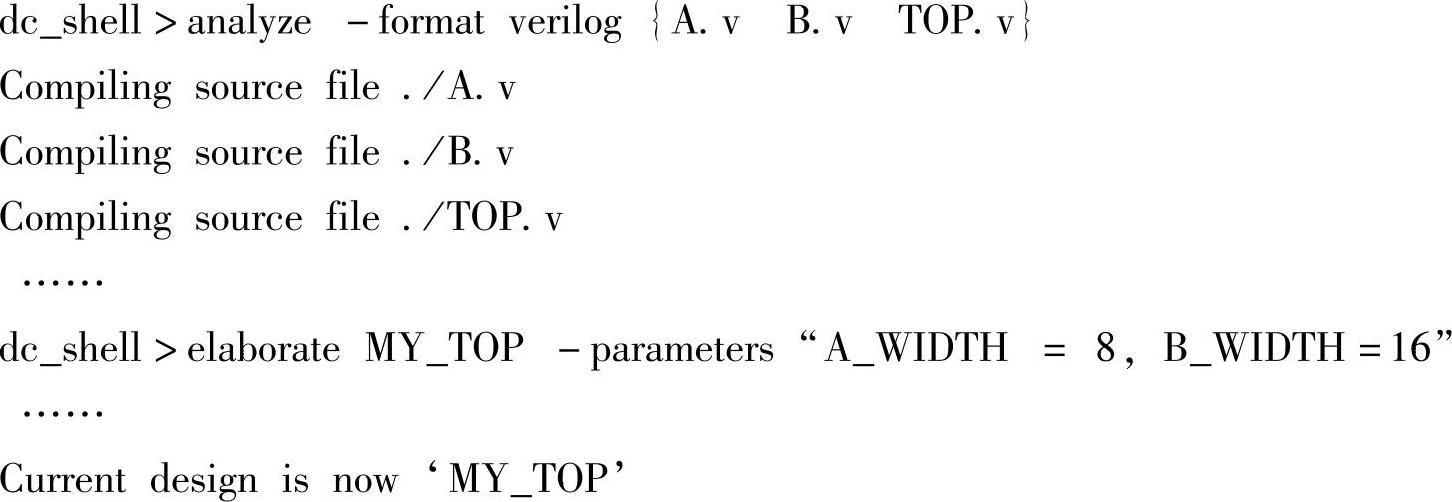

表6.2是两种读入文件方式的比较

表6.2 两种读入文件方式的比较

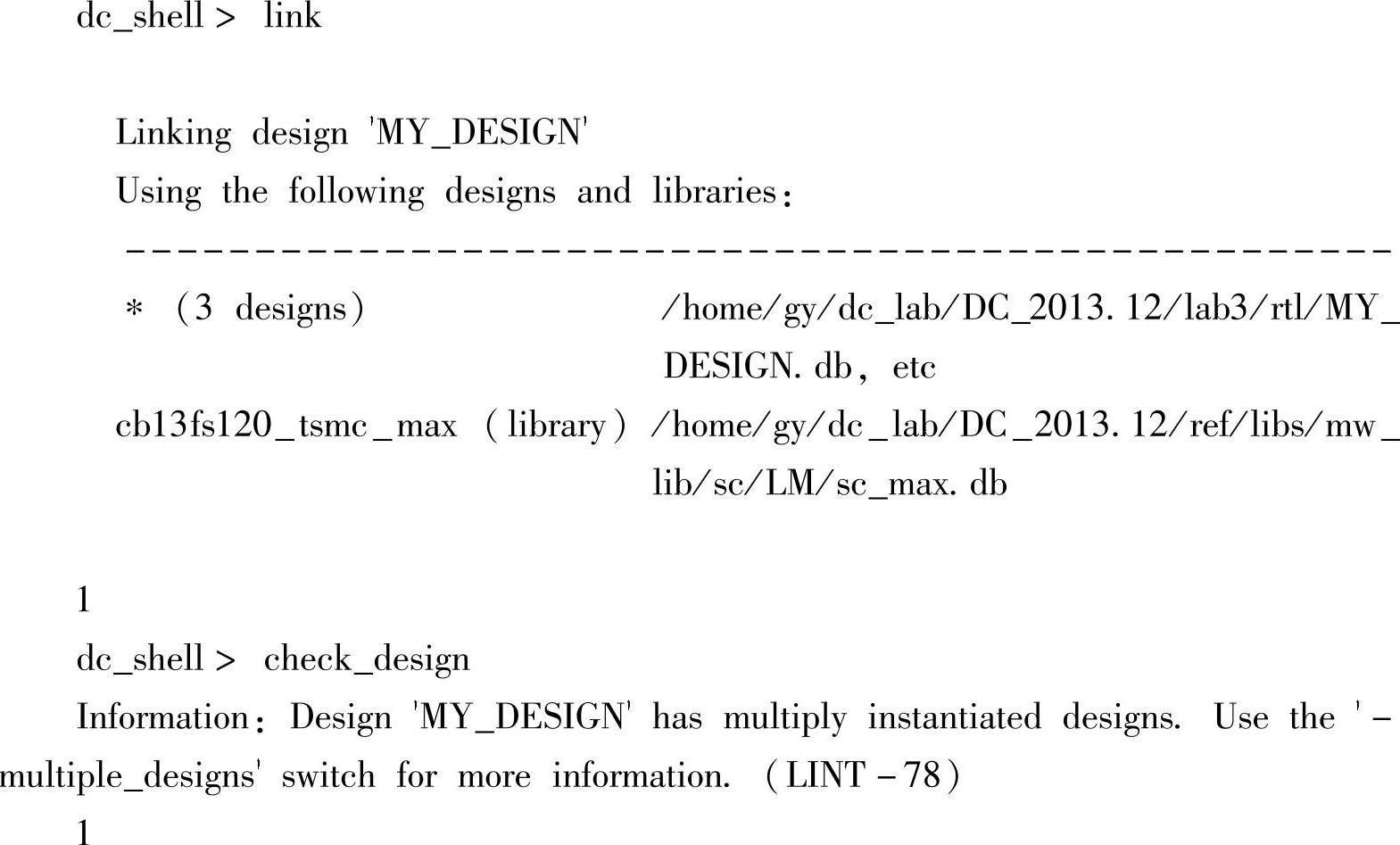

2.链接设计

对于一个完整的设计,它的每个单元必须都关联到库中的元器件,并且描述它的每一个引用,这个过程就叫作链接。链接可以用link命令执行,这个命令会用到link_library和search_path两个系统变量去解释设计中的各种应用。如上文所述,e-laborate命令中包含了link命令的操作,而如果用read_file读入文件,则必须用link命令链接。

在link命令后加上check_design命令是一个好习惯。check_design命令能够检查当前设计的内部表达的一致性,能发现一些问题并报出warning和error。比如一些未连接pin和一些递归的层次结构都可以发现并报错,如例6.16所示。

例6.16

3.添加设计约束

我们为了让电路实现预期的期望,达到设计的目标,会添加关于时序、面积和功耗等方面的约束,DC会根据这些约束对设计进行有效的优化。为了增强脚本的可读性,这里建议用户可单独建立一个约束的Tcl文件,然后在运行DC的脚本中用source命令执行该约束脚本。这样不容易出错,而且脚本思路清晰,可读性好。关于怎样添加约束,下一节会详细介绍。

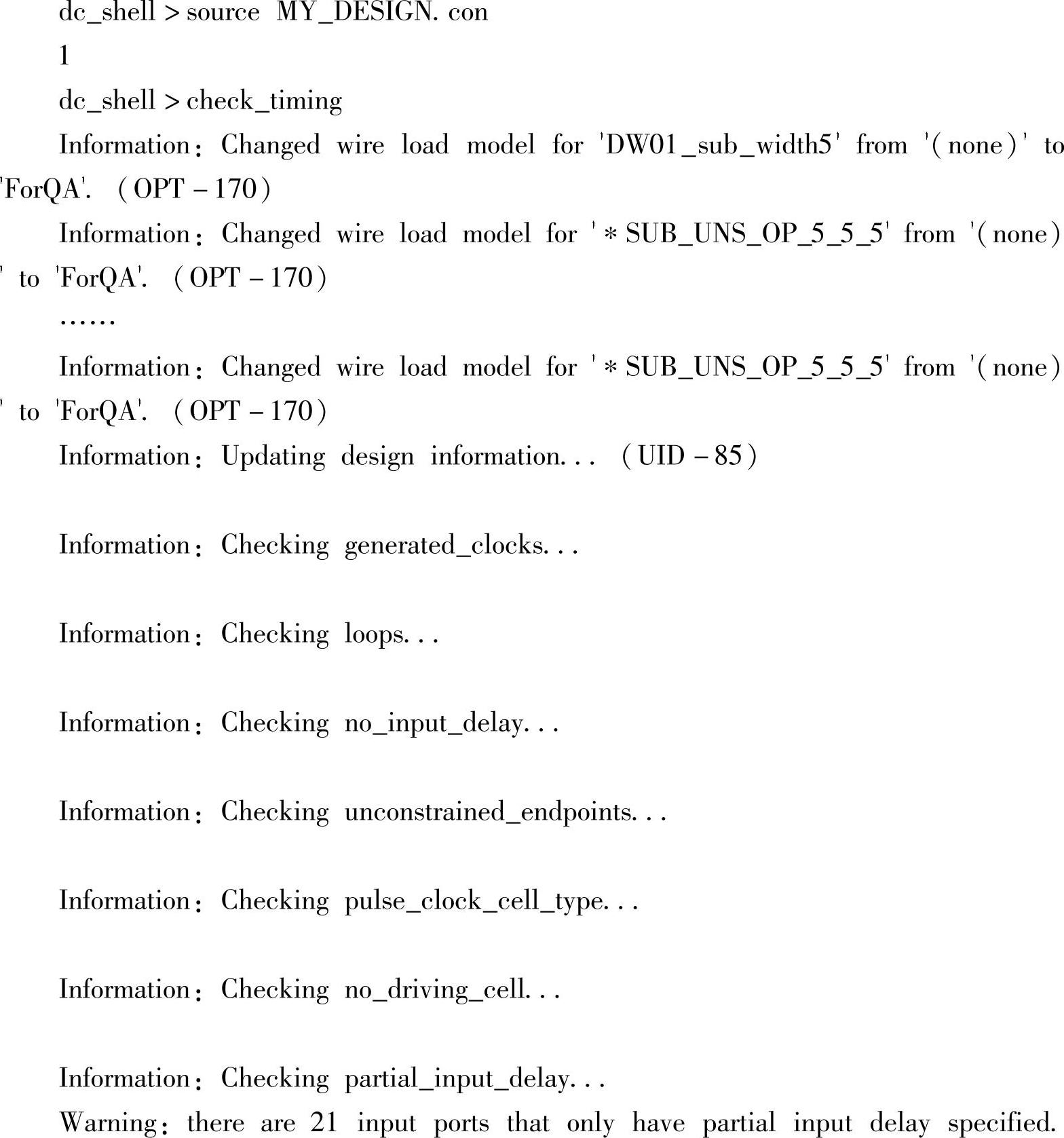

在执行完约束脚本后,建议用户执行check_timing命令。这个命令可以报告出当前设计的时序属性,未施加约束的节点,以及一些潜在错误和警告,供设计者参考,再进一步完善约束脚本,如例6.17所示。

例6.17

4.编译综合

添加设计约束后,就要命令DC根据约束的要求将GTECH网表中的逻辑器件映射到变量 target_library中指定库中的实际电气器件。这里需要用到compile命令,这个命令可以综合和优化当前设计中从逻辑层到门级网表层的部分。它的优化过程是根据用户施加的约束驱动的。

target_library中指定库中的实际电气器件。这里需要用到compile命令,这个命令可以综合和优化当前设计中从逻辑层到门级网表层的部分。它的优化过程是根据用户施加的约束驱动的。

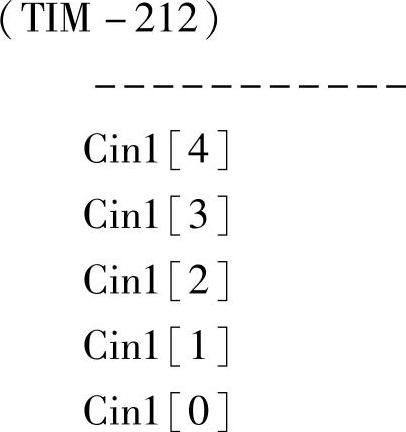

compile_ultra命令除了具有和compile一样的功能外,还提供了更强大的优化功能。它能提供对时序、面积、功耗等方面的并发优化手段来优化高性能设计,例如它能打破模块之间的边界,进行边界优化。它也能在算法层面优化,并且提供高级的时序分析以及关键路径的重编译,如例6.18所示。

例6.18

compile_ultra命令还可以添加各种选项,使其具有更加符合设计者需求的优化功能。读者可在DC的终端下输入man compile_ultra来获得命令帮助信息。DC的其他命令及内置变量都用man命令来获得命令的用法及选项。

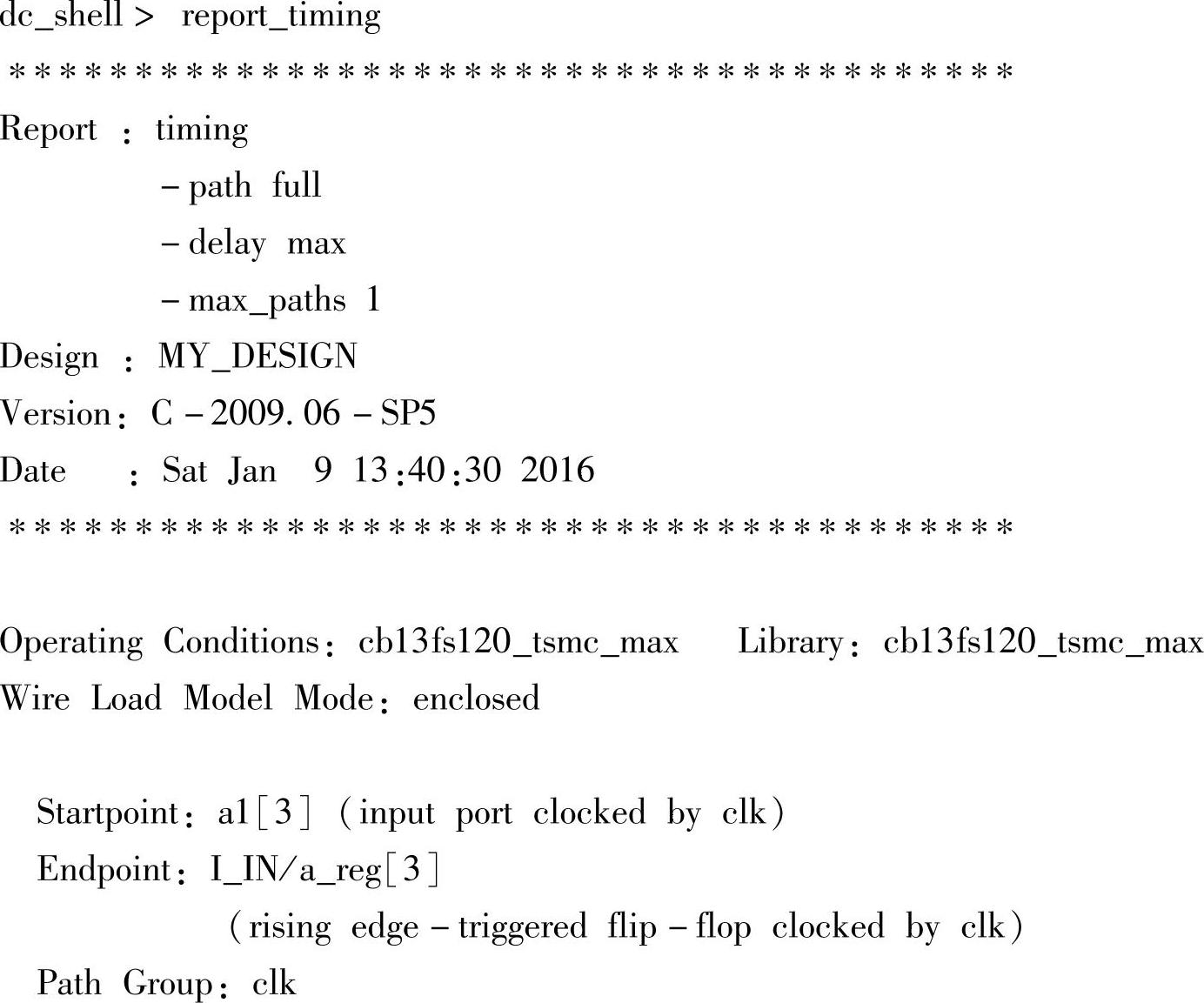

5.报告分析

编译综合完后,就得到了对应目标库的门级网表。但这个网表是否完全满足约束,我们并不知道。我们可以用report_*命令来产生各种报告,通过这些报告,可以了解到设计的一些信息。report_timing返回的是设计的时序报告,report_con-straint返回的是设计规则和时序违反约束,report_area返回的是面积报告等。例6.19是命令report_timing返回的报告,最后一行的(VIOLATED)表示设计违例。设计工程师需要修改约束或者RTL代码来消除违例。

例6.19

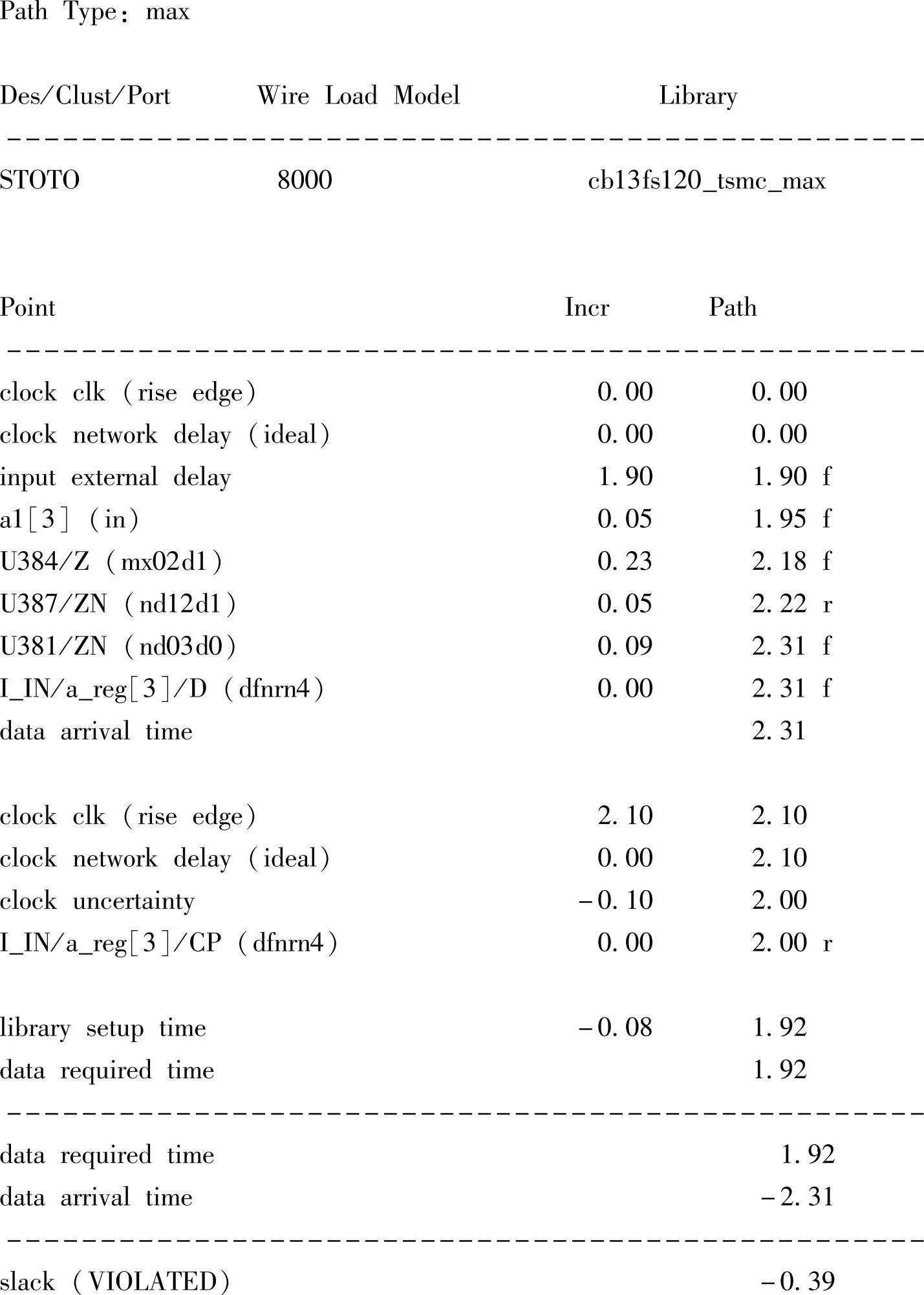

6.保存网表

通过以上步骤我们得到了所需要的门级网表,可以用write命令将生成的网表文件保存在磁盘上,可以通过-format选项选择保存文件的格式。如例6.20所示,可以是.v格式、.vhd格式和.ddc格式。其中.ddc格式是SYNOPSYS内置的内部数据库文件格式,.ddc文件不仅有网表中的器件连接信息,还包含网表的时序信息。它是二进制格式文件,SYNOPSYS工具读取它速度很快,是前端设计人员交付后端设计的最佳选择。

例6.20

例6.21为结合以上步骤编写的DC运行脚本。在DC终端用source命令执行该脚本就可自动完成以上综合的每个步骤。有利于简化综合操作流程以及完成交互式的任务。

例6.21

以上就是使用DC进行逻辑综合的基本流程。经过这6个步骤以后,我们将得到一个较为满意的门级网表,前端设计工程师就可以把它交付给后端部门进行下一步的设计了。

有关CMOS集成电路EDA技术的文章

2)物质流物质流控制是清洁生产实施的重中之重,它是“源消减”的核心体现。清洁生产更注重对物质流的优化,从而降低材料消耗,即实现过程改善。内循环就是在本项目生命周期内的继续使用,清洁生产的核心工作是废料管理的优化。......

2023-06-20

泸州市实验区对《泸州市中小学生综合素质评价实施方案(试行)》进行反复论证,历经近30次修改,最终形成《泸州市中小学生综合素质评价实施方案(试行)》方案。班主任、体育教师、艺术教师分别在《泸州市小学生综合素质学期评价表》中登记学生综合素质相关情况。学校德育部门在《泸州市小学生综合素质学期评价表》中对学生、教师的评价是否属实进行评价。......

2023-07-18

原型结构的综合延伸设计,是更为贴近实现服装原创设计作品的结构技术性运用。1.衣身原型结构的综合延伸设计衣身原型结构的综合延伸设计是对衣身结构各方面多种因素的考虑,其结构的设计构成关系已初具服装的丰富性和完整性。......

2023-06-24

等离子彩电组件可分为屏上组件和整机生产厂家生产的自制组件两部分。市场上的等离子彩电品种规格较多,主板采用的集成电路各不相同,但它们的主板基本工作原理基本相同。为了便于读者对主板有所了解,本章将各个品牌等离子彩电的主板电路组成和信号流程介绍给读者,为维修主板时追踪信号流程和判断主板是否正常提供依据。......

2023-06-29

数字电路的逻辑综合由3部分组成:综合=转化+逻辑优化+映射。第二步是根据设计工程师对电路预期功能的要求,对GTECH网表施加时序、功耗和面积等各方面的约束,使其能达到设计的目标。图6.2 逻辑综合流程综合的结果和设计提供的约束有着直接关系,通过添加的各种约束来让综合工具优化我们的设计,并使其满足设计目标。图6.3是综合结果的时序和面积折中曲线,可见设计的结果或是面积大,延时短,或是面积小,延时长,或是两者都适中。......

2023-06-26

(一)设计的前期准备前期的准备工作主要包括阅读产品零件图,收集、查阅有关资料,根据产品的原始数据研究设计任务,分析产品实施冷冲压加工的可能性、经济性等。本设计的产品材料是45钢,属优质碳素结构钢,其力学性能是强度、硬度和塑性指标适中,经退火后,用冲裁的加工方法是完全可以成形的。②落料、冲孔单工序模,工序图如图2-55所示。......

2023-06-30

(一)制定实施方案学校依据市区级综合素质评价标准制定学校校本化方案是实施综合素质评价的基础。美习拍卖会学生的习惯养成一直以来都受到学校的高度重视,为了让孩子进入梁才后能尽快养成良好的习惯,并且能长久的坚持下去,学校为孩子设计了美习卡,并以美习币的形式对孩子的表现进行评价。(四)开展师生培训梁才学校采用落实到人环环紧扣的方法扎实推进学生综合素质评价。......

2023-07-18

相关推荐