逻辑推理有四大基本规律,即同一律、矛盾律、排中律和充分理由律。矛盾律要求思想前后一贯,不能自相矛盾。违反了这一规律,就要犯虚假理由、以偏概全、推不出等逻辑错误。逻辑思维能力是指正确、合理思考的能力。即对事物进行观察、比较、分析、综合、抽象、概括、判断、推理的能力以及采用科学的逻辑方法准确而有条理地表达自己思想观点的能力。......

2023-10-26

数字电路的逻辑综合由3部分组成:综合=转化+逻辑优化+映射。

第一步是用read命令将HDL代码转化为通用的布尔门阵列,也就是GTECH(generic technology)库中的逻辑器件。这个库中的器件没有时序和负载的特性,它仅仅是Design Compiler用来表示器件的一个符号,只有Design Compiler能识别它。

第二步是根据设计工程师对电路预期功能的要求,对GTECH网表施加时序、功耗和面积等各方面的约束,使其能达到设计的目标。

第三步用compile命令,将电路按照设计的约束优化和综合,使其能满足设计的目标或约束,并且映射到特定厂家目标工艺库中的逻辑器件,此时的网表包含了厂家的工艺参数。

第四步用report命令,产生各种设计报告,设计工程师可通过这些报告分析评估该网表是否满足预期需求。若不满足预期需求,可对设计约束或者RTL进行修改直到满足需求为止。

最后用write命令,将满足设计需求的门级网表以ddc的格式保存在磁盘上。

整个流程如图6.2所示。

图6.2 逻辑综合流程

综合的结果和设计提供的约束有着直接关系,通过添加的各种约束来让综合工具优化我们的设计,并使其满足设计目标。

设计工程师提供约束指导综合工具,综合工具使用这些信息尝试产生满足时序要求的最小面积设计。如果没有提供约束,综合器会产生非优化的网表,该网表可能不能满足设计师的要求。

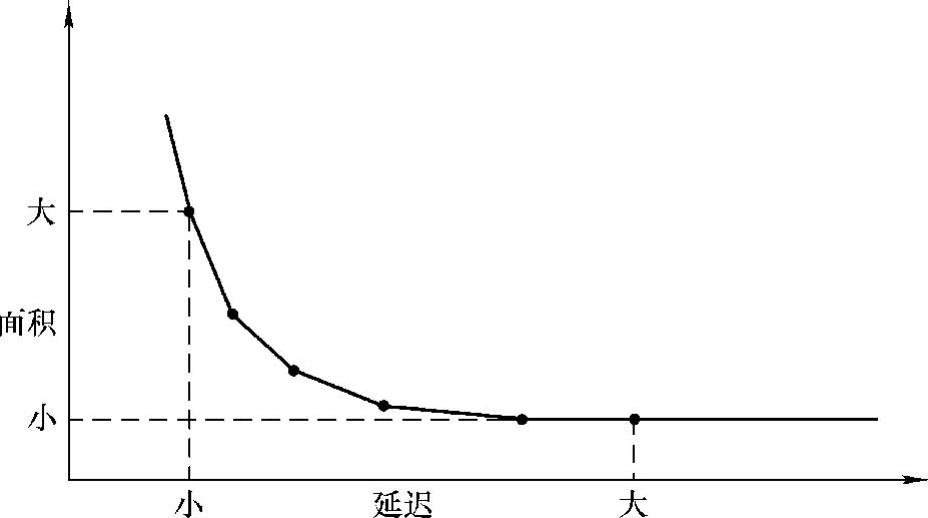

图6.3是综合结果的时序和面积折中曲线,可见设计的结果或是面积大,延时短,或是面积小,延时长,或是两者都适中。

图6.3 时序和面积的权衡关系

有关CMOS集成电路EDA技术的文章

逻辑推理有四大基本规律,即同一律、矛盾律、排中律和充分理由律。矛盾律要求思想前后一贯,不能自相矛盾。违反了这一规律,就要犯虚假理由、以偏概全、推不出等逻辑错误。逻辑思维能力是指正确、合理思考的能力。即对事物进行观察、比较、分析、综合、抽象、概括、判断、推理的能力以及采用科学的逻辑方法准确而有条理地表达自己思想观点的能力。......

2023-10-26

在配置好初始环境并且启动Design Compiler后,就开始了DC综合的流程。例6.13为了避免人为因素导致的错误,建议用户在使用完read_file命令后用current_design命令显示指定顶层进行设计。例6.14中用current_design命令显示指定MY_TOP为顶层设计。check_design命令能够检查当前设计的内部表达的一致性,能发现一些问题并报出warning和error。读者可在DC的终端下输入man compile_ultra来获得命令帮助信息。report_timing返回的是设计的时序报告,report_con-straint返回的是设计规则和时序违反约束,report_area返回的是面积报告等。......

2023-06-26

图6.1中,“综合”部分将是本章讨论的重点。图6.1 系统开发的基本设计流程逻辑综合是随着20世纪80年代VHDL、Verilog HDL的产生、发展而诞生,并逐渐成熟的。最初的逻辑综合器支持的HDL语法形式较少,其智能程度及综合效率都比较低。随着逻辑综合技术的不断进步,逻辑综合器的执行效率和优化能力都有了很大程度上的进步。......

2023-06-26

时钟树综合前的时钟网络如图8.27所示,呈发射状。为了平衡寄存器到时钟端口的延时,时钟树综合通过许多专用的时钟缓冲单元来搭建平衡的网状结构。也就是基于如上原因,时钟树综合这一步骤在数字物理设计流程中,一般在布局完成后进行。具体到Encounter工具,Encounter的时钟树工具现在版本使用的有两个时钟树综合引擎,两者均有读入SDC约束的能力。......

2023-06-26

数字动画创作流程与传统动画既有相似、又有区别,整体的创作思路依然延续传统制作顺序,但在流程上有了更多数字化的改进。以三维动画的创作流程为例,我们可以了解数字动画的整个制作环节及步骤。迪士尼动画《花木兰》在原版故事的基础上进行新的开发和创作,将传统的东方女性形象加以修饰,赋予更新的时代意义。数字故事板是数字动画制作的特有的环节,加上初步的对话、音效与配乐,让整个影片看起来更像一部完整的电影。......

2023-09-25

如前面所述,ICC中使用的逻辑层数据主要是db文件,其文件内的信息与lib文件相同,只不过经过压缩转化成了二进制文件,因此不可阅读或编辑;但db文件大大减小了前端综合与后端设计时对内存的需求,加快了运算速度。以一个模拟单元为例,lib文件的格式大致如下。......

2023-06-26

图4.46显示的是EPP纳米线通过FIB方法制得的EPP纳米线器件的SEM图像。随后对EPP纳米线的其中两段的电学性质进行研究。经过进一步研究发现,这种轴向EPP双P-N异质结三段纳米线的特异的电学性质恰好与逻辑门中的二输入或门表现出同样的现象。图4.47EPP杂化纳米线逻辑门(见彩图)EPP纳米线用作2输入或门;标准的2输入或门符号;EPP纳米线用作2输入或门的电信号输入输出曲线;EPP纳米线用作2输入或门的输入输出数值......

2023-06-30

逻辑斯蒂方程是一种在许多领域中都有着广泛应用的数学模型,下面我们通过树的生长过程的例子来说明该模型的建立过程.一棵小树刚栽下去的时候长得比较慢,渐渐地,小树长高了,而且长得越来越快,但长到某一高度后,它的生长速度趋于稳定,然后再慢慢降下来.这一现象具有普遍性.现在我们来建立这种现象的数学模型.如果假设树的生长速度与它目前的高度成正比,则显然不符合两头尤其是后期的生长情形,因为树不可能越长越快;但如......

2023-10-19

相关推荐