数字电路的逻辑综合由3部分组成:综合=转化+逻辑优化+映射。第二步是根据设计工程师对电路预期功能的要求,对GTECH网表施加时序、功耗和面积等各方面的约束,使其能达到设计的目标。图6.2 逻辑综合流程综合的结果和设计提供的约束有着直接关系,通过添加的各种约束来让综合工具优化我们的设计,并使其满足设计目标。图6.3是综合结果的时序和面积折中曲线,可见设计的结果或是面积大,延时短,或是面积小,延时长,或是两者都适中。......

2023-06-26

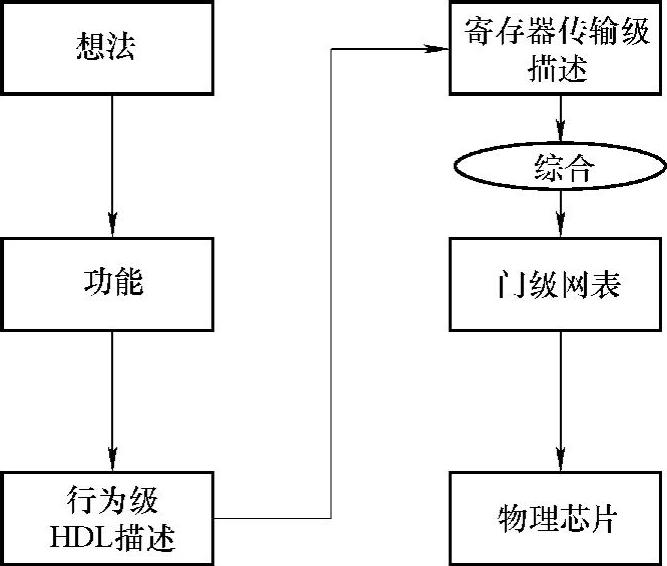

在上一章我们讨论了如何用硬件描述语言来设计数字系统层次的结构模型。首先我们有一个需要解决的问题,然后用一个想法去解决这个问题,再将这个想法用RTL代码去描述,包括定义数字电路的层次结构;定义设计中的寄存器结构与规模;定义设计中的组合电路功能。

接下来我们要将这个HDL设计的模型映射成可制造的电路器件的门级网表,并且保证映射后的器件能执行预期的功能,这就是逻辑综合。就像C语言中编译器连接C语言和机器语言一样,逻辑综合连接了HDL代码和门级网表。图6.1是一个系统开发的基本设计流程。

图6.1中,“综合”部分将是本章讨论的重点。“综合”之前的设计步骤在第5章中已经进行了详细阐述,本章将不再赘述。

图6.1 系统开发的基本设计流程

逻辑综合是随着20世纪80年代VHDL、Verilog HDL的产生、发展而诞生,并逐渐成熟的。最初的逻辑综合器支持的HDL语法形式较少,其智能程度及综合效率都比较低。设计者只能应用HDL代码中的一部分来进行设计,所以给电路设计带来了大量的困难。随着逻辑综合技术的不断进步,逻辑综合器的执行效率和优化能力都有了很大程度上的进步。为了提高电路的集成度、缩短设计周期,从20世纪90年代开始,行为综合方法应运而生。它开始于算法描述及HDL行为建模,由行为综合工具根据设计的行为描述,自动生成对应的门级网表。

后来伴随着其他新的硬件设计描述语言(System Verilog、System C等)出现,现在的综合器所支持的语言也趋近多样化。设计工程师可以灵活地选择设计语言来完成各个层次的设计。

有关CMOS集成电路EDA技术的文章

数字电路的逻辑综合由3部分组成:综合=转化+逻辑优化+映射。第二步是根据设计工程师对电路预期功能的要求,对GTECH网表施加时序、功耗和面积等各方面的约束,使其能达到设计的目标。图6.2 逻辑综合流程综合的结果和设计提供的约束有着直接关系,通过添加的各种约束来让综合工具优化我们的设计,并使其满足设计目标。图6.3是综合结果的时序和面积折中曲线,可见设计的结果或是面积大,延时短,或是面积小,延时长,或是两者都适中。......

2023-06-26

国际学术界最早的界定是美国教育心理学家科克于1963年提出的学习障碍概念。他认为学习障碍是指儿童在语言、说话、阅读和社会交往技能方面的发育障碍。......

2023-07-02

目前学术界及业界从内容、功能、分类等不同层面对电视新闻节目做出了界定,代表观点如下。(二)电视新闻节目发展历程1.美国电视新闻节目的发展历程从世界范围来看,美国的电视新闻业发展较早。美国早期电视新闻主要受新闻电影纪录片以及广播新闻节目的影响。这一时期,美国各类新闻节目,包括新闻杂志节目、联播型节目、新闻访谈节目等都呈现出繁荣的发展状态。......

2023-10-30

6第二节 逻辑的定义……………………………………………………8第三节 形式逻辑与其他科学的关系………………………………18第四节 形式逻辑的意义——为什么要研究逻辑…………………240第二节 归纳推理形式的种类………………………………………308第六节 证明在逻辑中的地位………………………………………327附录六:形式逻辑教学图解的商榷……………………………………......

2023-11-08

对渔港的定义较多:2004年1月1日起施行的《中华人民共和国港口法》第59条对渔港的定义是:“渔业港口,是指专门为渔业生产服务、供渔业船舶停泊、避风、装卸渔获物、补充渔需物资的人工港口或者自然港湾,包括综合性港口中渔业专用的码头、渔业专用的水域和渔船专用的锚地。”此外,由于服务对象的特殊性,渔港在港口设施的设置和布局上也与普通货运港口有一定差异。......

2023-11-29

表2-1我国主要的第三方支付机构续表(二)我国网络支付的发展历程网上支付如今俨然已经成为消费者网上交易活动的首选支付方式。我国第三方支付平台的发展历程可以分为三个阶段。同时,地方性、区域性移动支付也和第三方支付机构一起充当补充者的角色。央行公布数据显示,2016年第三方支付机构累计发生网络支付业务1639亿笔,移动支付交易规模达58.8万亿元,同比分别增长99.5%和87%。......

2023-07-05

C语言是目前使用非常广泛的高级程序设计语言。C语言就在这种情况下应运而生,并迅速成为国际上广泛流行的计算机高级语言。C语言的原型是ALGOL 60语言。其意义在于将CPL语言“煮干”,提炼出它的精华。1977年,Dennis M.Ritchie发表了不依赖于具体机器系统的C语言编译文本《可移植的C语言编译程序》。1987年,ANSI又公布了新的C语言标准——87 ANSI C。......

2023-11-18

第十章艺海沧桑成长期的相声从无到有,从小到大,经历了由发祥地北京向外地普及的过程。二十世纪四十年代,侯宝林、郭启儒自东北、天津返京,献艺于上海游艺社和西单游艺社,由于内容健康,格调清新,被誉为“文明相声”,受到热烈欢迎。清末以来,相声艺人逐渐从北京流向外地。最早离京赴津的是满族艺人裕二福。......

2024-06-06

相关推荐