4)其他:finish等系统任务;除法;table;stong1、weak0等信号强度的描述。......

2023-06-26

1.组合逻辑实例:编码器

编码器是将某些特定的逻辑信号变成二进制编码,能够对原有信号进行转换压缩,常用于通信、数字信号处理等系统中。简单4-2编码器是典型的组合逻辑,输入信号根据规则变成有标准的编码信号,4-2编码器是指输入4bit位宽信号,经过编码器后,输出2bit编码信号,其真值表如表5.1所示。

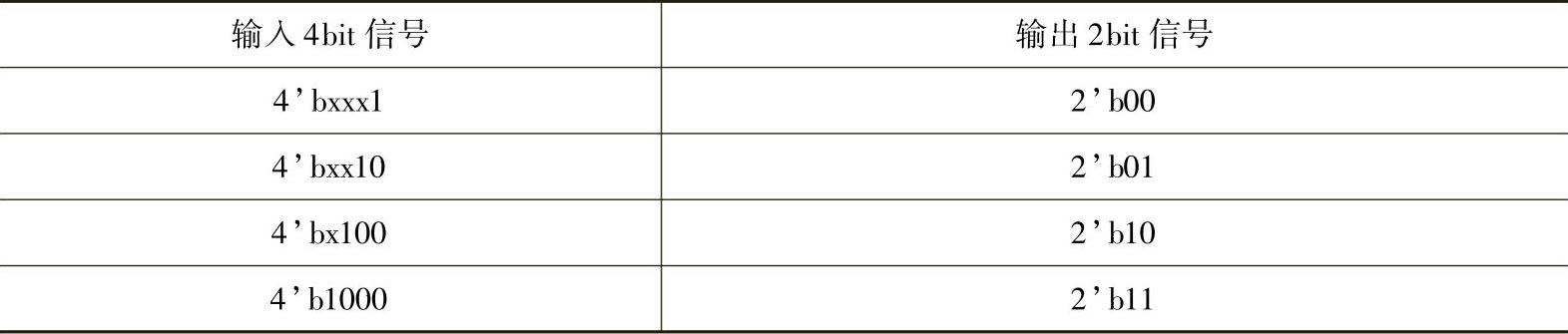

表5.14-2 编码器真值表

表5.1中,“x”表示不定位,可以是“0”,也可以是“1”,根据真值表写出Verilog实现代码,如例5.2所示。

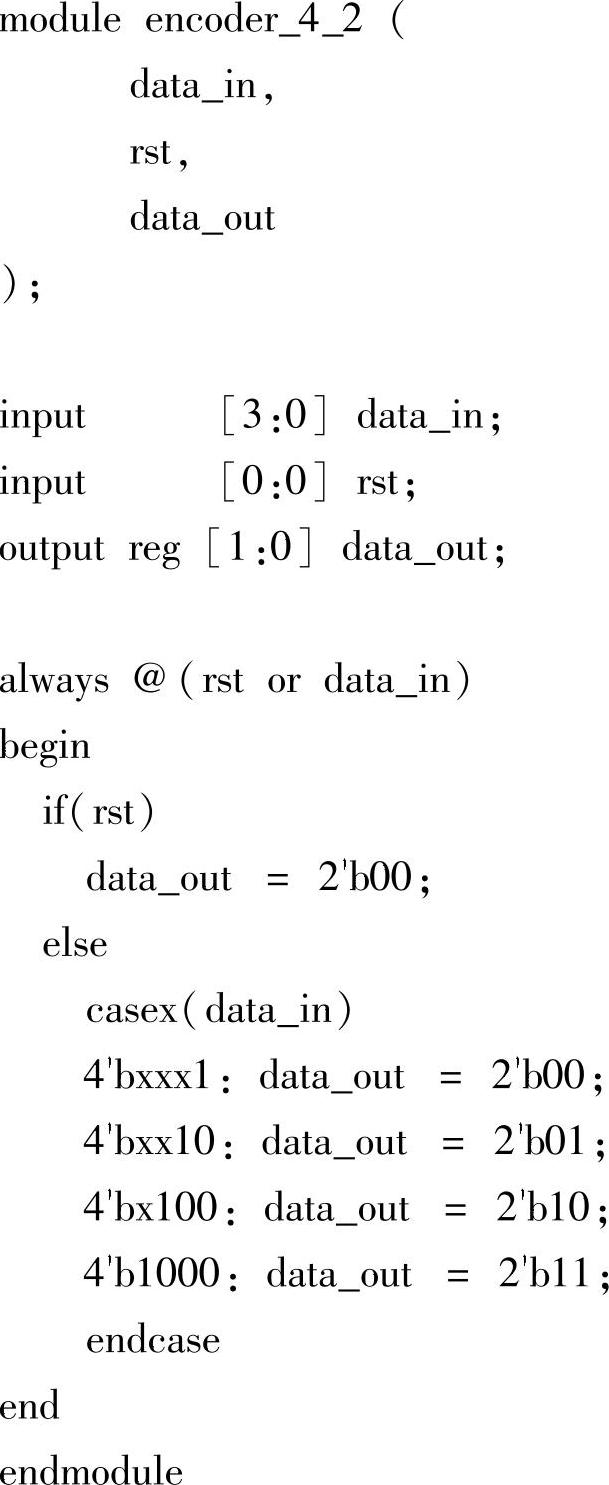

例5.2 4-2编码器示例

主要使用casex语句实现编码过程,其测试文件如例5.3所示。

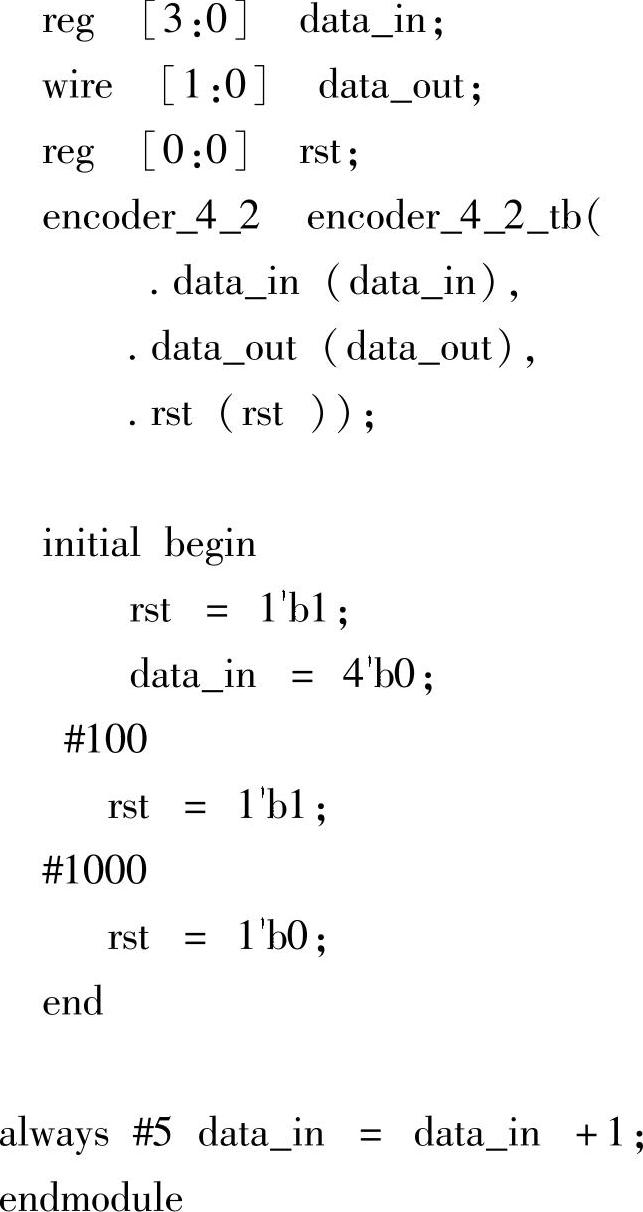

例5.3 4-2编码器测试文件

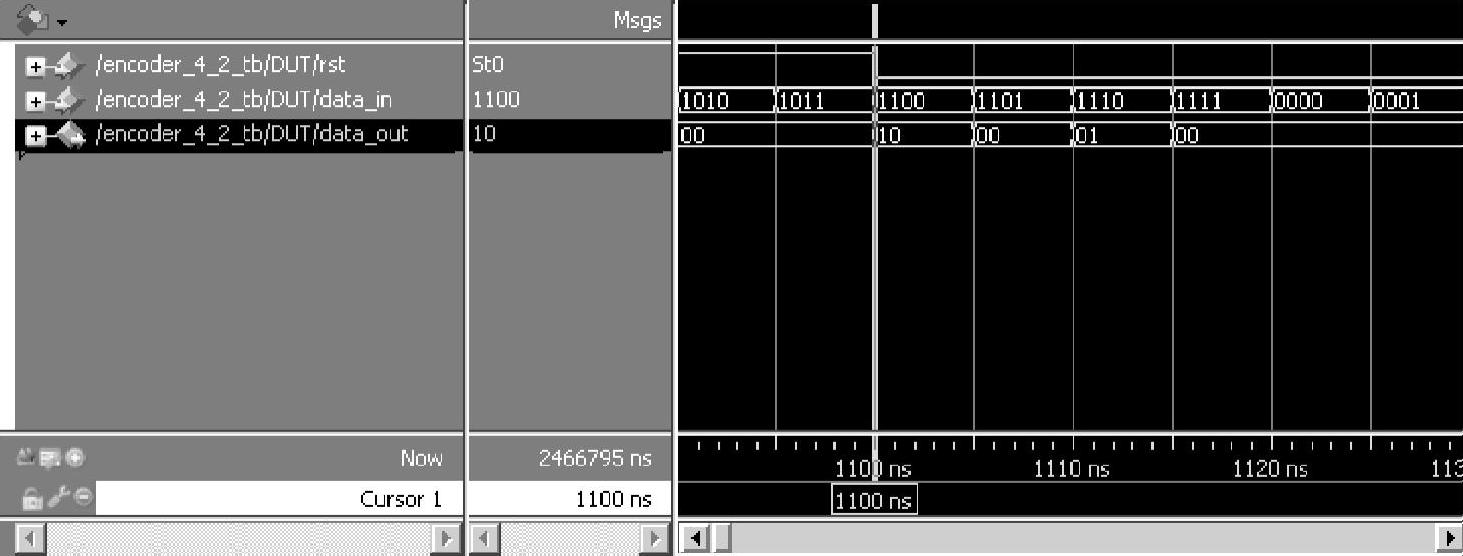

编码结果如图5.12所示。

图5.12 4-2编码器仿真结果

图5.12中,当复位信号“rst”释放之后,输出信号“data_out”根据输入信号“data_in”的变化而变化,查找真值表,输入“1100”输出“10”,输入“1101”输出“00”,与真值表吻合,实现了4-2编码功能。

2.时序逻辑实例:分频器

分频器是将输入信号的频率进行分频,把输出信号的频率变成成倍低于输入信号的频率,相位保持一致,也可以根据设计者需求调整初始相位。简单分频器是典型的时序逻辑,在这里以四分频为例,将输入的时钟信号进行四分频输出,如例5.4所示。

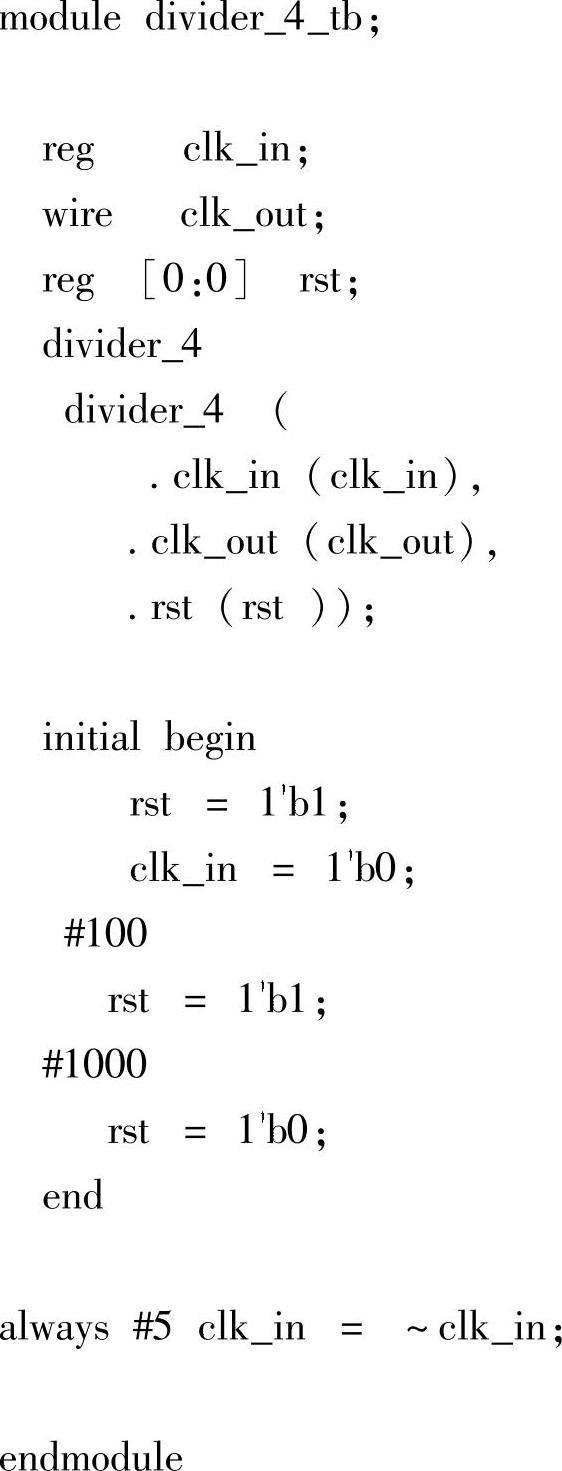

例5.4 四分频示例

主要通过两个寄存器实现,第一个用输入时钟“clk_in”触发,第二个用第一个寄存器的输出“clk_temp”触发,能够实现两个二分频电路的级联。其测试代码如例5.5所示。

例5.5 四分频器测试代码

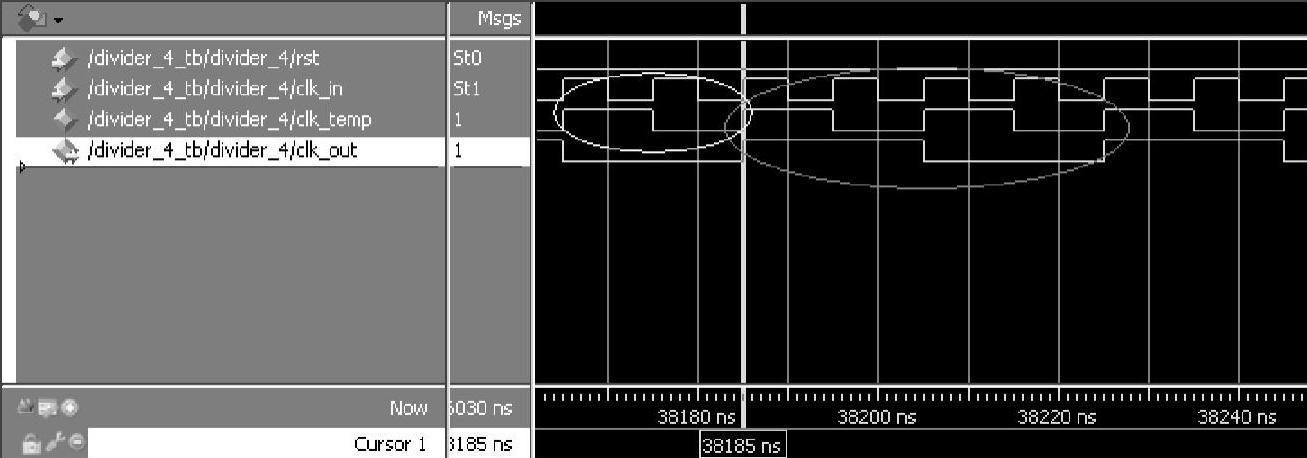

仿真结果如图5.13所示。

图5.13 四分频器仿真结果

图5.13中,可以看出输出信号“clkout”是输入信号“clkin”的四分频,用大线圈出,其中,中间信号“clktemp”是输入信号“clkin”二分频的结果,用小线圈出,两个二分频电路的级联,结果就是四分频。

有关CMOS集成电路EDA技术的文章

Verilog语言博大精深,本节提取Verilog语言精华做详细介绍,主要从以下几个方面入手:Verilog语言基本结构、其门级描述与行为级描述,搭建组合逻辑与时序逻辑,以及如何使用状态机,从基础框架到骨髓血液,整个硬件描述语言塑造成型。图5.3 Verilog基本结构1.Verilog基本结构Verilog模块在工程中以.v的文件形式存在,在每个.v文件中都定义了一个功能模块,其基本结构如图5.3所示。......

2023-06-26

算法的描述方法主要有如下几种。例如,用传统流程图表示的顺序结构如图3.2所示,用NS图表示的顺序结构如图3.2所示,表示先执行A操作,再执行B操作,两者是顺序执行的关系。......

2023-11-20

项目2:输入一行字符,分别统计出其中英文字母、空格、数字和其他字符的个数。图3.15兔子问题输出结果根据以上的分析可以知道,循环次数可以为0,因此该程序是一个条件型循环,可以利用while语句编写程序。熟悉了循环结构在程序设计中的运用,循环结构语句包含了while语句、do…......

2023-11-18

例4.16从键盘上输入一行英文字符串,判断该字符串的每一单词的第一个字母是否是大写,若不是,则改为大写字母。利用大小写对应ASCII码值之间的差值,可以很方便地完成大小写间的转换操作,如“ch[i]=ch[i]-32;”语句便实现了将小写字母转换成对应的大写字母。例4.17编写一个简单的密码程序。7438jkd你不是合法用户,不能进入本系统!例4.18从键盘上输入4个字符串,比较它们之间的大小关系,然后按从小到大的顺序存放到二维数组中并输出。......

2023-11-18

条件编译使得同一源程序在不同的编译条件下得到不同的目标代码。商业软件公司总是使用条件编译来提供和维护某一程序的多个顾客版本。条件编译有几种常用的形式,现分别介绍如下:#ifdef标识符这种形式的含义是:如果标识符已被#define行定义,则编译程序段1,否则编译程序段2。例6.1条件编译的简单应用。例6.2输入一行字母序列,根据需要设置条件编译,使之能将字母全改为大写输出,或全改为小写字母输出。......

2023-11-18

硬件测试系统包含本项目所使用的硬件设备,主要包括传感器、信号调理器、数据采集设备和计算机等部分。物流包装材料无害化生产过程数据采集系统硬件设备主要包括塑料注塑成型机、计算机、数据采集卡、传感器、信号调理器等。通过数据采集卡获取数据是主要的渠道,系统采用了NI公司基于PCI总线的数据采集卡PCI6221以及USB接口的数据采集卡USB6221,采集卡集成了A-D转换和数字I/O等功能。图6-13 测试系统硬件设计方案表6-3 采集所用的各种传感器......

2023-07-02

图2.4中,横向向左的箭头表示必定发生的转换。如果将一个实型数据赋值给一个整型变量,那么将舍弃实型数据的小数部分。例如,将2.12赋值给整型变量i,结果为2。图2.5自动转换int型与1ong型。......

2023-11-18

相关推荐