4)其他:finish等系统任务;除法;table;stong1、weak0等信号强度的描述。......

2023-06-26

Verilog语言博大精深,本节提取Verilog语言精华做详细介绍,主要从以下几个方面入手:Verilog语言基本结构、其门级描述与行为级描述,搭建组合逻辑与时序逻辑,以及如何使用状态机,从基础框架到骨髓血液,整个硬件描述语言塑造成型。

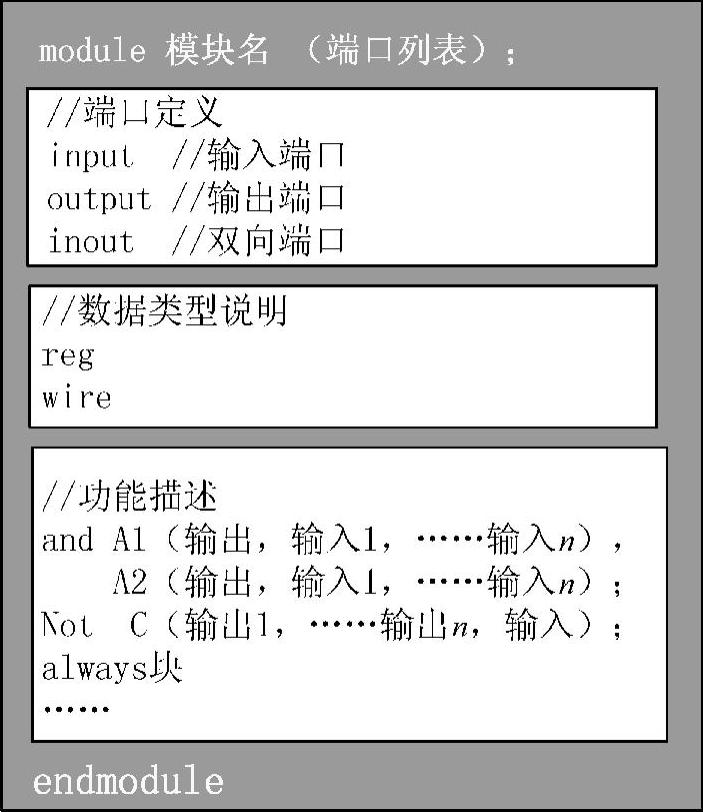

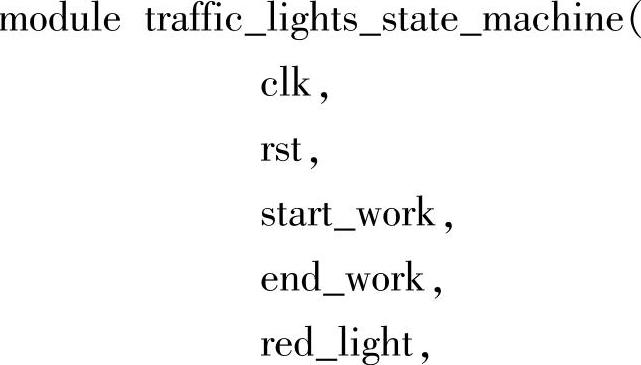

图5.3 Verilog基本结构

1.Verilog基本结构

Verilog模块在工程中以.v的文件形式存在,在每个.v文件中都定义了一个功能模块(module),其基本结构如图5.3所示。

图5.3中,第一行语句module用来声明一个模块,它与endmodule配套使用,endmodule在代码最后一行,表示代码的结束,module声明后面跟着模块的名称,名称后面跟着端口列表,在端口列表中需要列出该模块的输入输出端口名,在接下来的端口定义中对端口的位宽进行说明,在数据类型说明中需要用reg和wire型声明output型端口,reg和wire类似于C语言中用int之类去定义数据类型,reg型指数据类型为寄存器型,wire型指数据类型为线型,紧接着就是模块功能的描述,这部分由组合电路和时序电路共同组成,在输入信号的激励下,经过组合电路和时序电路的处理将信号输出,完成一个基本模块的编写。

当模块的上一层调用这个模块的时候,需要将该模块例化,生成该模块的调用实例,将该模块端口与其他各模块端口一一对应,例化的方法如图5.4所示。

图5.4 模块例化

其中,调用的模块名称是module_A,引用该模块时将其命名为module_A_inst,即module_A_inst是模块module_A的实例引用名。

2.门级描述与行为级描述

门级描述和行为级描述都是用在图5.3中“功能描述”的那部分,都是完成功能描述的方式。所谓门级描述,就是利用门器件完成功能描述,如:与门(and),或门(or),非门(not),异或门(nor)等,它们都可以在代码中直接引用,如图5.5所示。

图5.5 门级描述示例

其中,a1和a2为与门“and”的实例化名称,此句表示将输入datain1和da-tain2相与输出到out1,将datain3和datain4相与输出到out2。如上所述,图5.5中通过改变实例化名称(a1、a2、…)将与门“and”多次例化,实现与门模块的重复利用。

所谓行为级描述,就是用Verilog自身的语言去实现功能,没有现成的门器件,取而代之的是always块、if语句、case语句等,if、case等比较好理解,与C语言功能一样,always块是Verilog语言所独有的、并且大面积使用的表达方式,如图5.6所示。

第一句表示当时钟信号clk的上升沿或者复位信号rst的上升沿出现时,触发always块下面的语句执行,第二句表示当信号A、B、C中至少有一个发生变化时,触发always块执行其下面的语句,第三句表示当always块下面的语句中用到的所有条件信号,比如if语句中的条件,case语句中的条件等,至少有一个发生变化时,触发always块。上面只是行为级描述的一个简单例子,所有用自身语言实现的描述都可以统称为行为级描述。在行为级描述中,有的语句是可以综合的,也就是说能用工具翻译成门级网表,这些语句又称为RTL级描述,在我们的设计中,最终目的都是将设计变成电路,所以都必须是可综合的,因此都要使用RTL级描述,除了部分只用于仿真的代码,不用考虑其可综合性,关于可综合,会在后面做详细介绍。

在电路规模较小的情况下,可以用门级描述去实现,此时电路门数少,直接用门级描述使得电路结构清晰,便于综合。然而,随着功能的强大,电路复杂度的提高,很难用简单的门级结构去分析和描述其功能,容易造成错误,这时用行为级描述就简单易懂,用语句去实现,而不是自己去搭电路,把搭电路的工作留给后续的综合工具,而我们只需要了解语法,并组织起来,所以,行为级描述比门级描述对于机器来说抽象层次更高,对于人来说更通俗易懂,可以显著地提高设计效率。

图5.6 always块

3.组合逻辑与时序逻辑

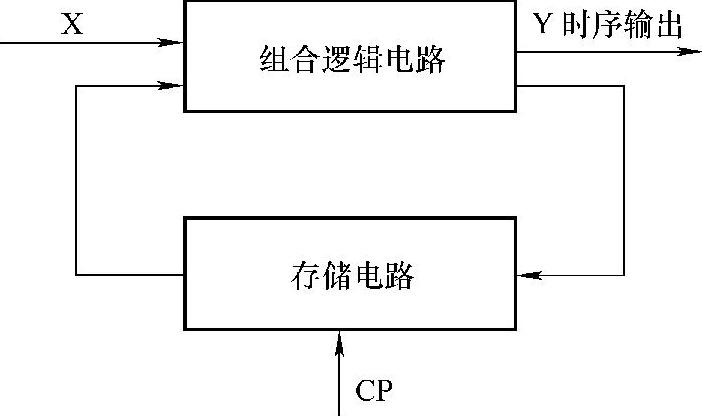

前面已经多次提到组合逻辑与时序逻辑,它们是数字电路设计的血肉。它们最大的区别就是时钟,组合逻辑中只有逻辑和符号运算,没有时钟的控制,而时序逻辑都是在时钟的控制下进行逻辑和符号运算,因此,当组合逻辑遇上时序逻辑,组合逻辑在电路中容易出现竞争冒险现象,信号产生毛刺,埋下不稳定的地雷。它们的关系如图5.7所示。

图5.7 组合逻辑与时序逻辑关系

组合逻辑通常使用assign语句和always块实现,如图5.8所示。

图5.8中,变量c的类型为wire型,在assign语句中被赋值的变量必须定义为wire型,c相对于a、b没有延迟,当a、b发生变化时,c即刻跟随a或者b发生变化,上述语句也可以通过always块实现,如图5.9所示。

图5.8 assign语句实现组合逻辑

图5.9 always语句实现组合逻辑

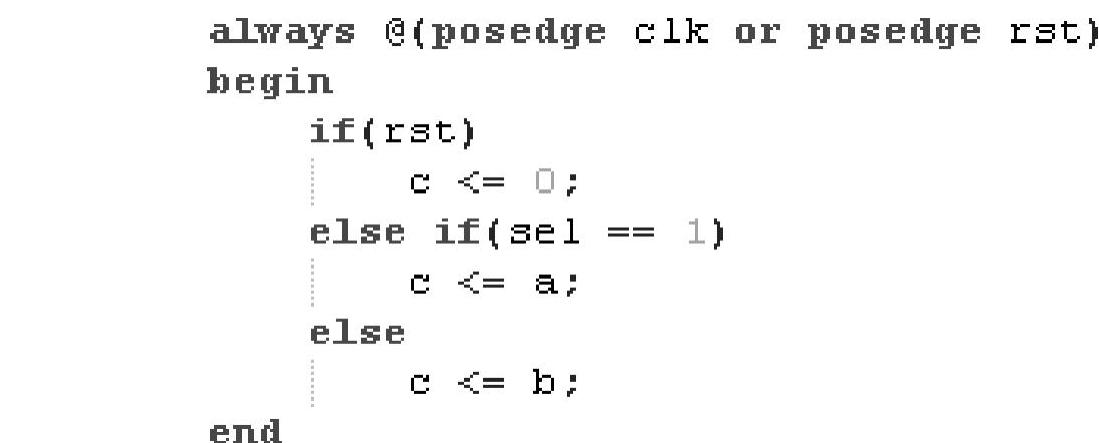

图5.8与图5.9表达的意思相同,它们都是组合逻辑的表现形式,c的输出与时钟没有关系,不管是在时钟的上升沿或下降沿或中间某个位置,只要a、b或sel中至少一个发生变化,c就会在同一时间跟随a或者b发生变化。时序逻辑也是通过always语句来实现,但其过程却截然不同,如图5.10所示。

图5.10 时序逻辑

图5.10中,当时钟的上升沿(posedge clk)或者复位信号的上升沿(posedge rst)到来时才执行always块里面的代码,这就意味着c的输出与时钟沿是同步的,它是在每个时钟沿去判断sel,并根据sel选择输出a或者b,所以c会比a或者b的变化要晚一个时钟周期,由于c要受时钟沿的控制,所以在后续将代码映射成电路的过程中(即综合),可以通过控制时钟来达到控制c的目的,起到保证c能正确输出的作用,而不会采到亚稳态值,组合逻辑就无法控制,所以时序逻辑比组合逻辑的可控性更强。在数字电路设计中,对于异步时钟的输入信号都会做同步处理,即用本地时钟做握手,可以通过寄存器打两拍,也可以通过存储介质隔离一下,以保证模块采集到的输入信号是正确的;模块输出时也采用时序逻辑输出,保证输出的信号跟时钟同步,便于做管理和约束,关于约束在后续章节中会有详细介绍,这里不再赘述。

虽说组合逻辑容易产生毛刺,电路不稳定,但在实际的电路设计中,很难用时序逻辑完全取代组合逻辑,需要二者相互配合,将组合逻辑有效的穿插在时序逻辑间,通过约束时钟达到管理时序逻辑,携带管理组合逻辑的目的,这样能够合理地提高数字电路设计效率,实现电路设计的功能。两者相辅相成,缺一不可。

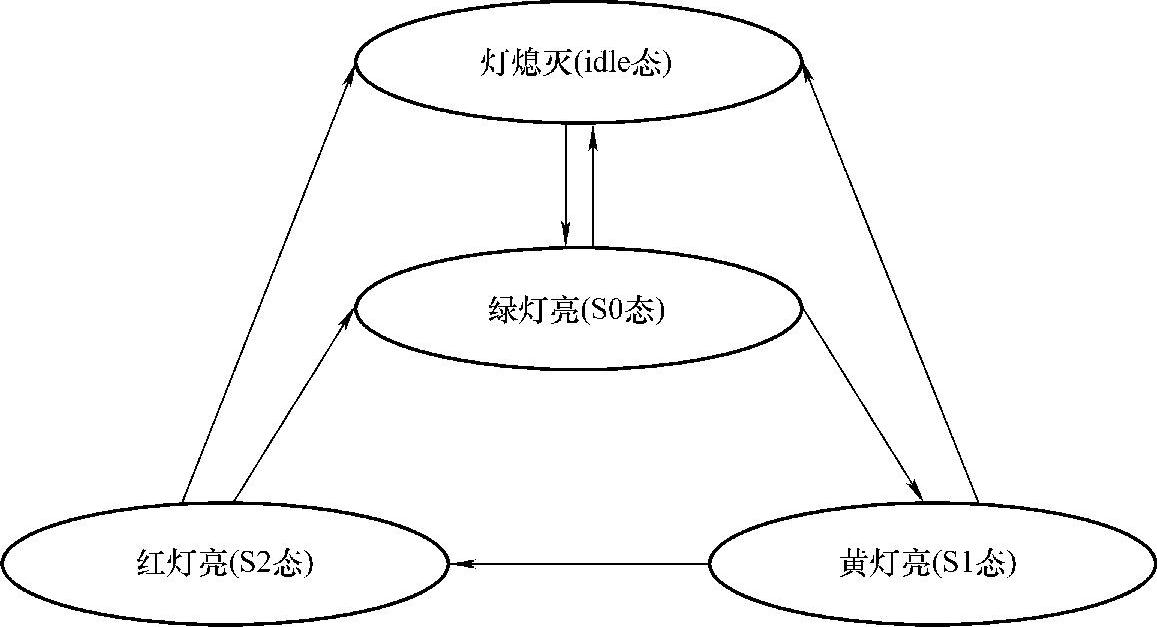

4.状态机

如果说时序逻辑和组合逻辑是数字电路设计的血肉,那么状态机就是数字电路设计的灵魂。所谓,灵魂和血肉,总有一个在路上。在数字电路设计中,总会用到它们,不离不弃,难舍难分。状态机,就是一个有多种状态的机器,根据自己的节奏,有条不紊地运转,在每个状态完成一件或几件事情,这个完成的事情就是我们需要的输出,这个控制节奏的砝码就是我们得到的输入。状态机的优势在于能大大提高数字电路的稳定性和可靠性。

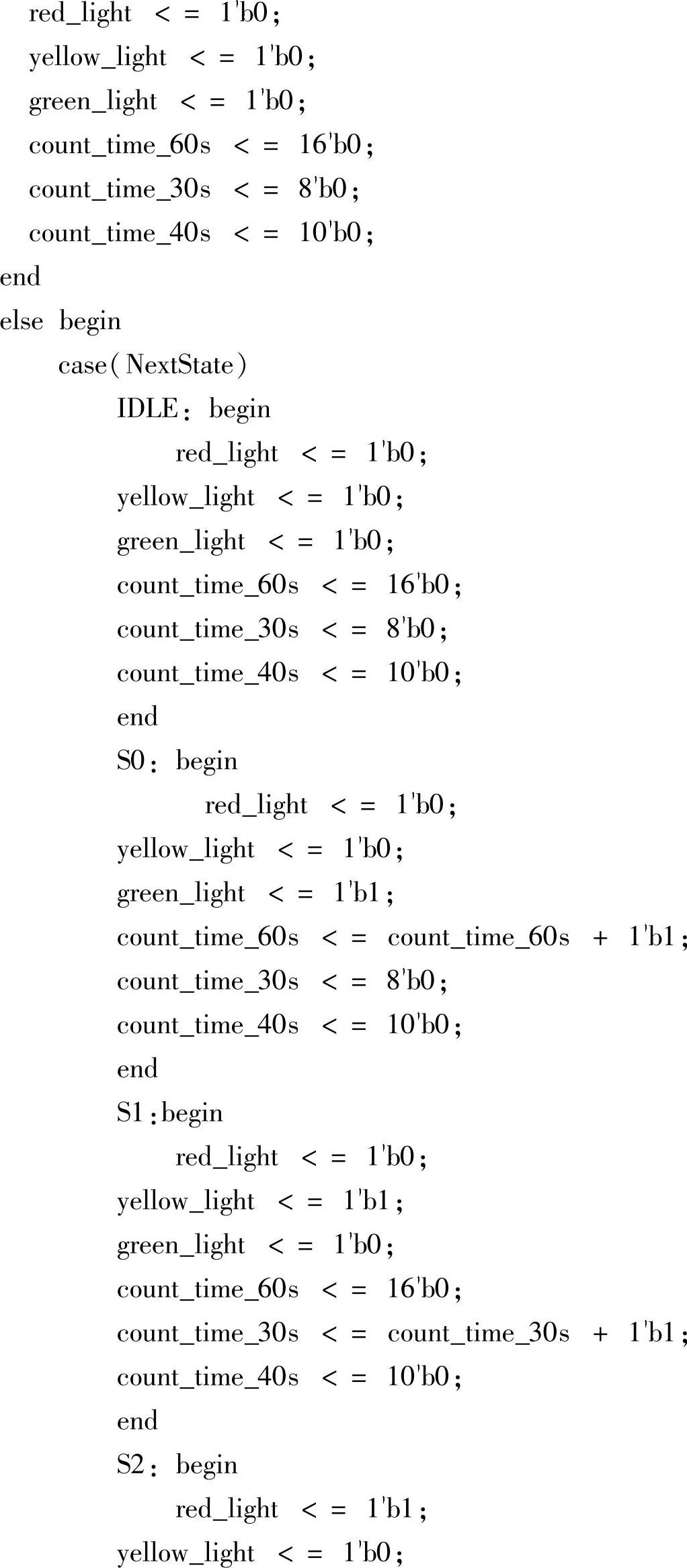

状态机的设计,首先要提取状态机的要素,即需要几个状态,各个状态之间的联系;其次是状态编码,就是给每个状态一个编号,最好用独热码,有利于综合工具进行优化,否则在综合时,综合工具可能自动将其转换为独热码;最后就是状态机的功能,就是每个状态需要干的事情,举个例子来说明状态机,比如交通灯控制,将其划分为如下几个状态,如图5.11所示。

图5.11 状态机示例

起初交通灯是熄灭的(idle),当早上6点交通灯开始工作,此时进入绿灯亮状态(S0),绿灯亮60s,进入黄灯亮状态(S1),黄灯亮30s,进入红灯亮状态(S2),红灯亮60s,再次进入绿灯亮状态(S0),当晚上10点,无论这时是绿灯亮(S0)、黄灯亮(S1)还是红灯亮(S2),交通灯都要关闭,回到灯熄灭状态(idle)。代码如例5.1所示。

例5.1 交通灯状态转移代码

例5.1中采用经典三段式状态机描述交通灯的控制过程,第一个always块由组合逻辑描述状态转移过程,第二个always块由时序逻辑描述各个状态下信号的输出情况,状态跳转没有时钟延迟,当输入条件变化,状态即刻变化,输出信号在各个状态下用时钟输出,保证输出信号的可约束性和稳定性,两者相互结合,大大地保证了电路的可靠性和实效性。所以,笔者认为在数字电路设计中状态机的描述使得代码逻辑更清晰,结构更合理,状态更稳定,是值得推荐的描述方式。

有关CMOS集成电路EDA技术的文章

表5.14-2 编码器真值表表5.1中,“x”表示不定位,可以是“0”,也可以是“1”,根据真值表写出Verilog实现代码,如例5.2所示。例5.2 4-2编码器示例主要使用casex语句实现编码过程,其测试文件如例5.3所示。例5.3 4-2编码器测试文件编码结果如图5.12所示。例5.5 四分频器测试代码仿真结果如图5.13所示。......

2023-06-26

算法的描述方法主要有如下几种。例如,用传统流程图表示的顺序结构如图3.2所示,用NS图表示的顺序结构如图3.2所示,表示先执行A操作,再执行B操作,两者是顺序执行的关系。......

2023-11-20

流体力学主要是研究流体在静止或流动时性质变化以及流体流动时对流场内的物体造成的影响,因此在式学习流体力学前必须对流体的性质与速度有一定的认识,才能对后续的学习内容有清楚而完整的认识。显然,流体的比容ν为流体的密度ρ的倒数,并可表示为。......

2023-06-29

PLC的编程语言一般有_______、_______、_______等。PLC 按结构形式划分主要有_______和_______两种。PLC 中输入和输出信号的数量,也就是输入、输出端子数总和称为______________。PLC的输出形式一般分为______________、______________和______________三种形式。A.1967年B.1968年C.1969年D.1970年PLC 控制系统能取代继电-接触器控制系统的()部分。A.8B.16C.4D.2在对PLC 进行分类时,I/O 点数为()点时,可以看作是大型PLC。简述PLC的主要特点。......

2023-06-27

④如何限制某一源程序文件中定义的变量在同一C程序的其他源程序文件中的使用。变量的作用域和生存期是两个相互联系而又有本质区别的不同概念,它们的基本意义如下:①一个变量在某个复合语句、某个函数、某个源程序文件或某几个源程序文件范围内是有效的,则称其有效的范围为该变量的作用域,在此范围内可以访问或引用该变量。......

2023-11-20

作为礼仪的一个组成部分,公共礼仪既有礼仪的共同特征,又具有个性特征。而在公共场所发生的人际交往中,人们都是以一半的社会成员身份出现的,所以公共场所发生的人际交往就不再有这些辈分、职务方面的差别,每个人都是具有同样交际身份的社会“游客”。一个人无论来自什么阶级、阶层,只要他到电影院观看电影,就只是一个观众;到公园游览,就只是一个游客;上了公交工具,就只是一个普通乘客。......

2023-08-11

口头语言与文字语言是两种不同的语言形式。书面语言应当注重文字规范和文字修饰,适应人们阅读的需要。同样,把口头语原封不动地搬到书面语言中,也不符合书面语言的规范要求。比如同样写“狗”,在不同的文体中,语言的要求各不相同。说明文中的语言,抓住狗的特点,语言通俗明白。论说文的语言,深刻犀利,鲜明准确,严谨,概括性强。......

2023-10-23

相关推荐