【摘要】:下面详细介绍采用Calibre工具对版图进行LVS检查的流程,并示出几处修改LVS错误的方法。本节采用内嵌在Virtuoso Layout Editor的菜单选项来启动Calibre LVS。Calibre LVS的使用流程如下:1)启动Cadence Virtuoso工具命令icfb,弹出命令行窗口,如图4.62所示。图4.68 Calibre LVS中Inputs菜单Netlist选项卡对话框8)选择左侧菜单中的Outputs,可以选择默认的设置,同时也可以改变相应输出文件的名称。图4.79 Calibre LVS通过界面以上完成了Calibre LVS检查的主要流程。

下面详细介绍采用Calibre工具对版图进行LVS检查的流程,并示出几处修改LVS错误的方法。本节采用内嵌在Virtuoso Layout Editor的菜单选项来启动Calibre LVS。Calibre LVS的使用流程如下:

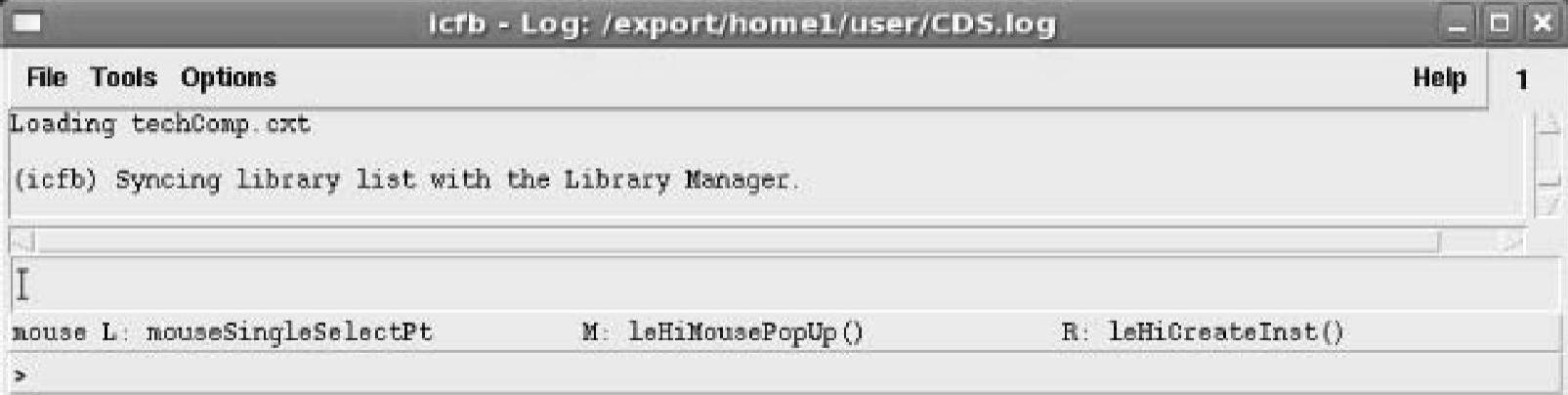

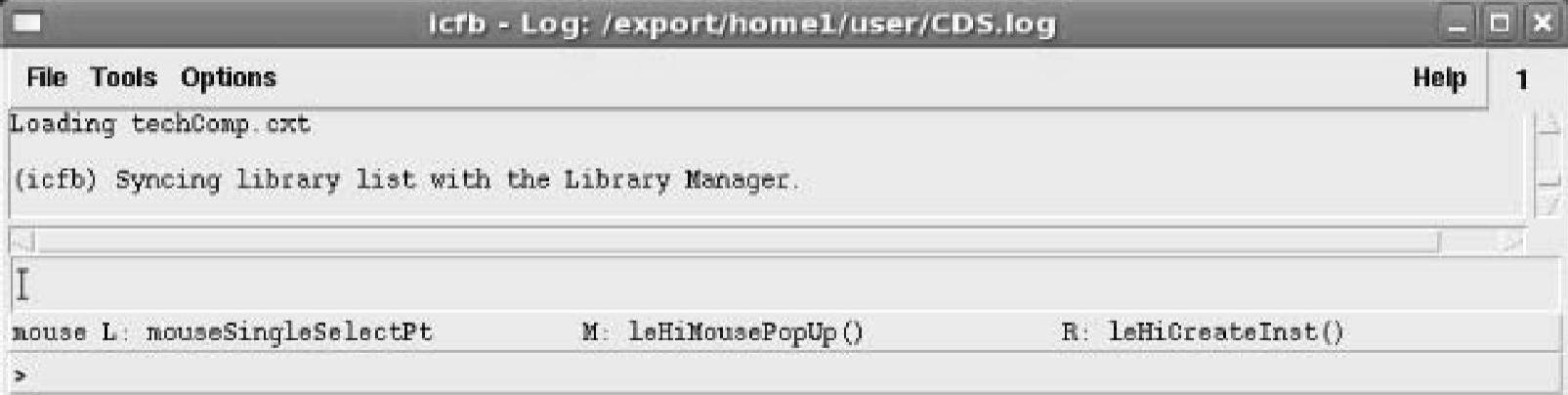

1)启动Cadence Virtuoso工具命令icfb,弹出命令行窗口,如图4.62所示。

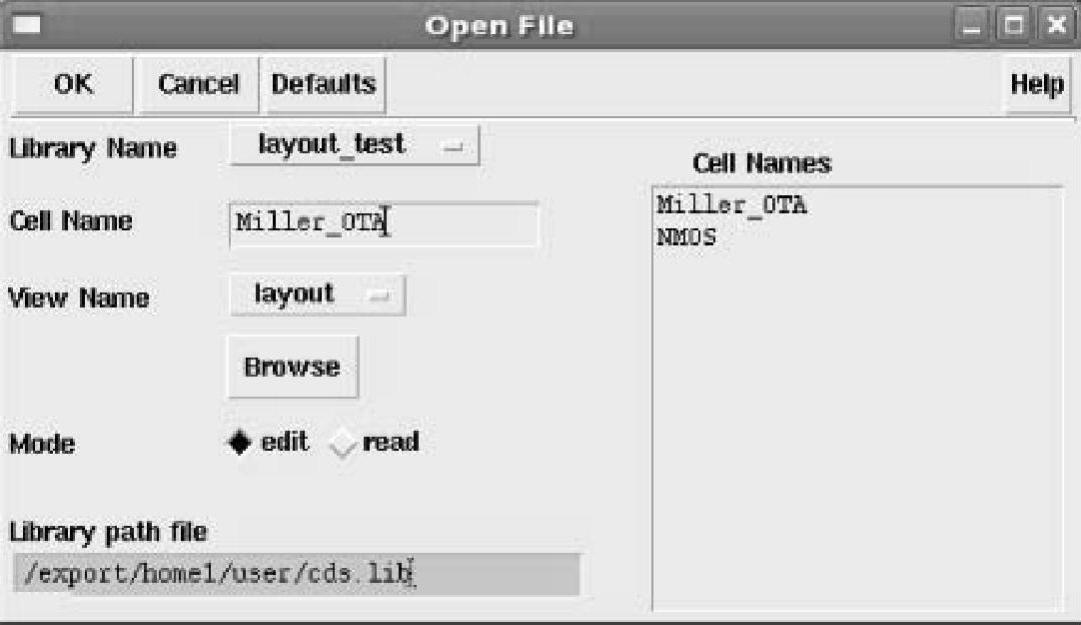

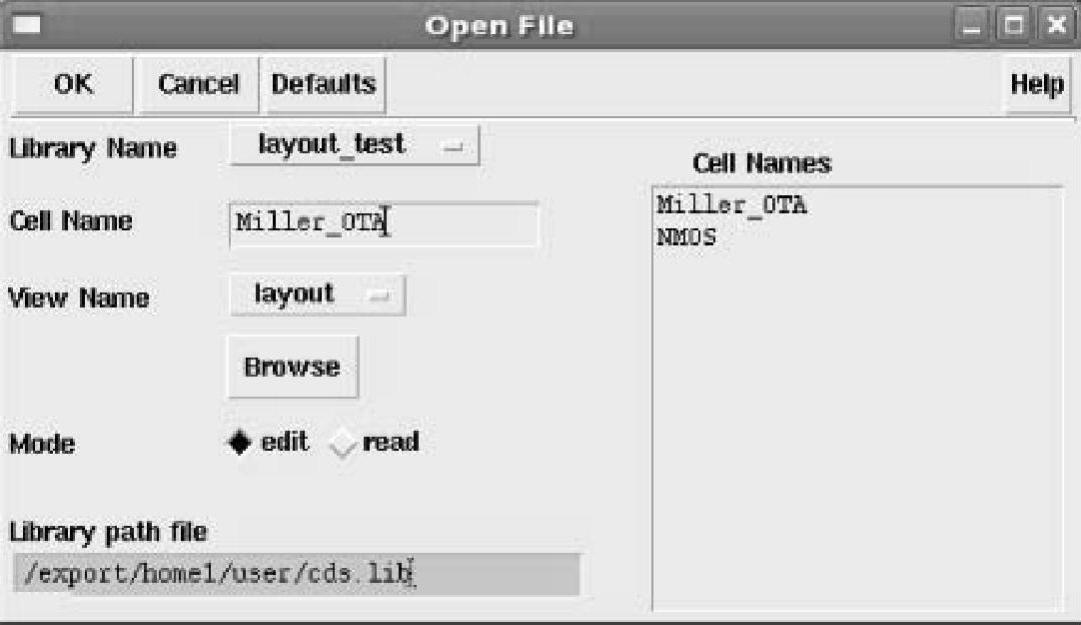

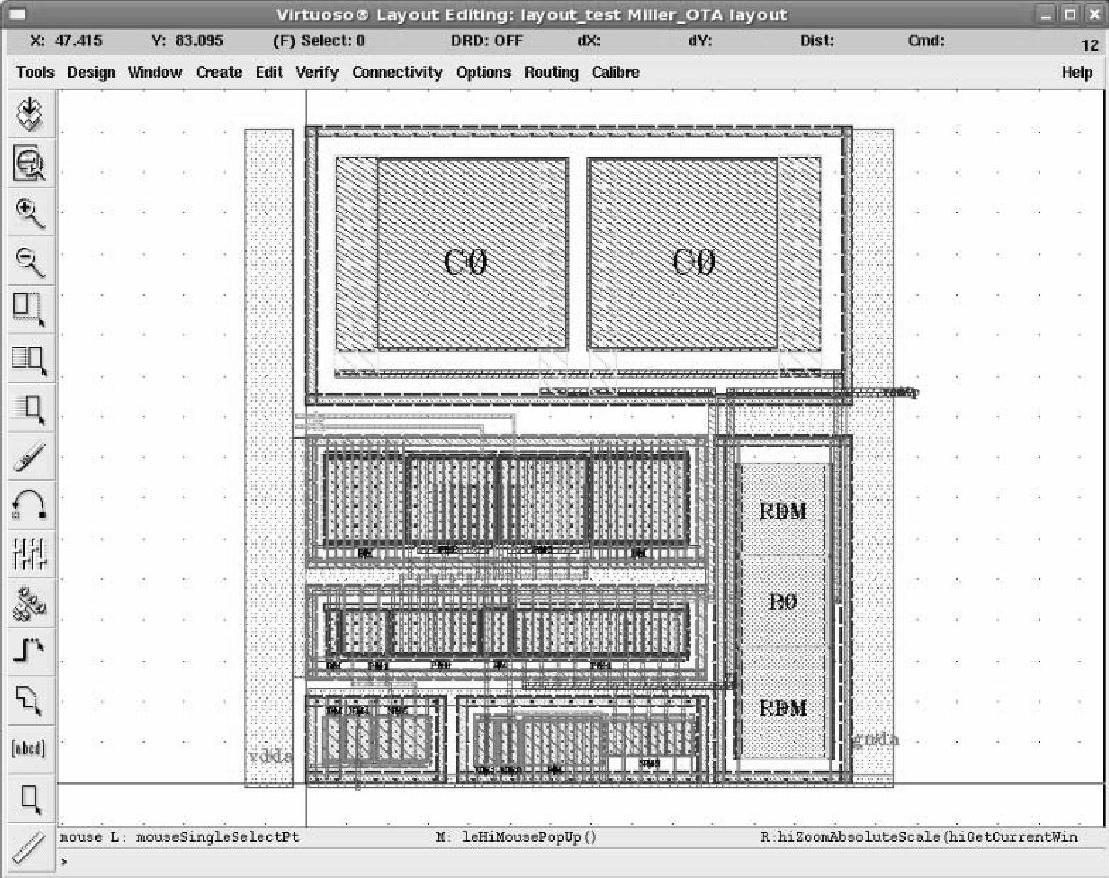

2)打开需要验证的版图视图。选择File→Open,弹出打开版图对话框,在“Library name”中选择“layout_test”,“Cell Name”中选择“Miller_OTA”,“View Name”中选择“layout”,如图4.63所示。

图4.62 命令行窗口

图4.63 打开版图对话框

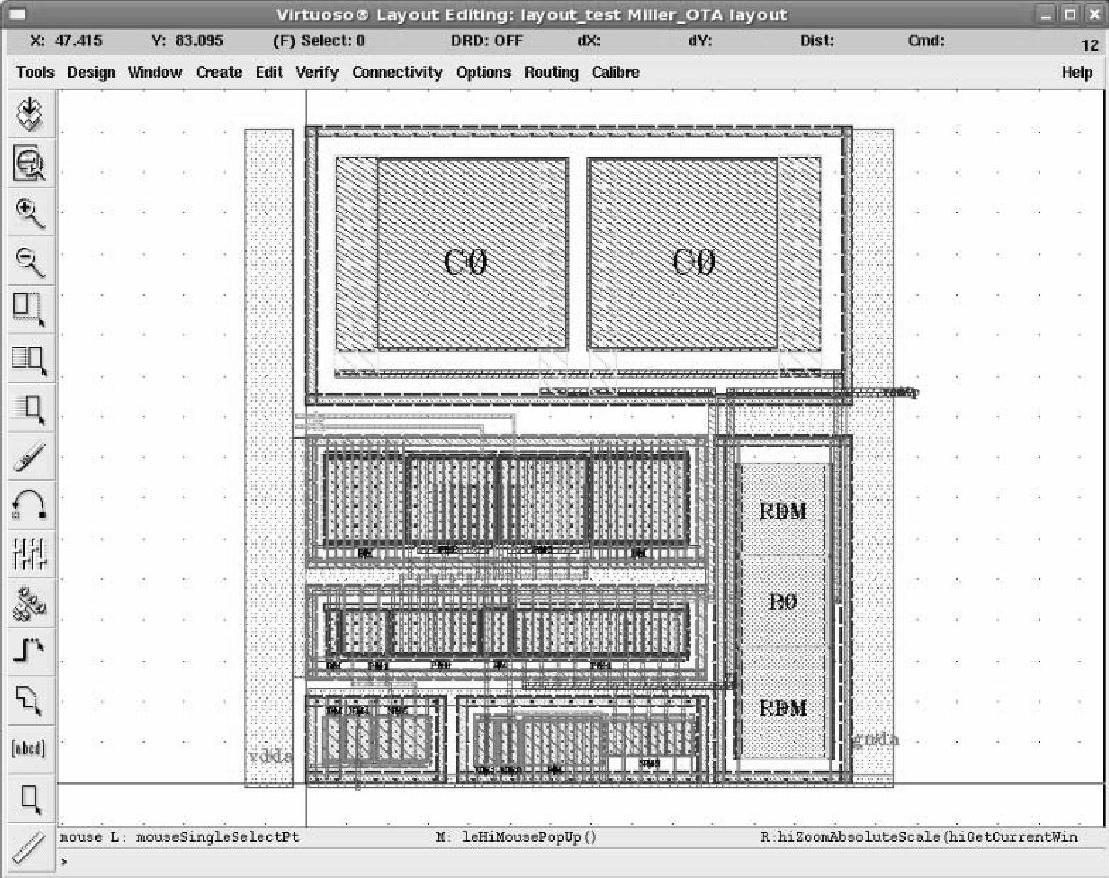

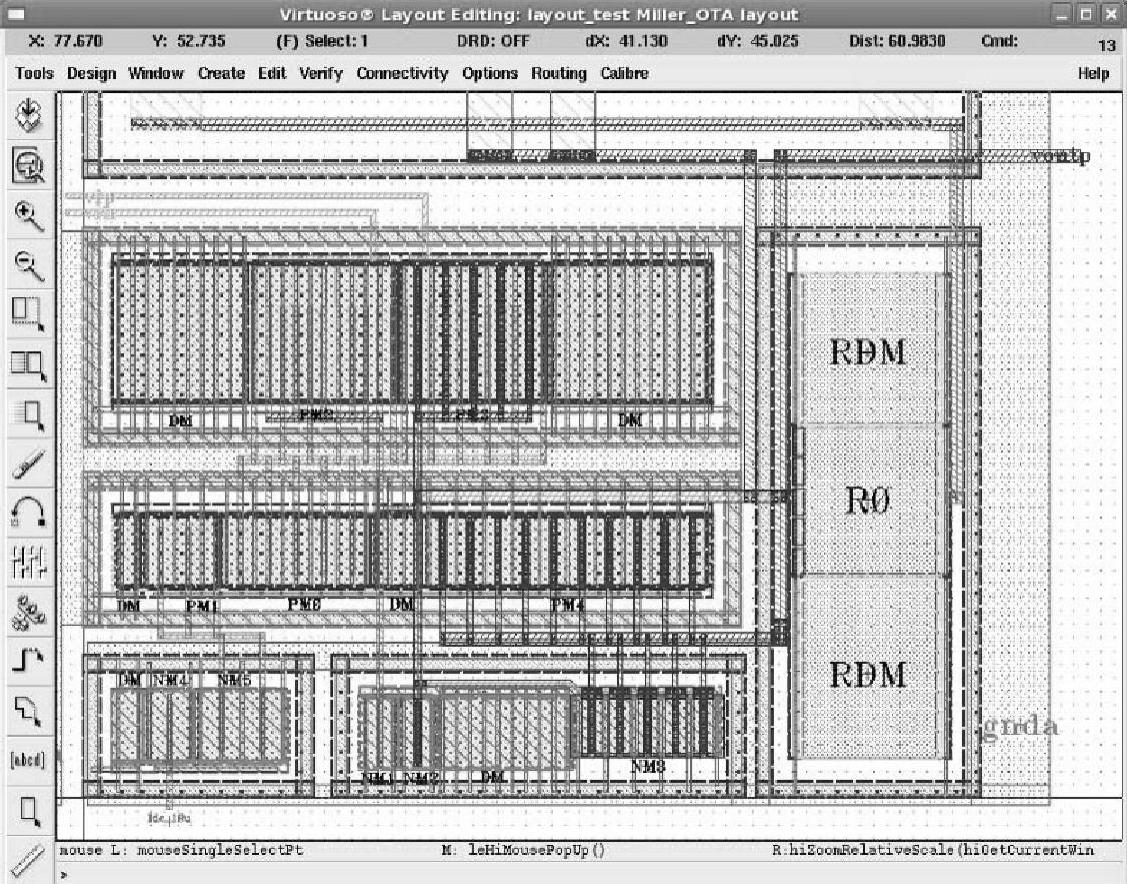

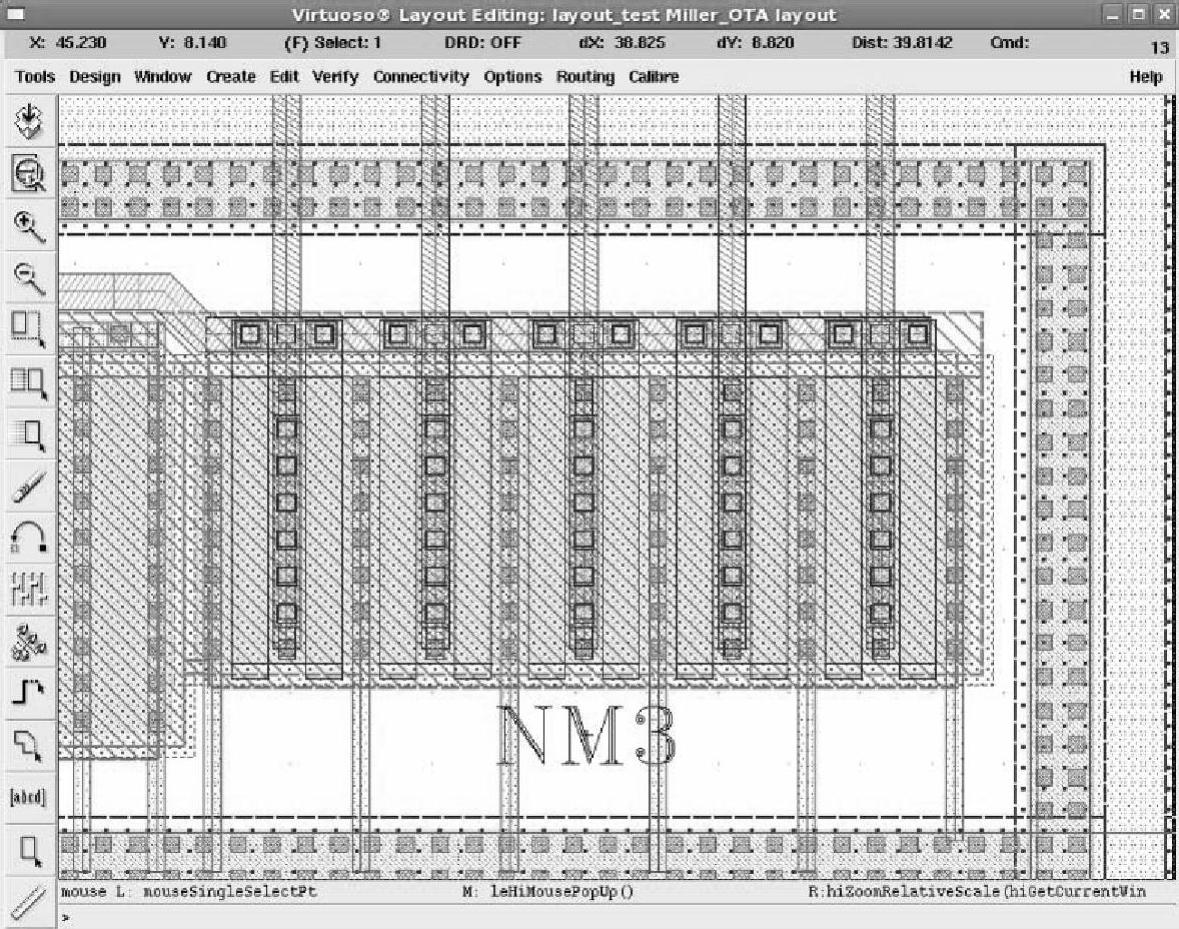

3)单击“OK”按钮,弹出Miller_OTA版图视图,如图4.64所示。

图4.64 打开Miller_OTA版图

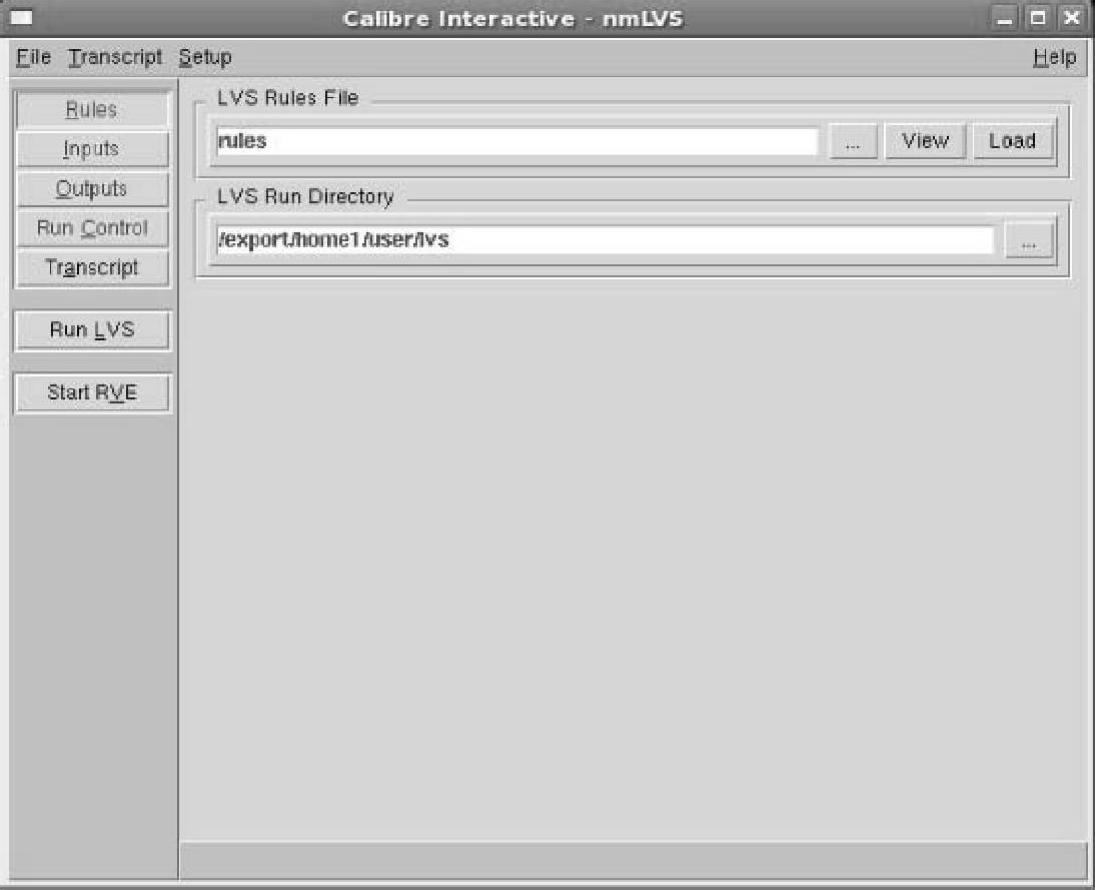

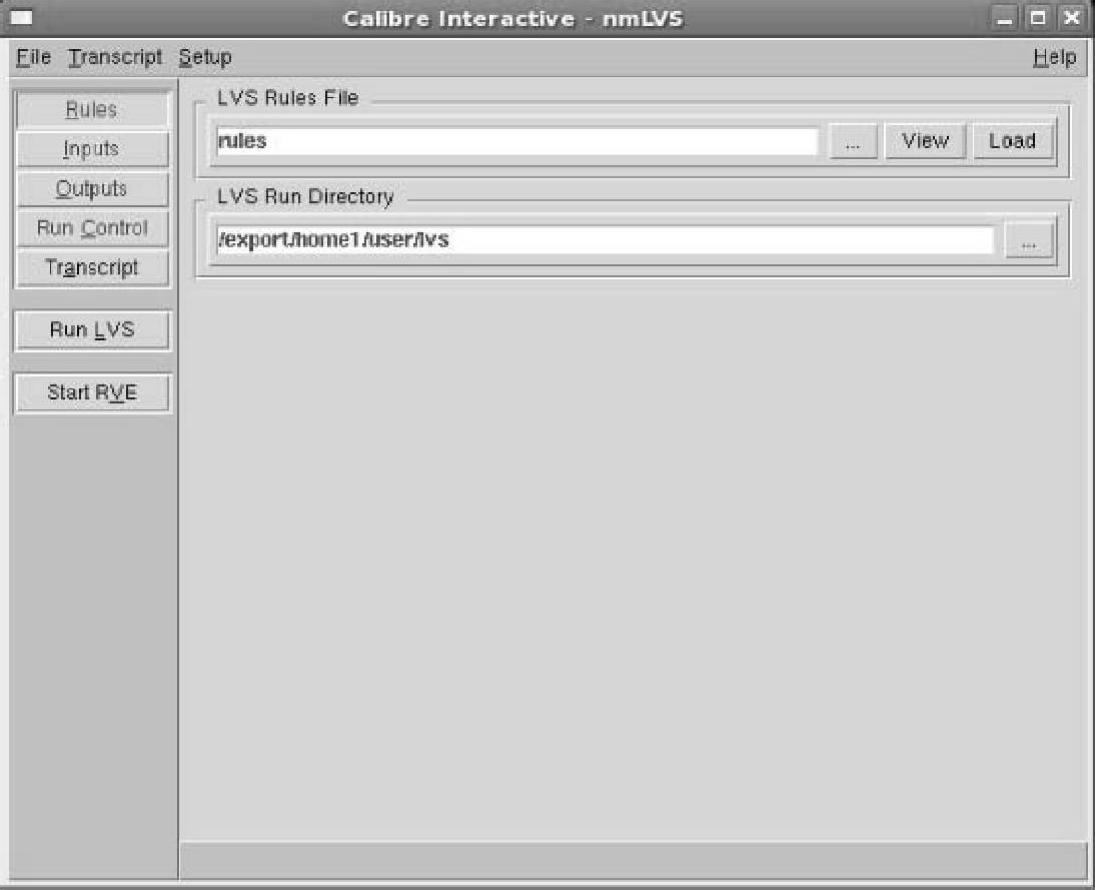

4)打开Calibre LVS工具。选择Miller_OTA的版图视图工具菜单中的Calibre→Run LVS,弹出LVS工具对话框,如图4.65所示。

图4.65 打开Calibre LVS工具

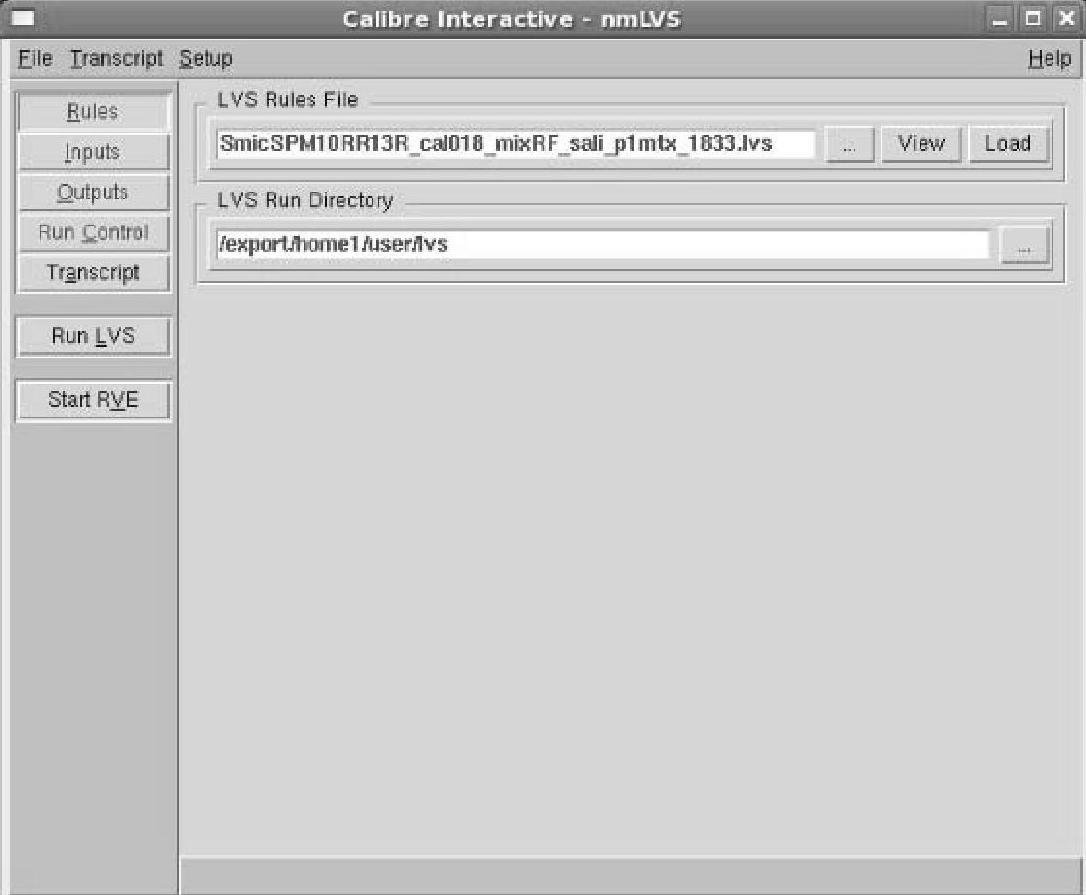

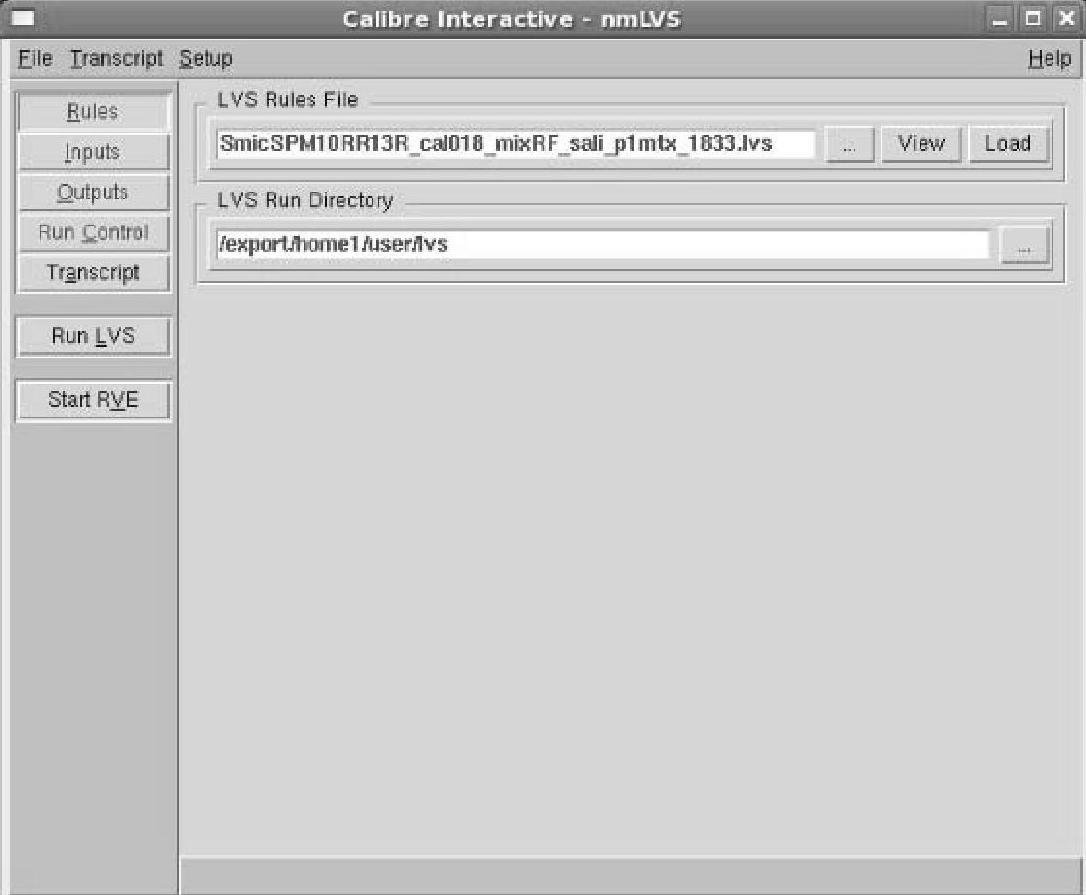

5)选择左侧菜单中的Rules,并在对话框右侧LVS Rules File单击[...]选择LVS规则文件,并在LVS Run Directory右侧选择[...]选择运行目录,如图4.66所示。

图4.66 Calibre LVS中Rules子菜单对话框

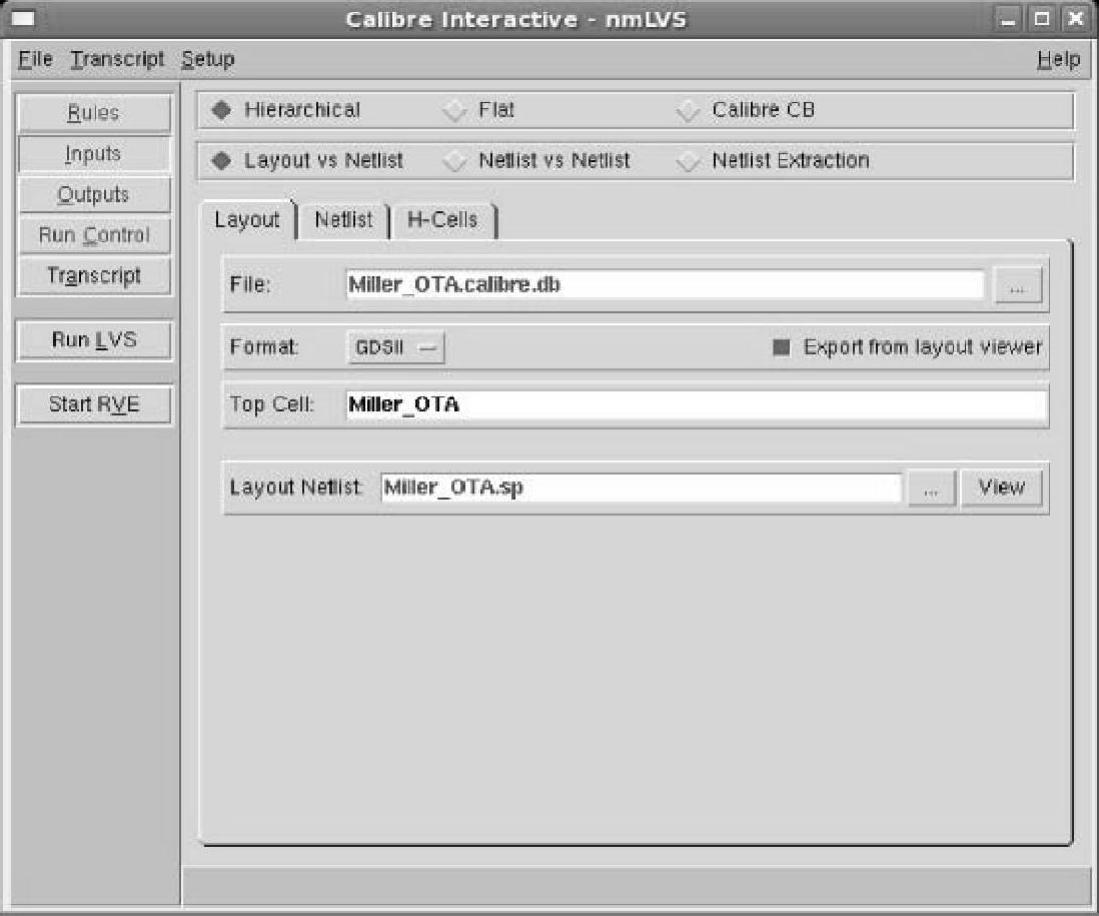

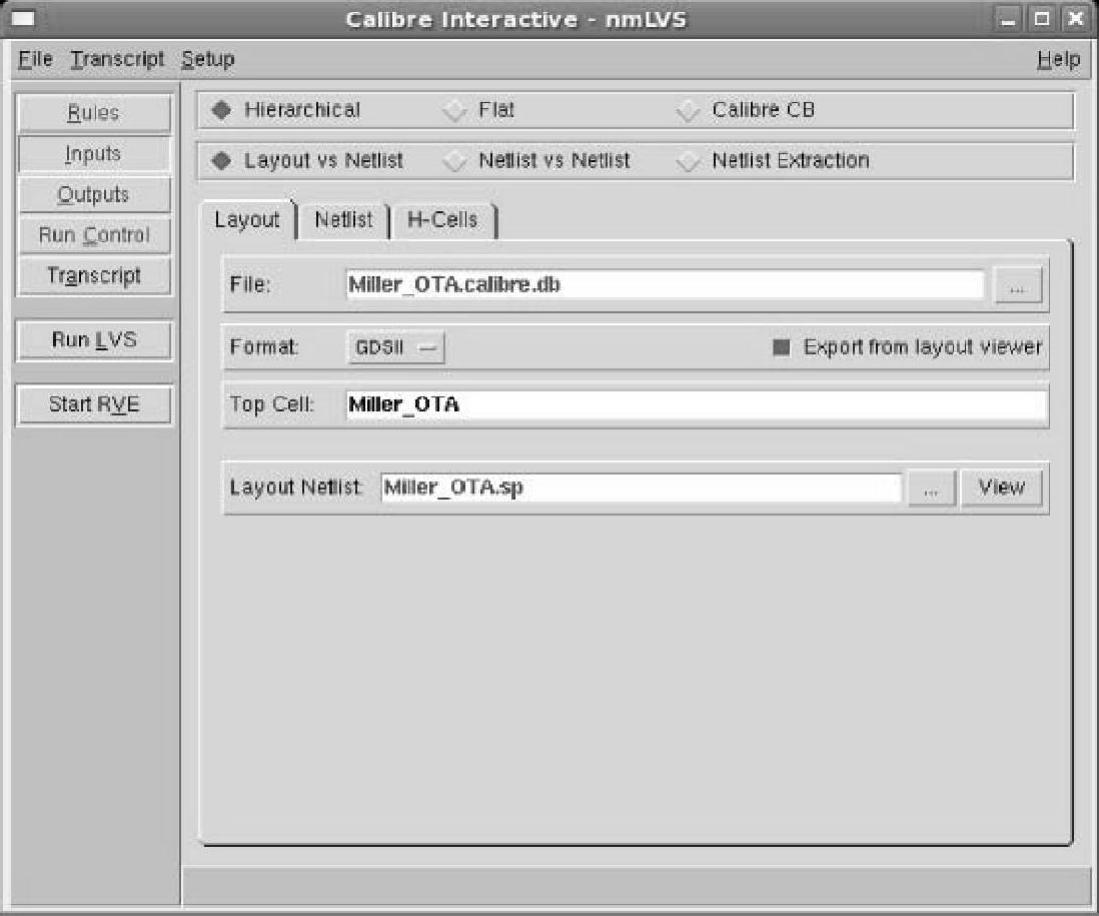

6)选择左侧菜单中的Inputs,并在Layout选项卡中选择Export from layout vie-wer高亮,如图4.67所示。

图4.67 Calibre LVS中Inputs菜单Layout选项卡对话框

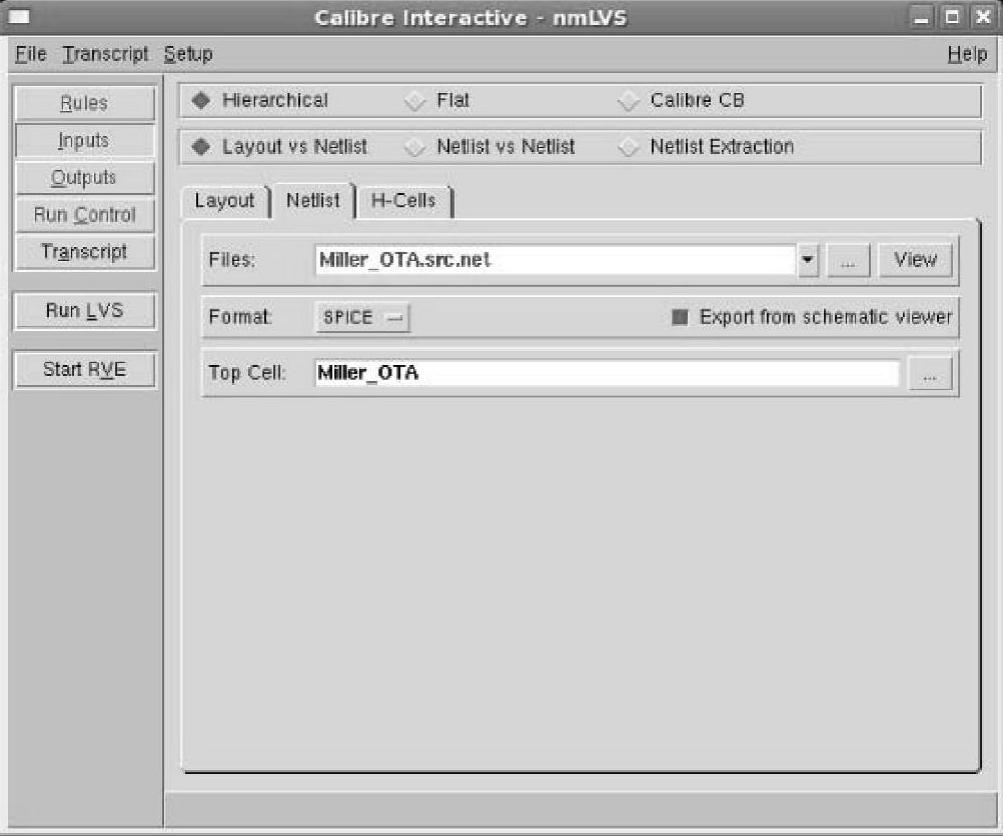

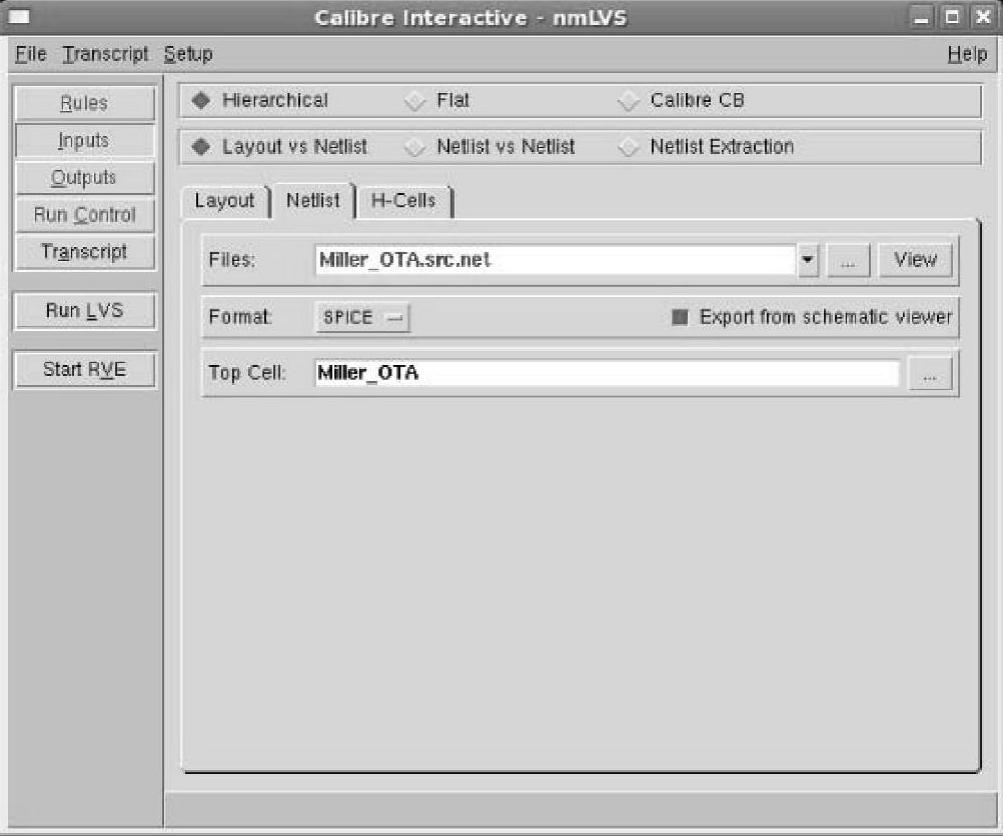

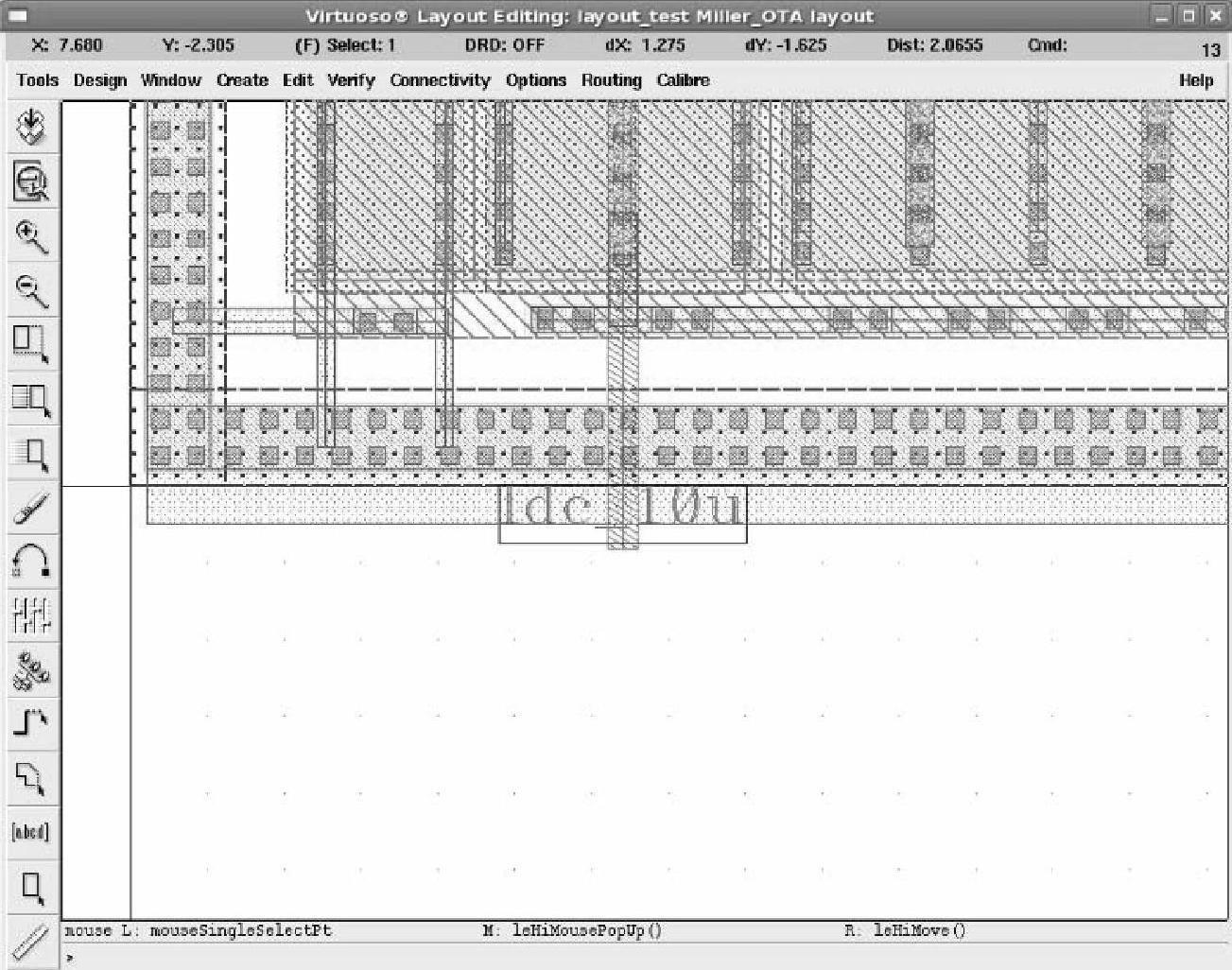

7)再次选择左侧菜单中的Inputs,选择Netlist选项卡,如果电路网表文件已经存在,则直接调取,并取消Export from schematic viewer高亮;如果电路网表需要从同名的电路单元中导出,那么在Netlist选项卡中选择Export from schematic vie-wer高亮(注意此时必须打开同名的schematic电路图窗口,才可从schematic电路图窗口从中导出电路网表),如图4.68所示。

图4.68 Calibre LVS中Inputs菜单Netlist选项卡对话框

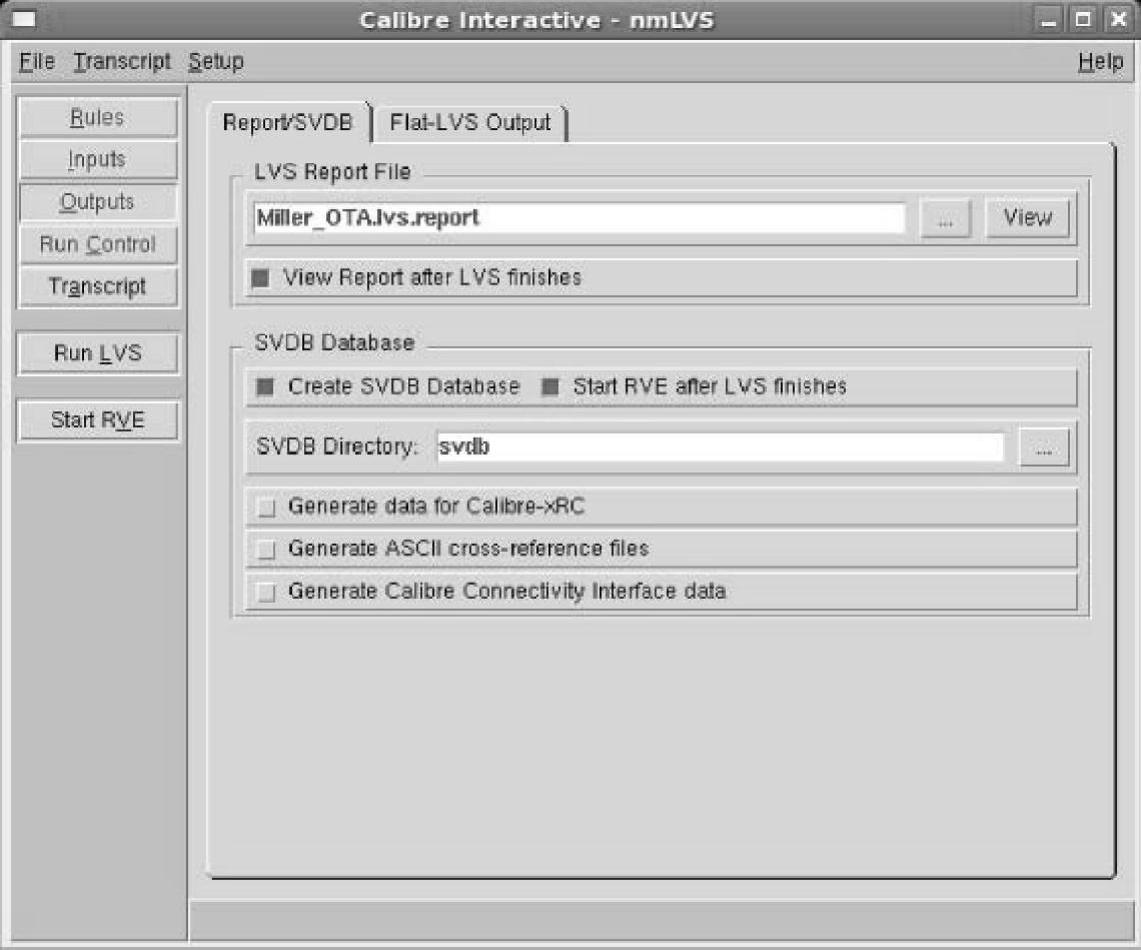

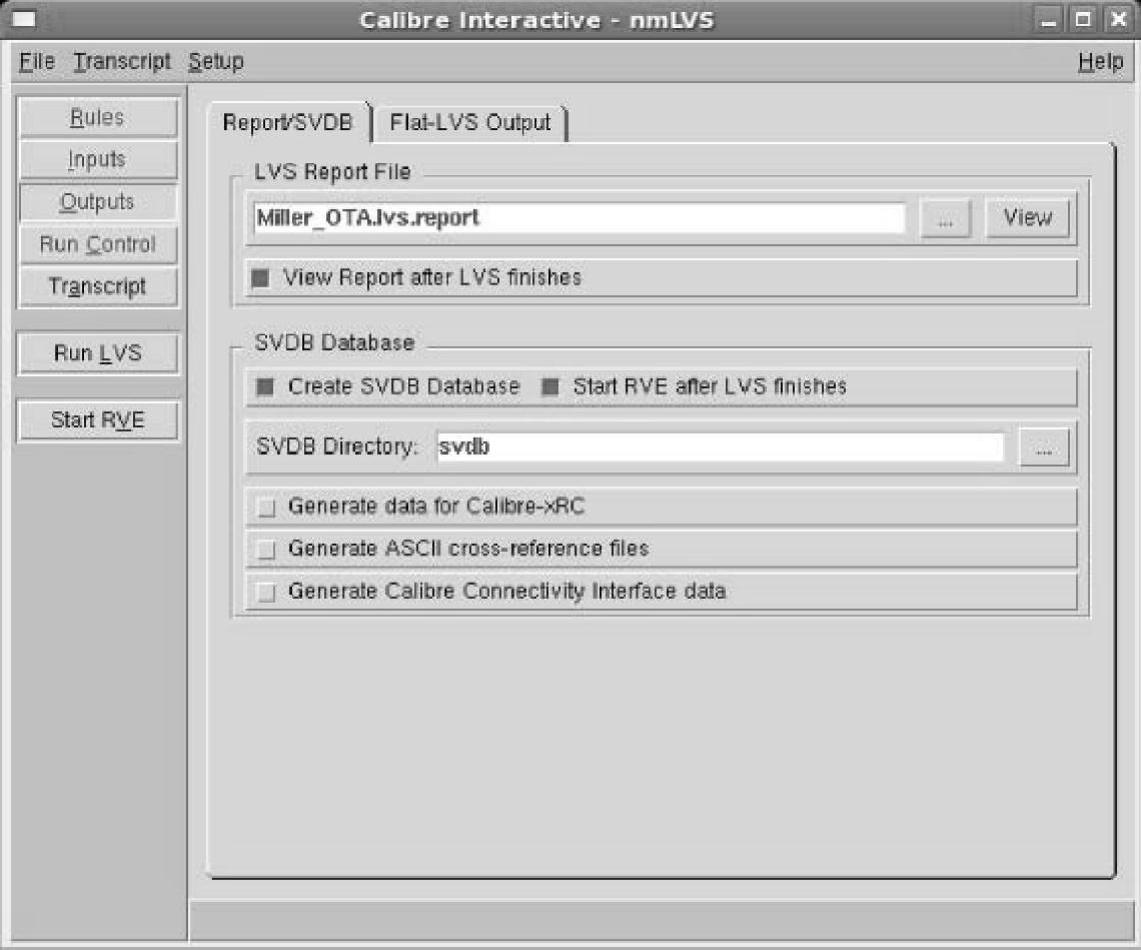

8)选择左侧菜单中的Outputs,可以选择默认的设置,同时也可以改变相应输出文件的名称。选项Create SVDB Database选择是否生成相应的数据库文件,而Start RVE after LVS finishes选择在LVS完成后是否自动弹出相应的图形界面,如图4.69所示。

图4.69 Calibre LVS中Outputs选项卡对话框

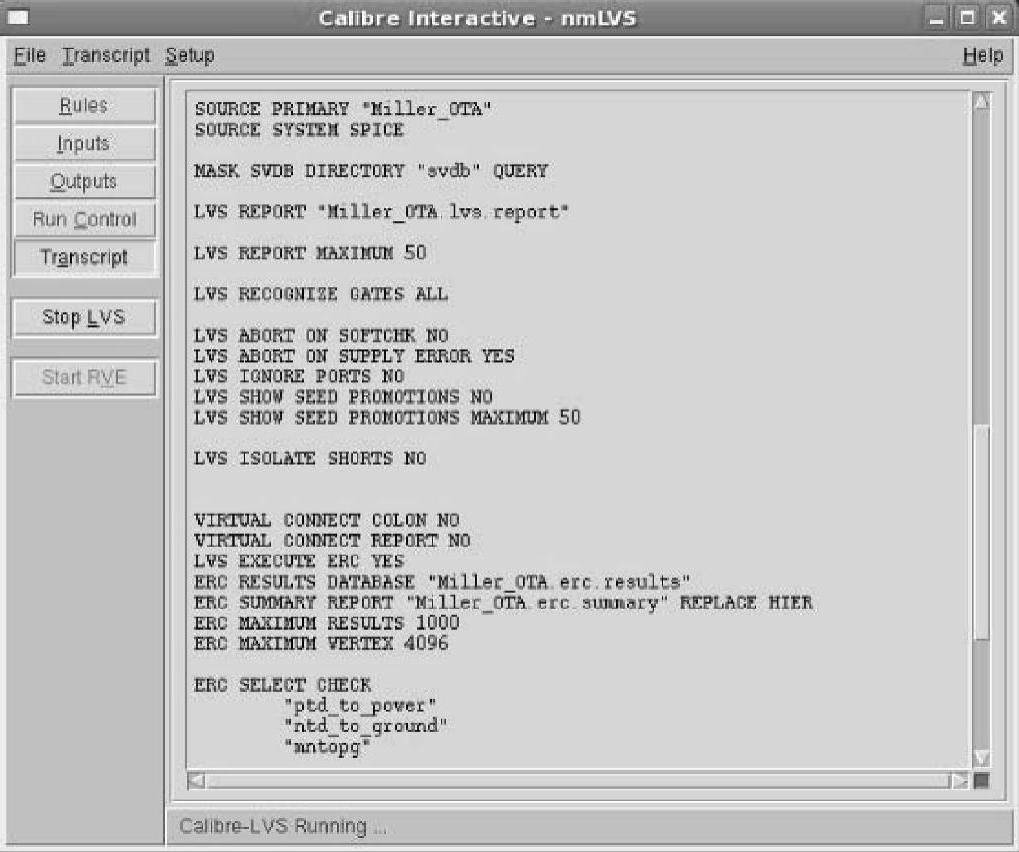

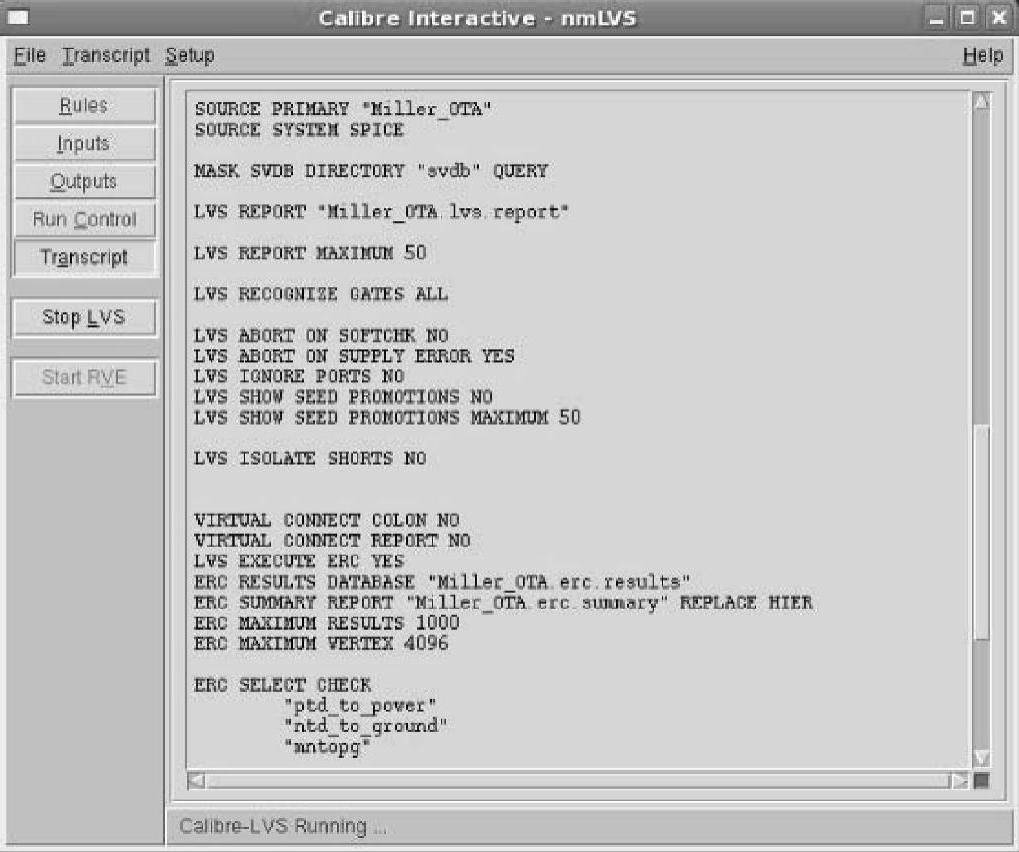

9)Calibre LVS左侧Run Control菜单可以选择默认设置,单击“Run LVS”按键,Calibre开始导出版图文件并对其进行LVS检查,如图4.70所示。

图4.70 Calibre LVS运行中

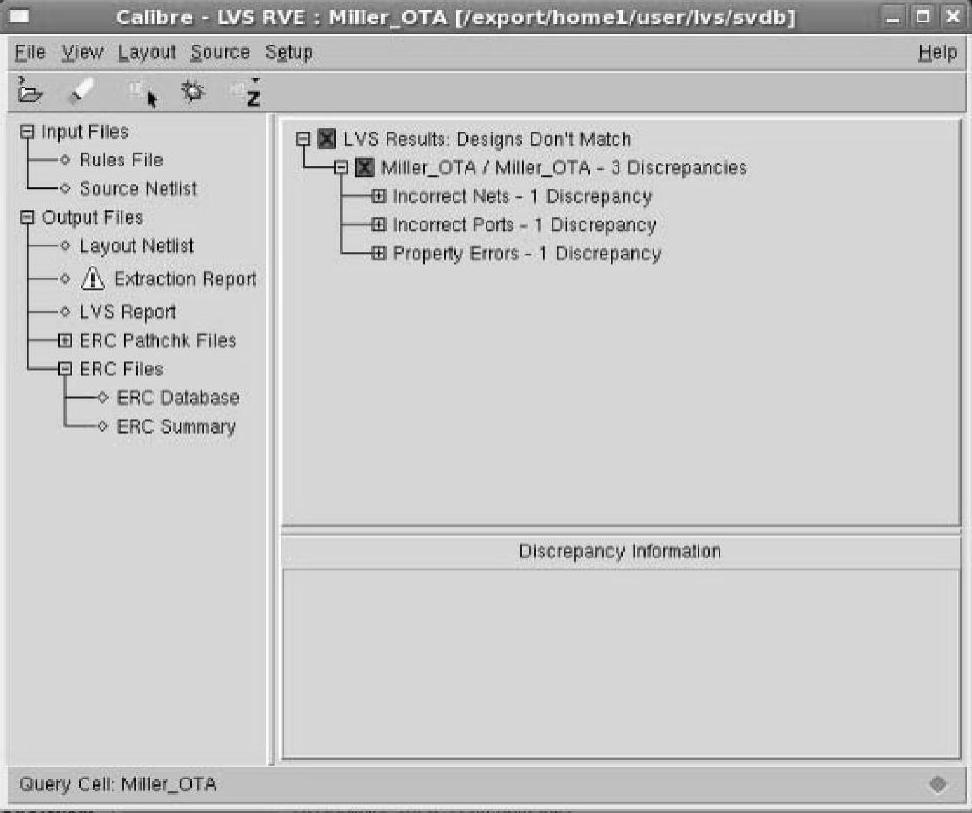

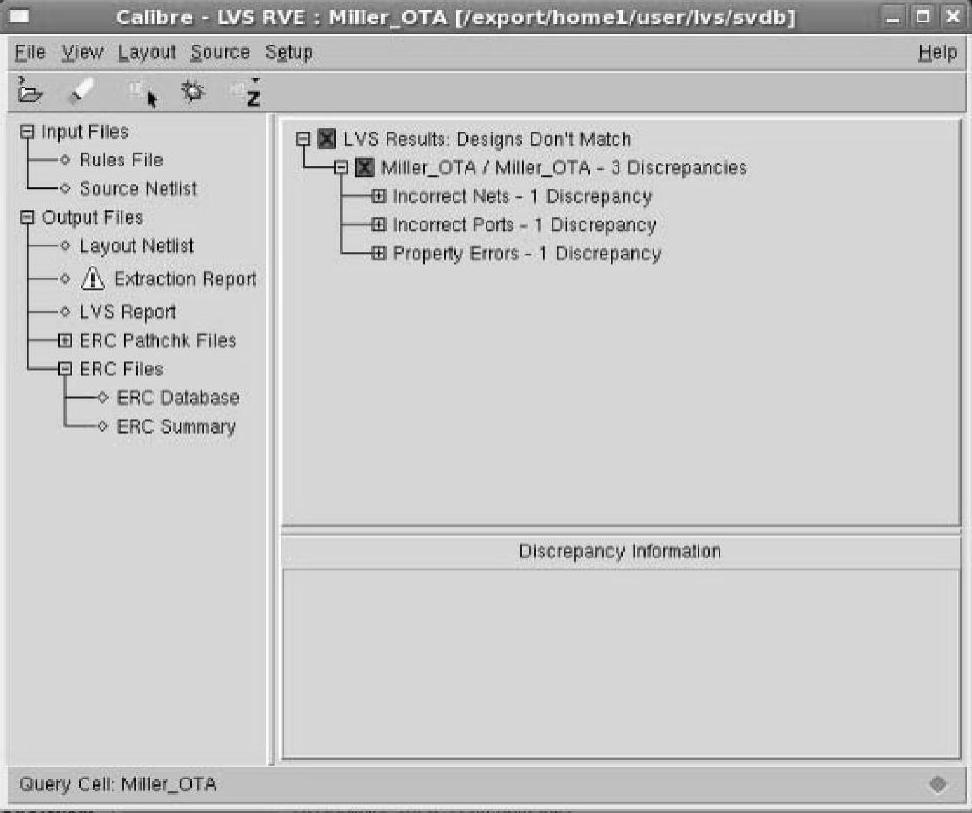

10)Calibre LVS完成后,软件会自动弹出输出结果并弹出图形界面(在Out-puts选项中选择,如果没有自动弹出,可单击“Start RVE”按钮开启图形界面),以便查看错误信息,如图4.71所示。

图4.71 Calibre LVS结果查看图形界面

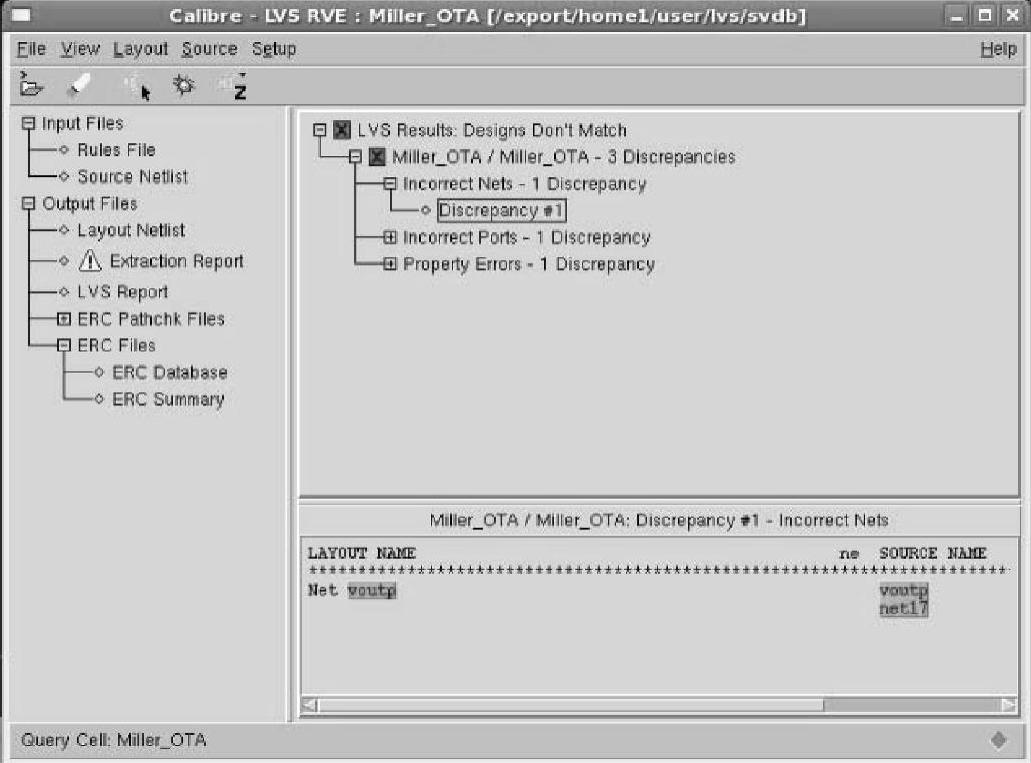

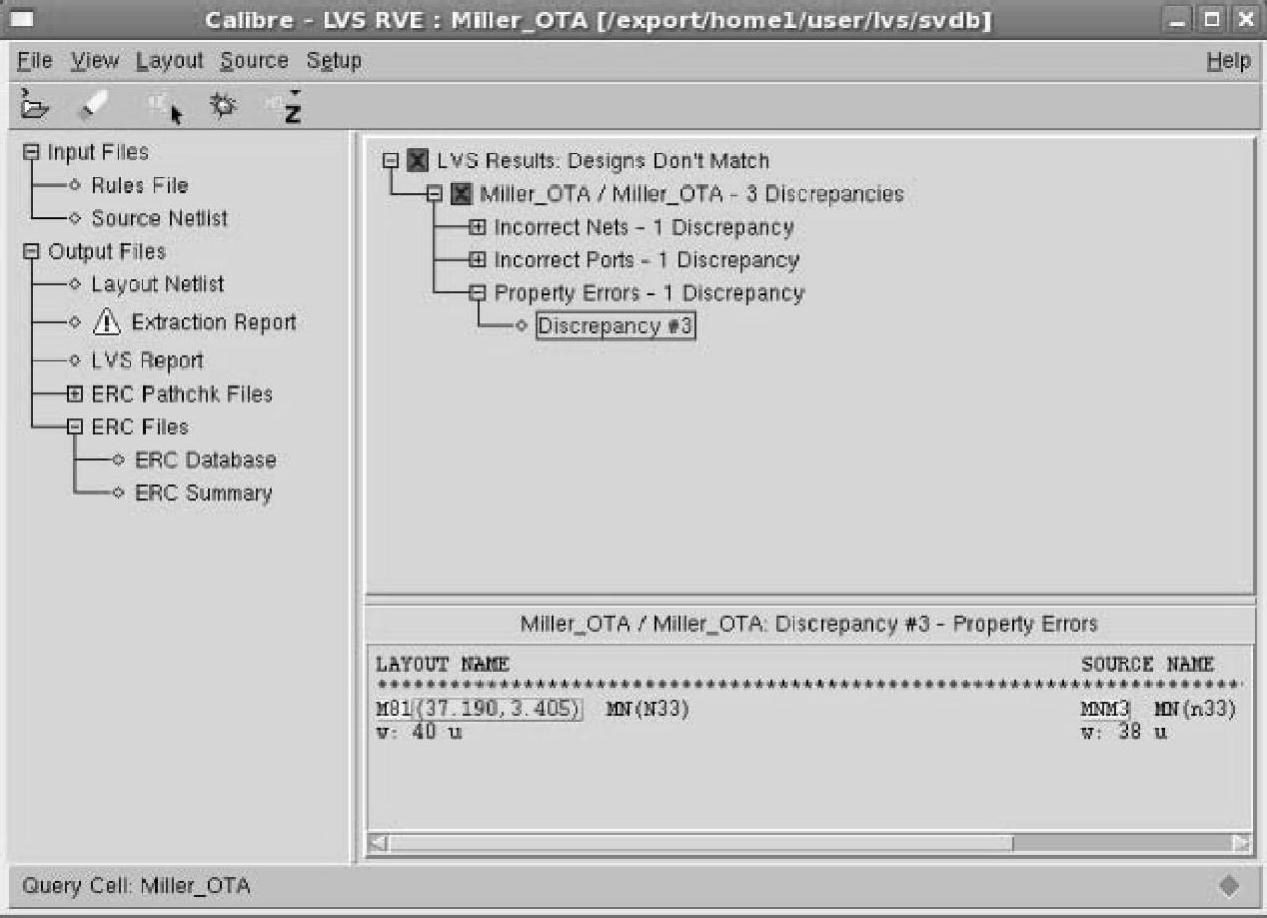

11)查看图4.71所示的Calibre LVS输出结果的图形界面,表明在版图与电路图存在3项(共3类)不匹配错误,包括一项连线不匹配、一项端口匹配错误以及一项器件属性匹配错误。

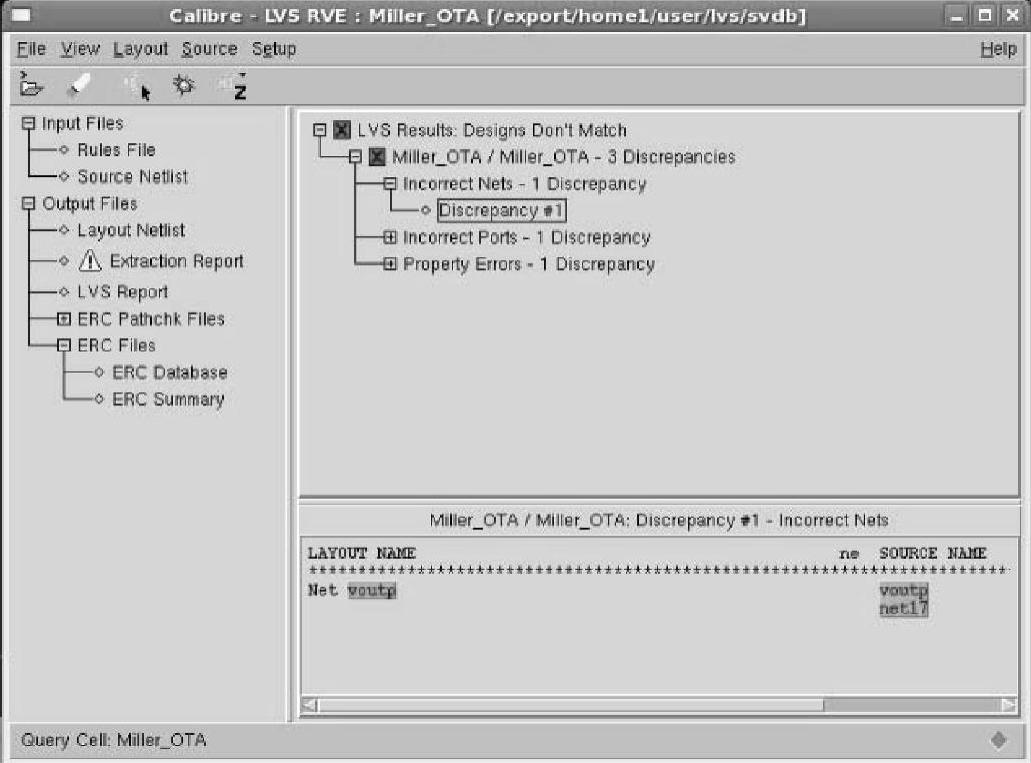

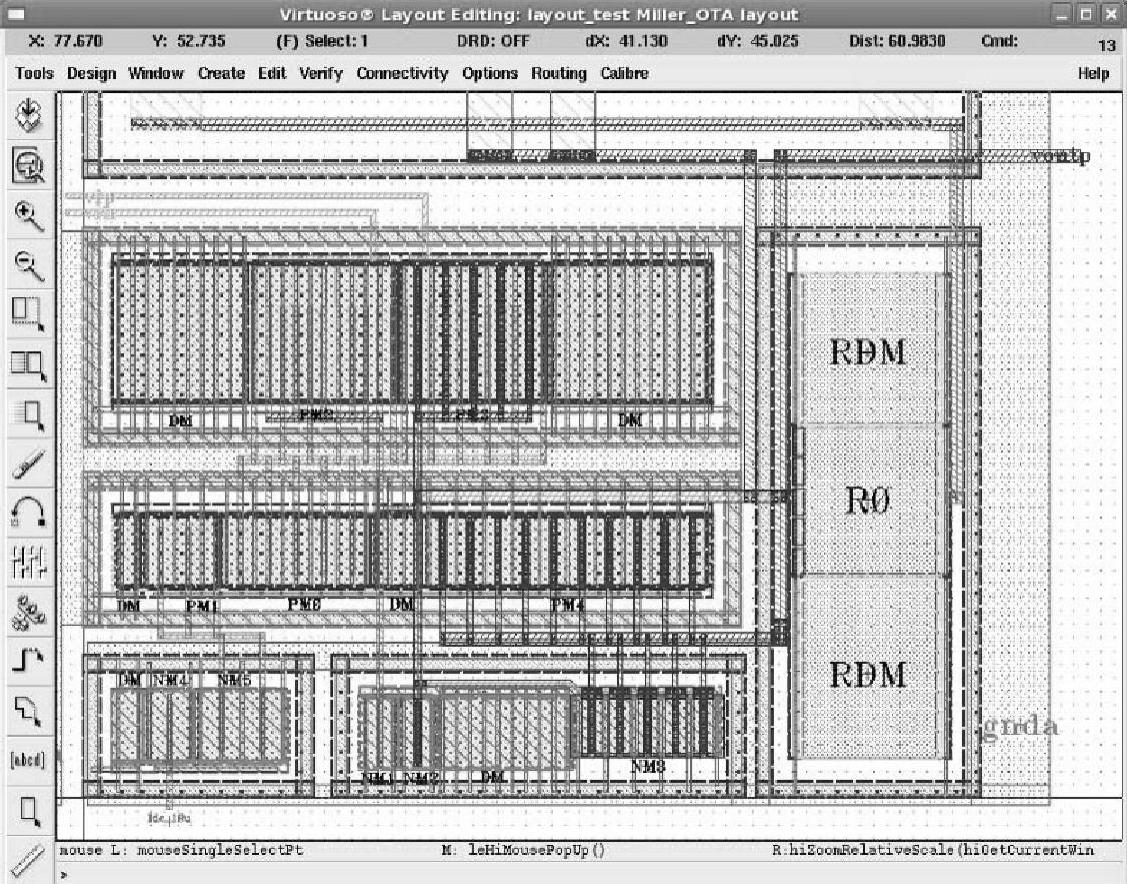

12)匹配错误1修改。鼠标左键单击Incorrect Nets-1 Discrepancy,并单击下属菜单中Discrepancy#1,LVS结果查看图形界面如图4.72所示,双击LAYOUT NAME下的高亮“voutp”,呈现版图中的voutp连线,如图4.73所示。

图4.72 Calibre LVS结果1查看图形界面

图4.73 相应版图错误定位

13)根据LVS错误提示信息进行版图修改,步骤12)中的提示信息表明版图连线voutp与电路的net17连线短路,应该对其进行修改。

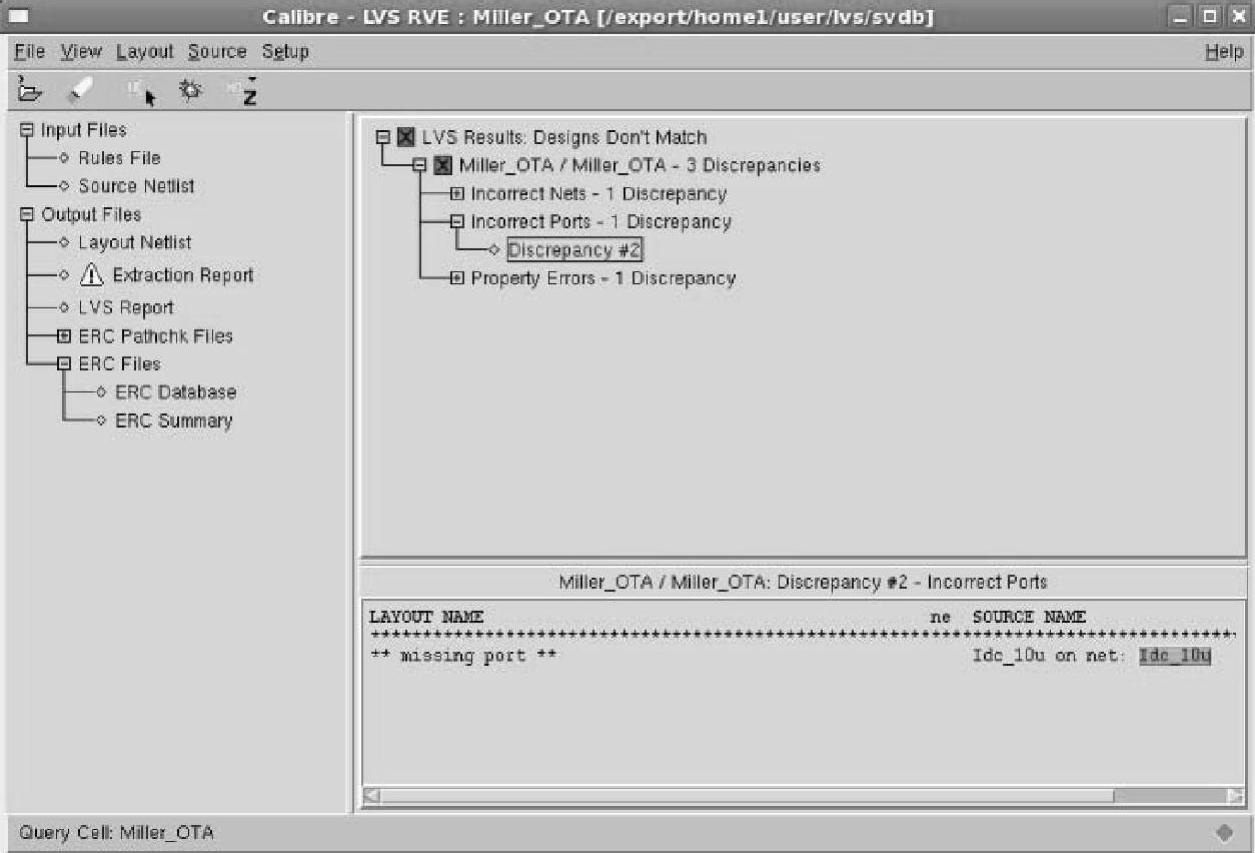

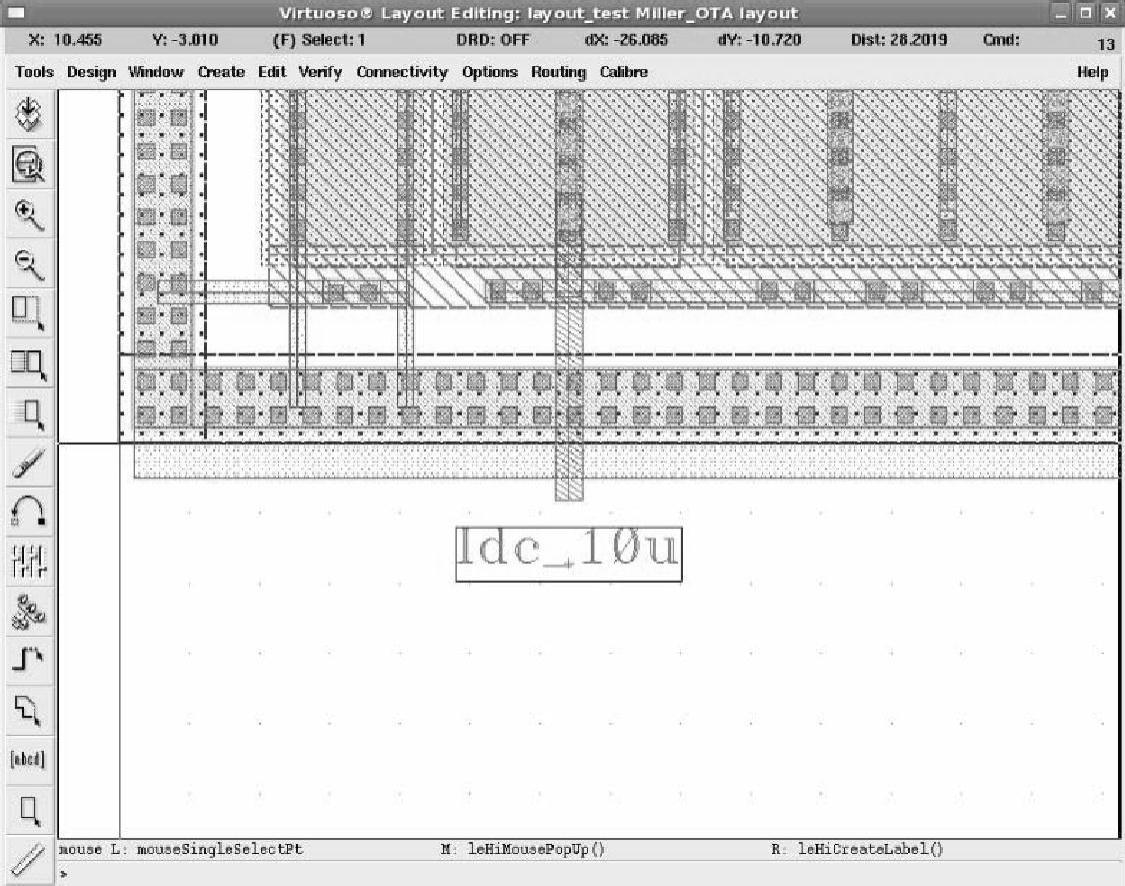

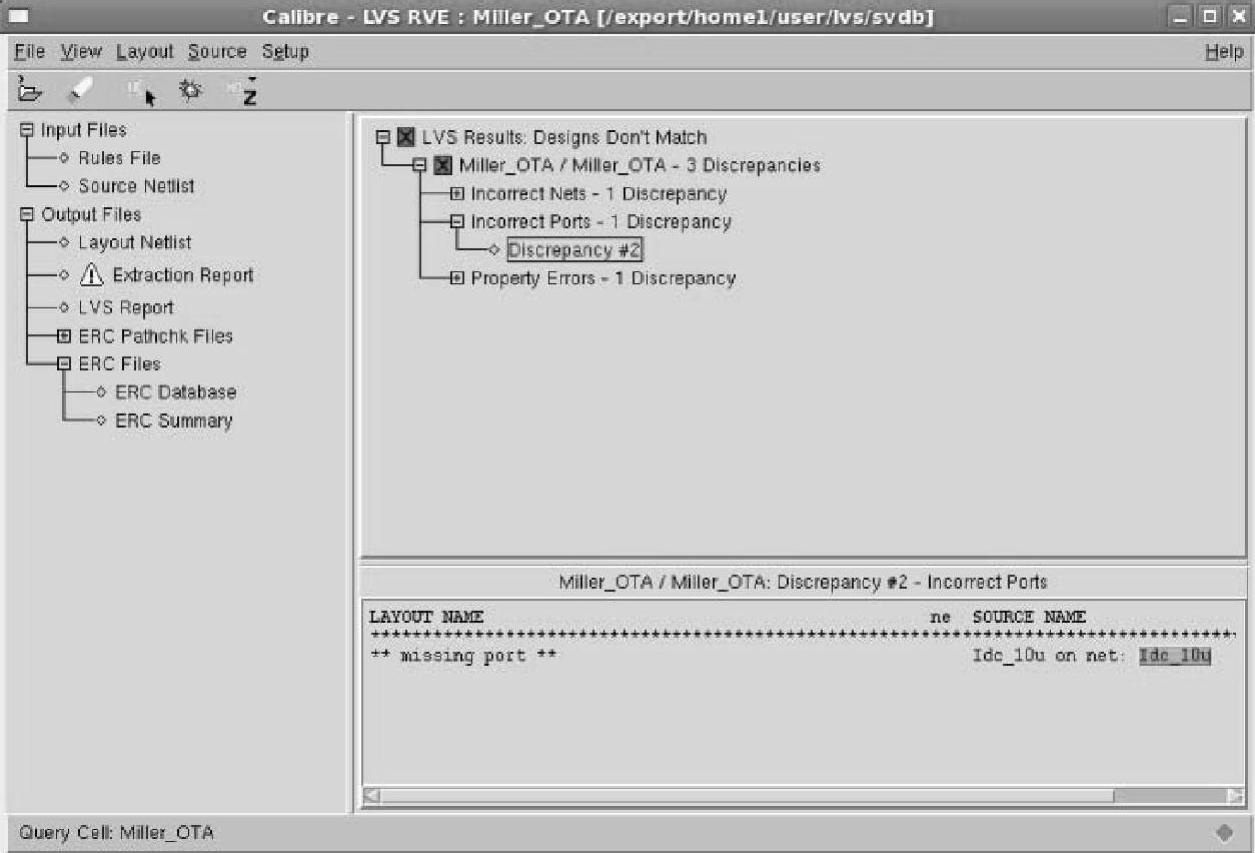

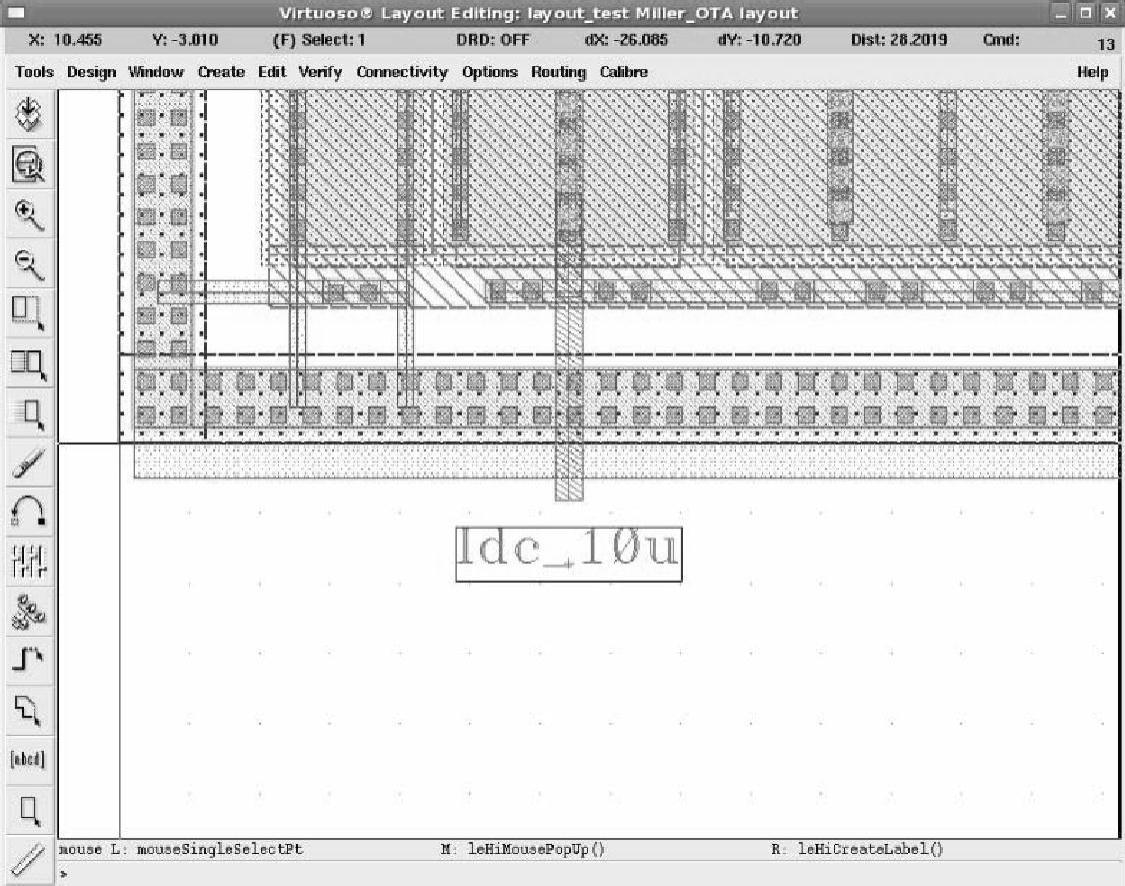

14)匹配错误2修改。鼠标左键单击Incorrect Ports-1 Discrepancy,并单击下属菜单中Discrepancy#2,相应的LVS报错信息查看图形界面如图4.74所示,其表明端口Idc_10u没有标在相应的版图层上或者没有打标,查看版图相应位置,如图4.75所示。

图4.74 Calibre LVS结果2查看图形界面

图4.75 相应版图错误定位

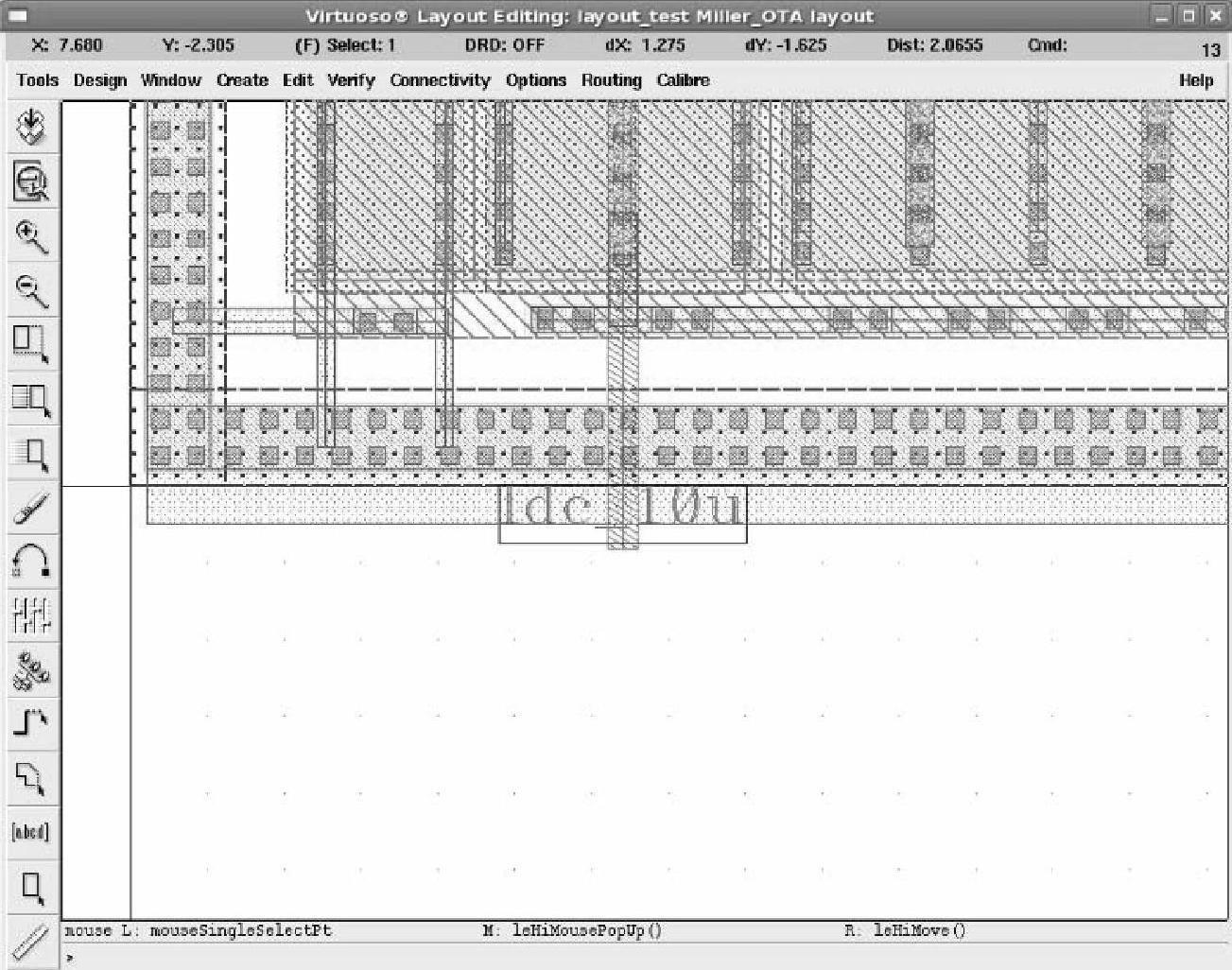

15)图3.75所示的标识Idc_10u没有打在相应的版图层上,导致Calibre无法找到其端口信息,修改方式为将标识上移至相应的版图层上即可,如图4.76所示。

图4.76 标识修改后的版图

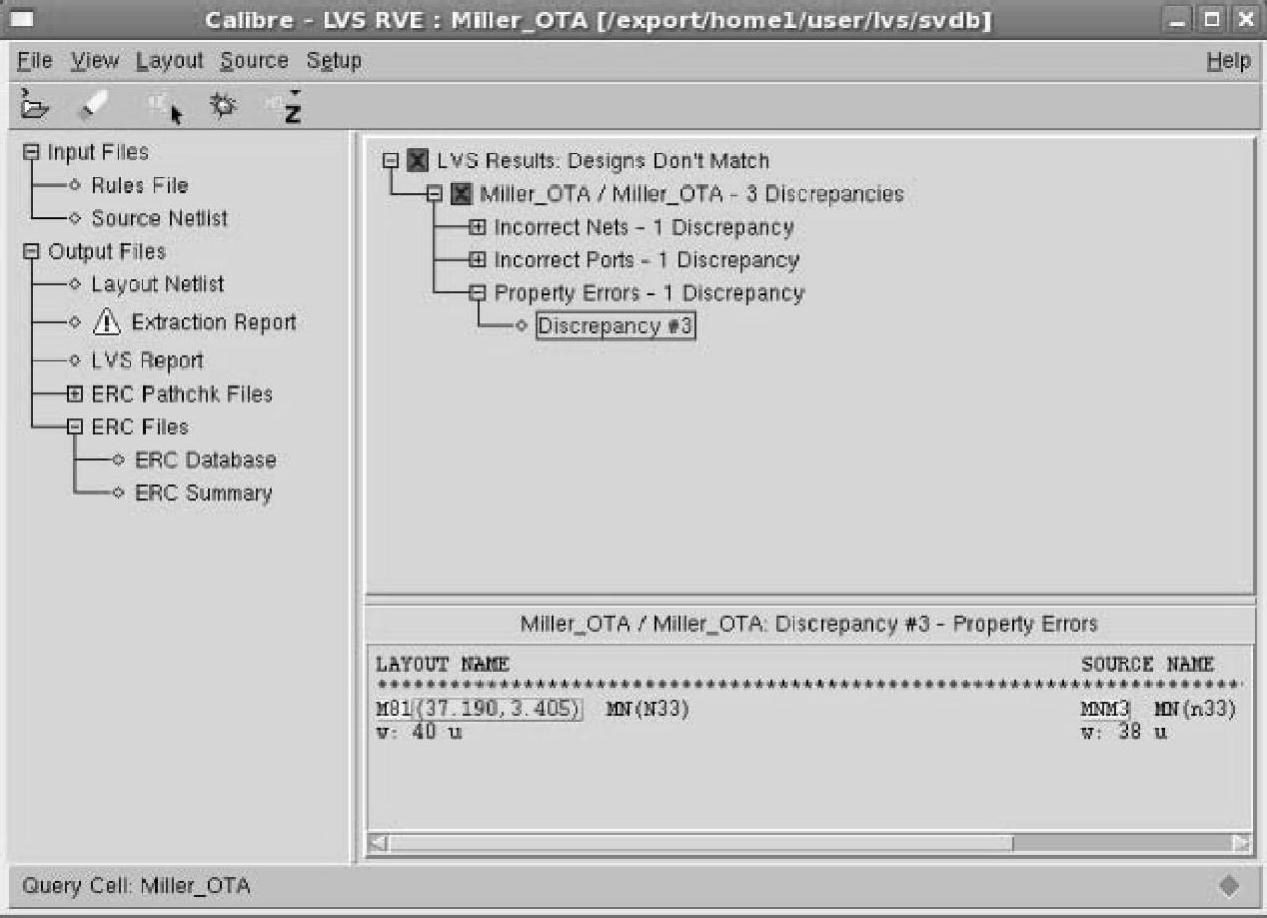

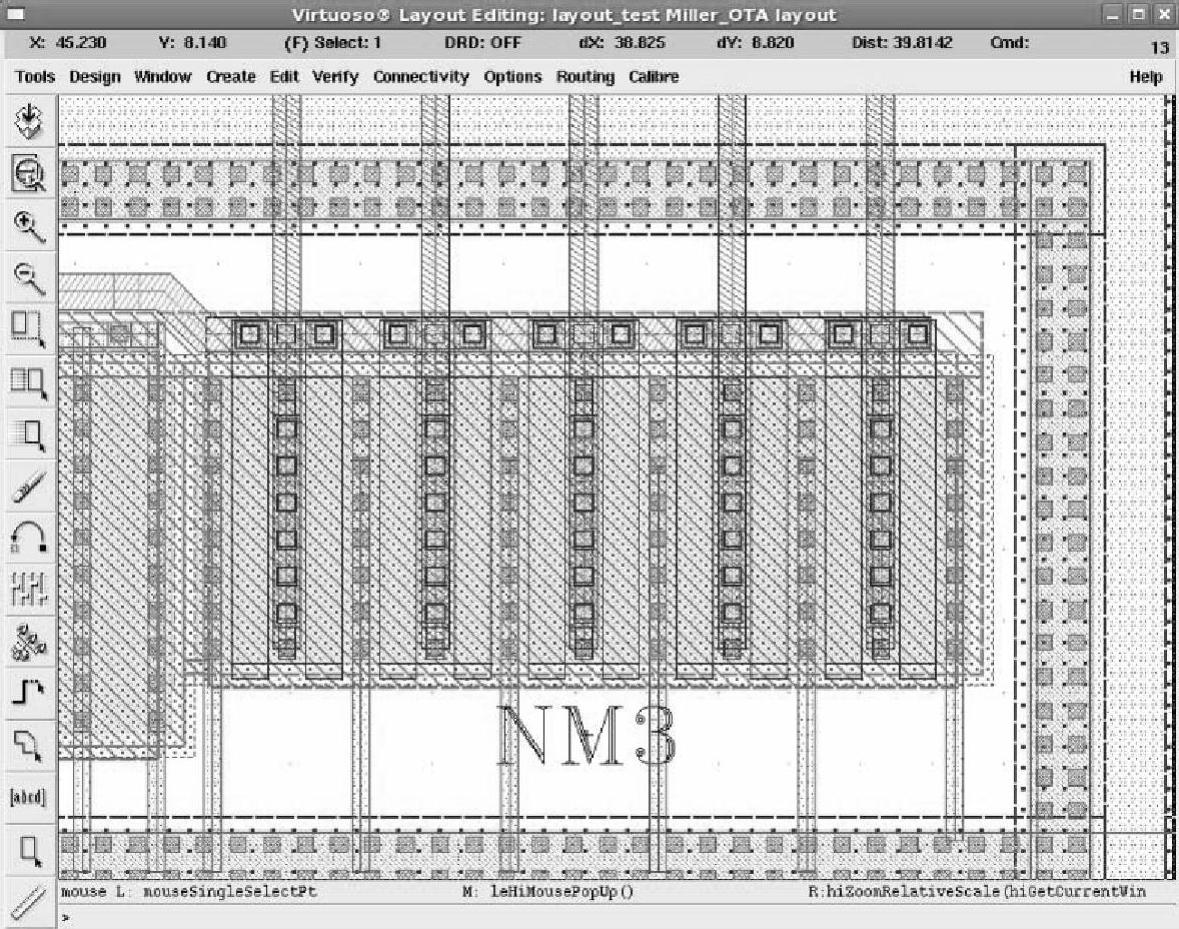

16)匹配错误3修改。鼠标左键单击Property Error-1 Discrepancy,并单击下属菜单中Discrepancy#3,相应的LVS报错信息查看图形界面如图4.77所示,其表明版图中器件尺寸与相应电路图中的不一致,查看版图相应位置,如图4.78所示。

图4.77 Calibre LVS结果3查看图形界面

图4.78 相应版图错误定位

17)图4.78所示版图中晶体管的尺寸为4μm×10=40μm,而电路图中为38μm,将版图中晶体管的尺寸修改为3.8μm×10=38μm即可。

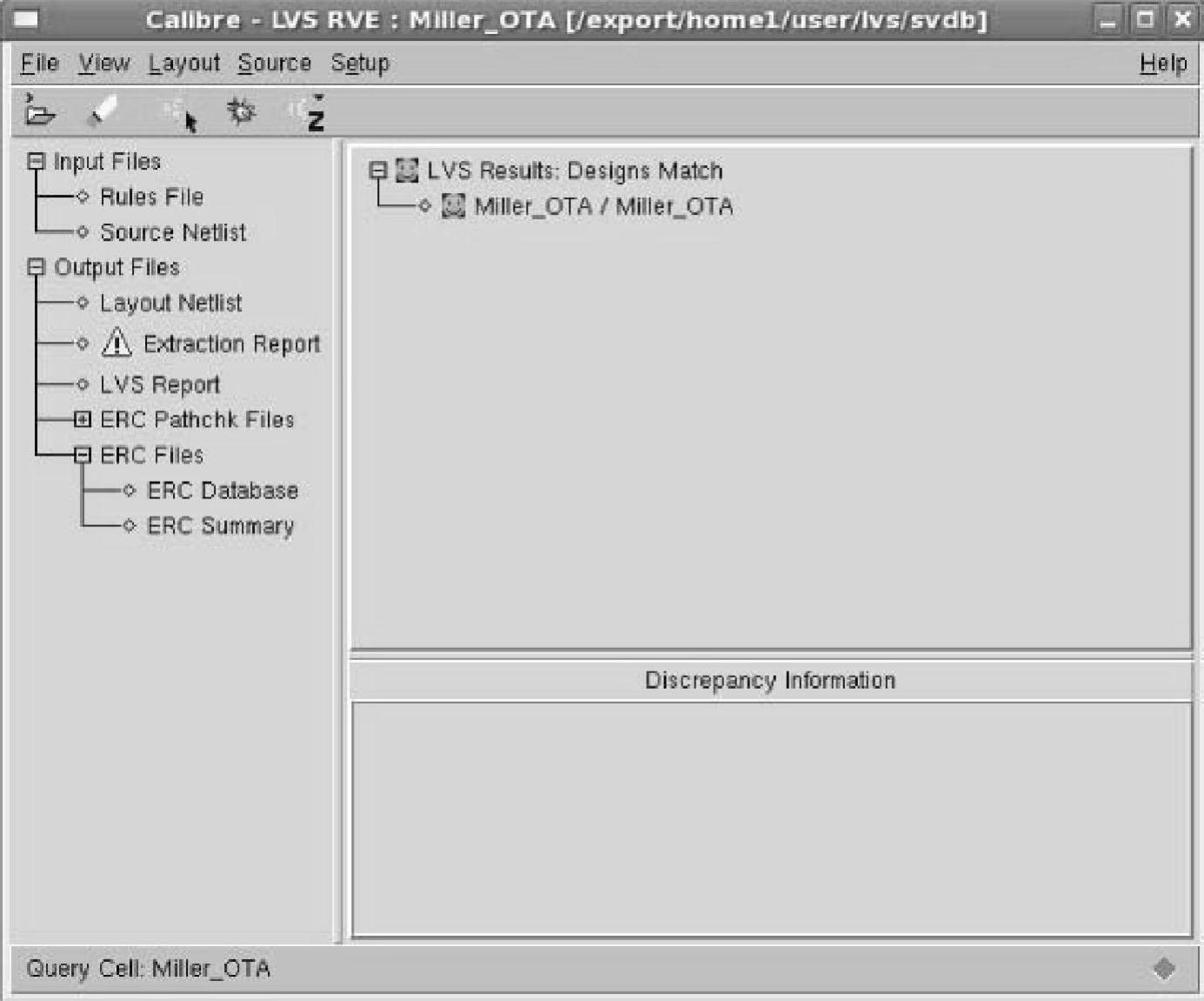

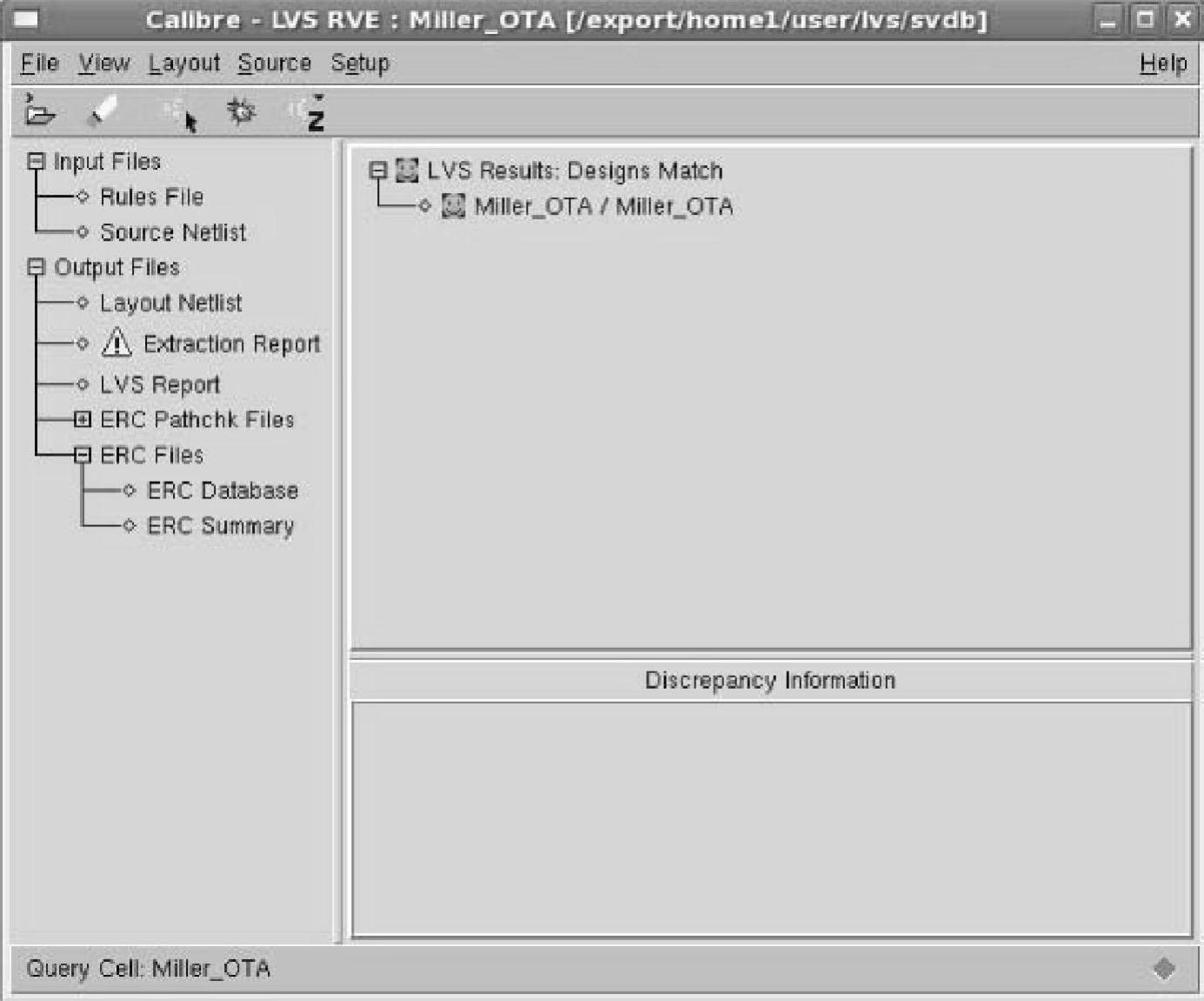

18)LVS匹配错误修改完毕后,再次做LVS,直到所有的匹配错误都修改完毕,直到出现如图4.79所示的界面,表明LVS已经通过。

图4.79 Calibre LVS通过界面

以上完成了Calibre LVS检查的主要流程。

相关推荐