【摘要】:下面详细介绍采用Mentor Calibre工具对版图进行DRC的流程,并示出几处修改违反DRC规则错误的方法。本节采用内嵌在Cadence Virtuoso Layout Editor的菜单选项来启动Calibre DRC。图4.32 Calibre DRC运行中9)Calibre DRC完成后,软件会自动弹出输出结果RVE以及文本格式文件,分别如图4.33和图4.34所示。图4.35 DRC结果查看图形界面图4.36 相应版图错误定位图4.37 修改后版图图4.38 DRC结果查看图形界面图4.39 相应版图错误定位图4.40 修改后版图图4.41 Calibre DRC通过界面以上完成了Calibre DRC的主要流程。

下面详细介绍采用Mentor Calibre工具对版图进行DRC的流程,并示出几处修改违反DRC规则错误的方法。本节采用内嵌在Cadence Virtuoso Layout Editor的菜单选项来启动Calibre DRC。Calibre DRC的使用流程如下:

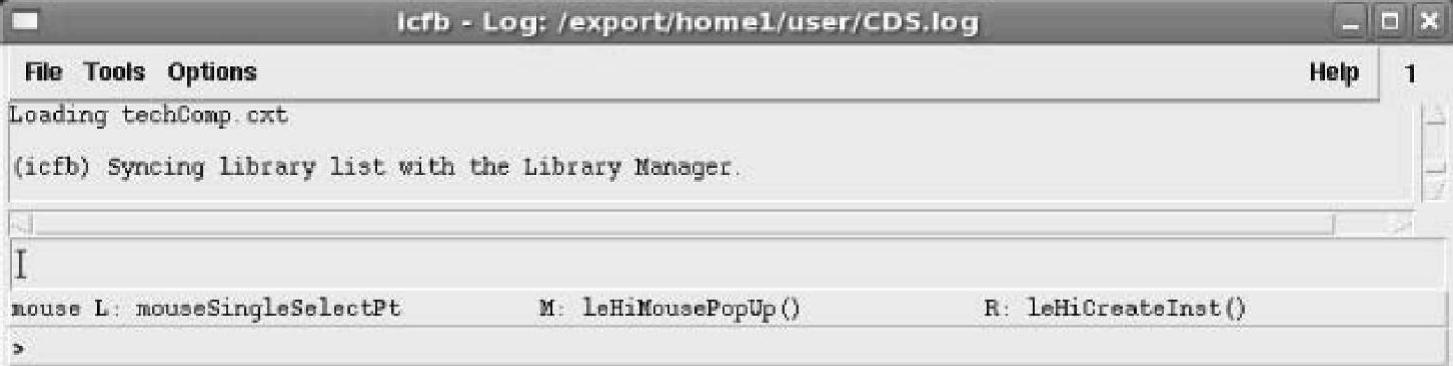

1)启动Cadence Virtuoso工具命令icfb&,弹出如图4.25所示窗口。

图4.25 启动Cadence Virtuoso

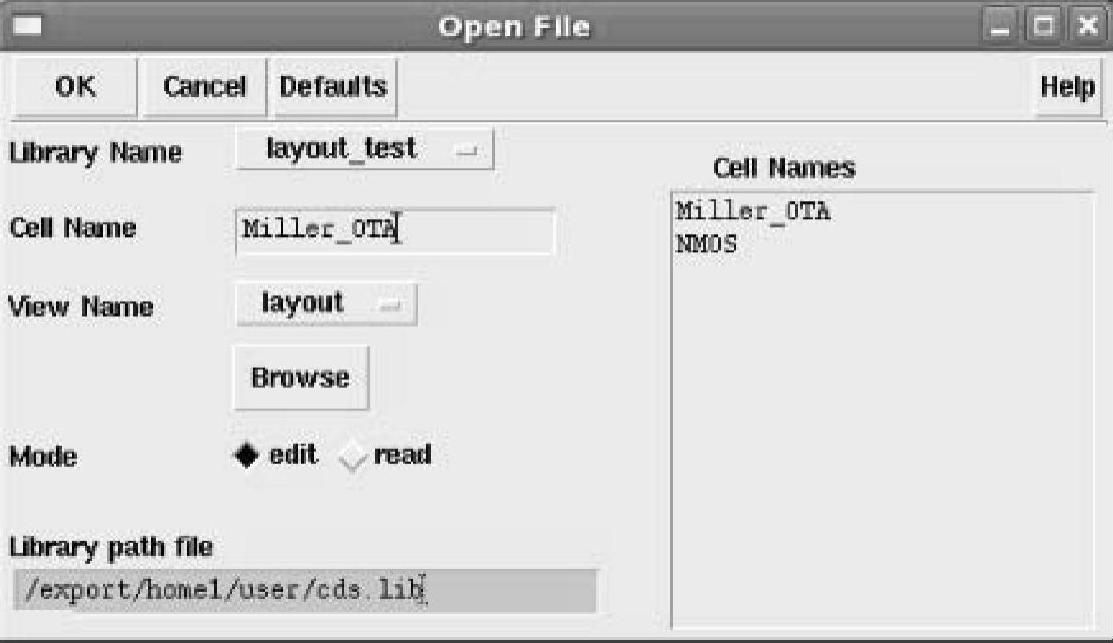

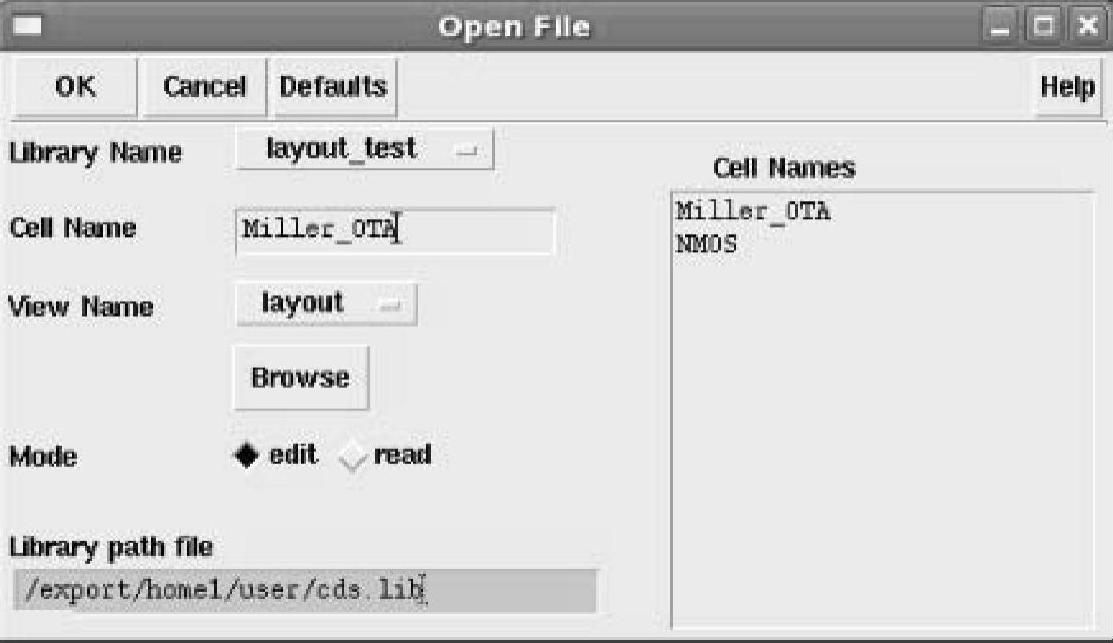

2)打开需要验证的版图视图。选择File→Open,弹出打开版图窗口,在“Li-brary Name”中选择“layoutt_est”,“Cell Name”中选择“Miller_OTA”,“View Name”中选择“layout”,如图4.26所示。

图4.26 打开版图窗口

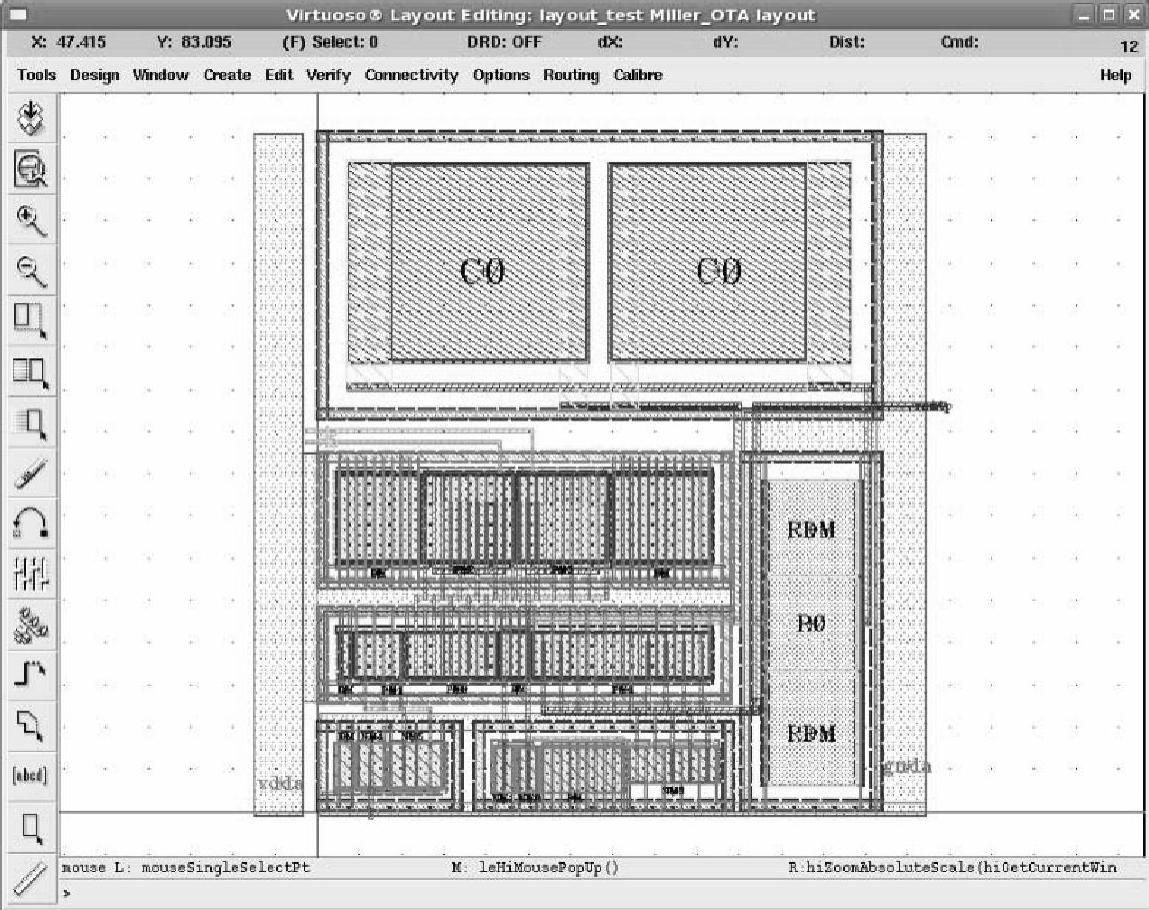

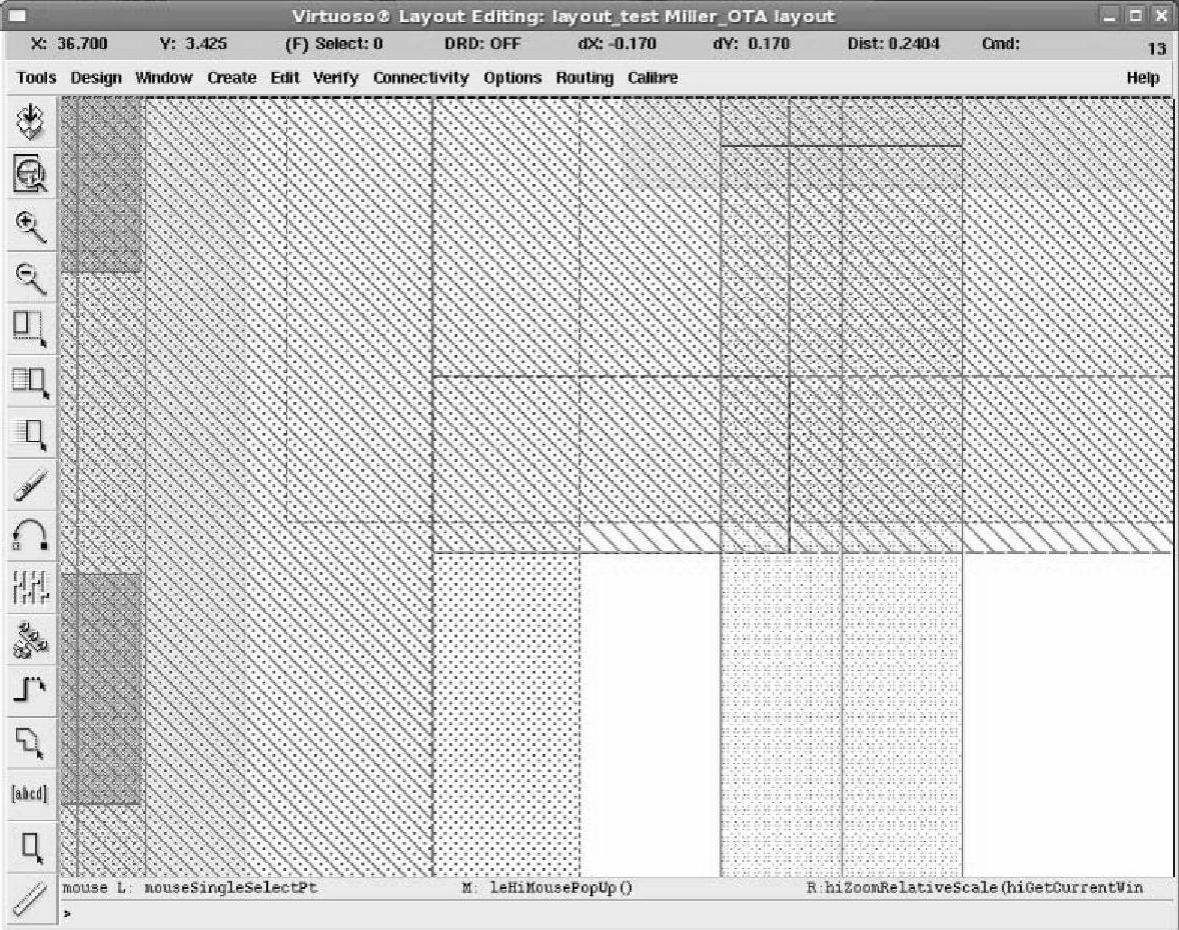

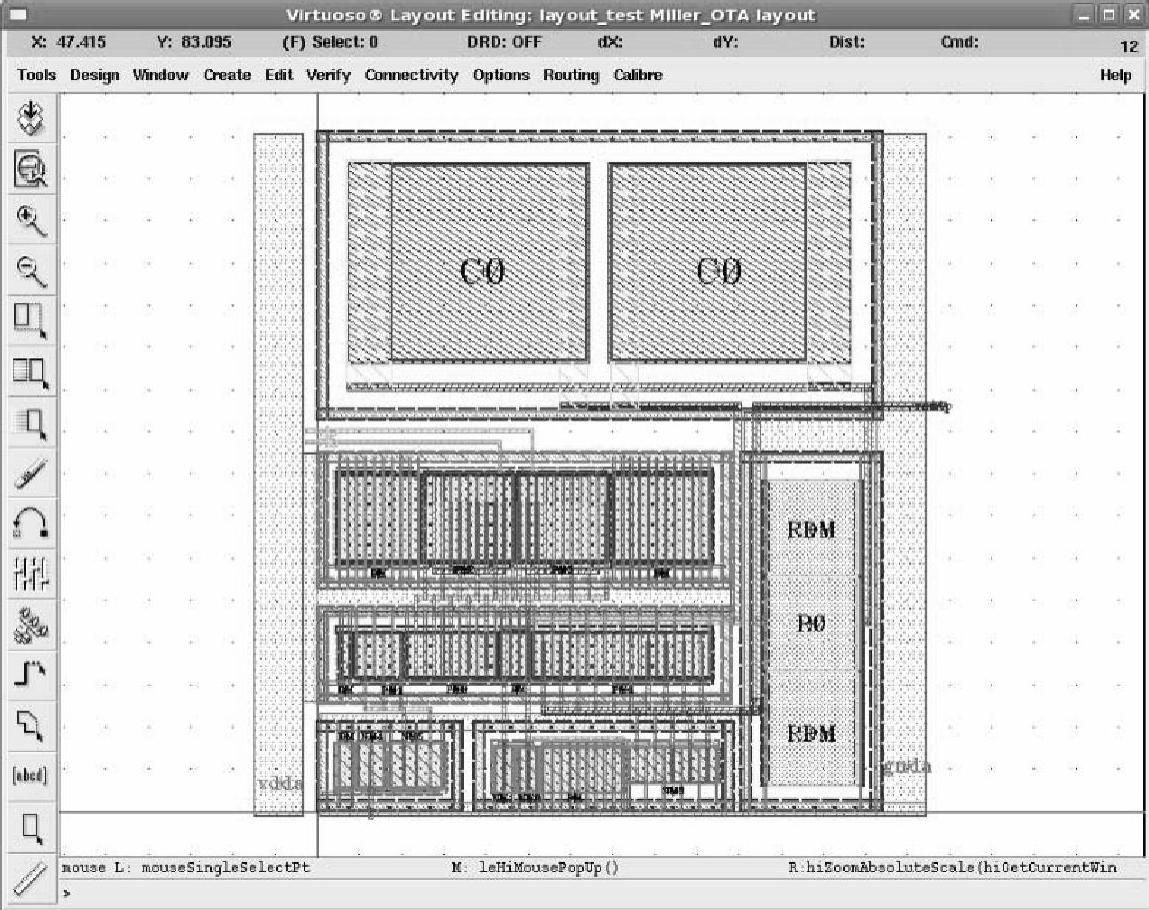

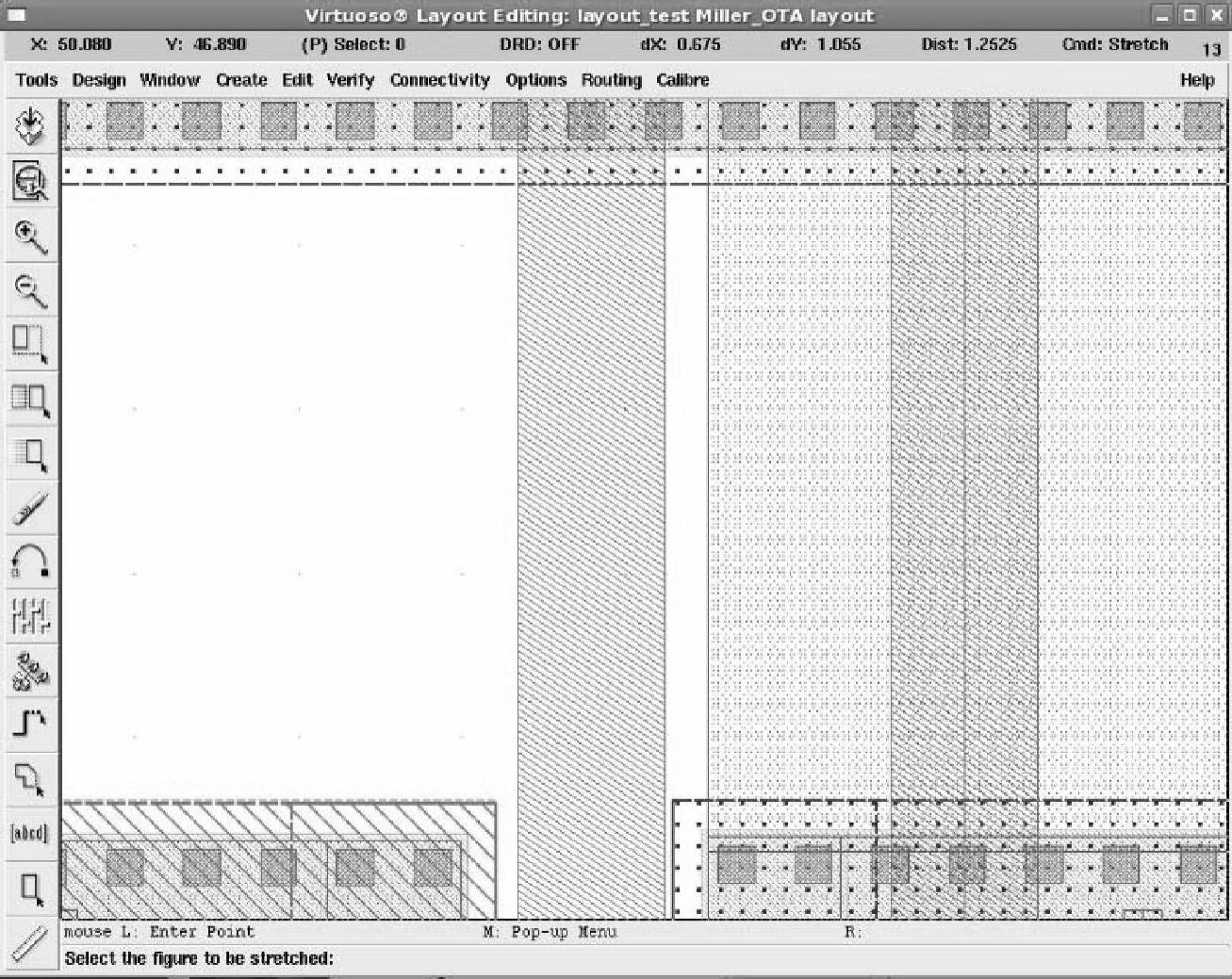

3)单击“OK”按钮,弹出Miller_OTA版图视图,如图4.27所示。

图4.27 打开Miller_OTA版图

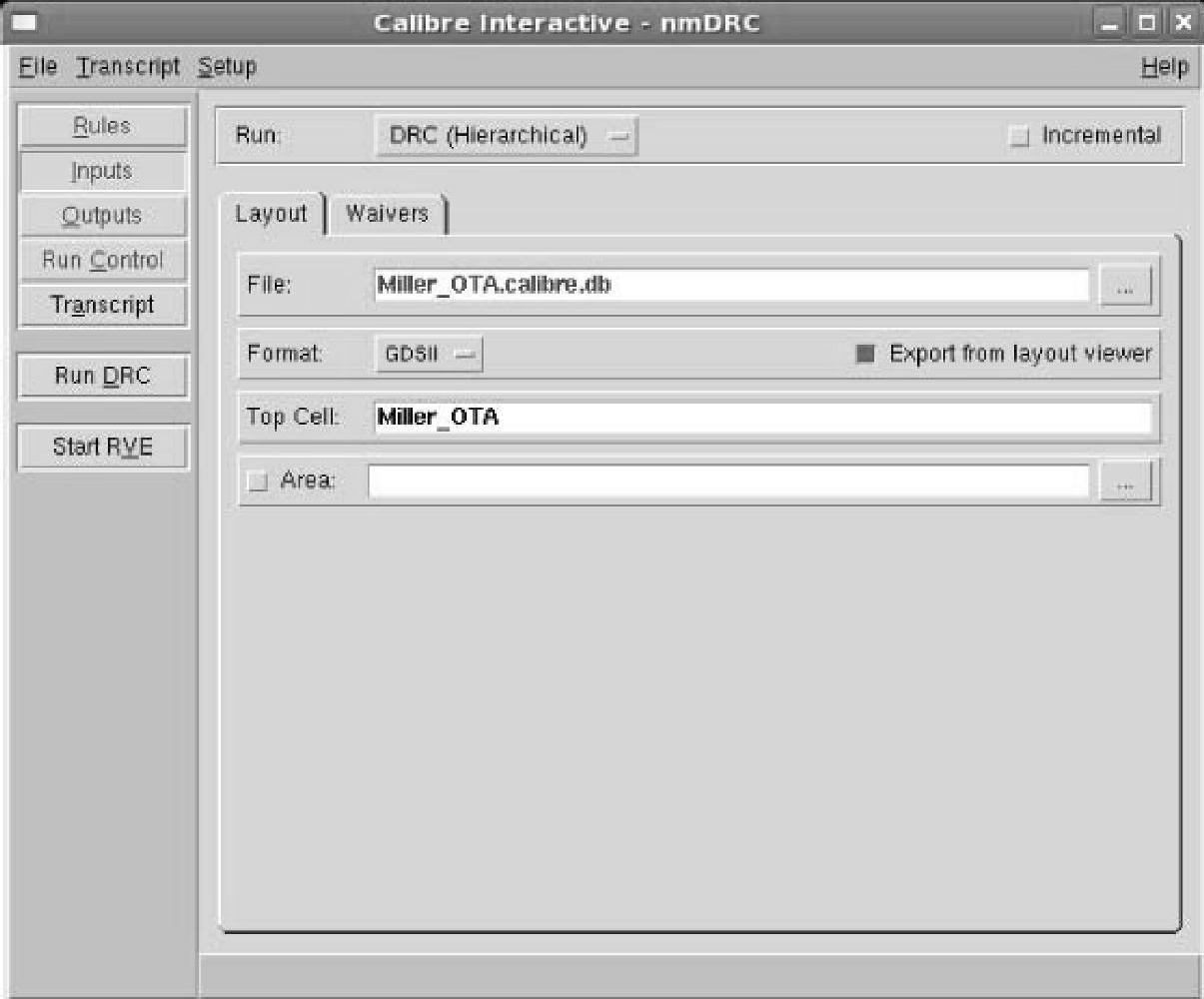

4)在Miller_OTA版图视图的工具菜单栏中选择Calibre→Run DRC,弹出Cal-ibre DRC工具对话框,如图4.28所示。

5)选择工具选项菜单中的Rules,并在DRC工具对话框右侧DRC Rules File栏中单击[...]选择设计规则文件,并在DRC Run Directory栏右侧选择[...]选择运行目录,如图4.29所示。

图4.28 打开Calibre DRC工具

图4.29 Calibre DRC中Rules子菜单对话框

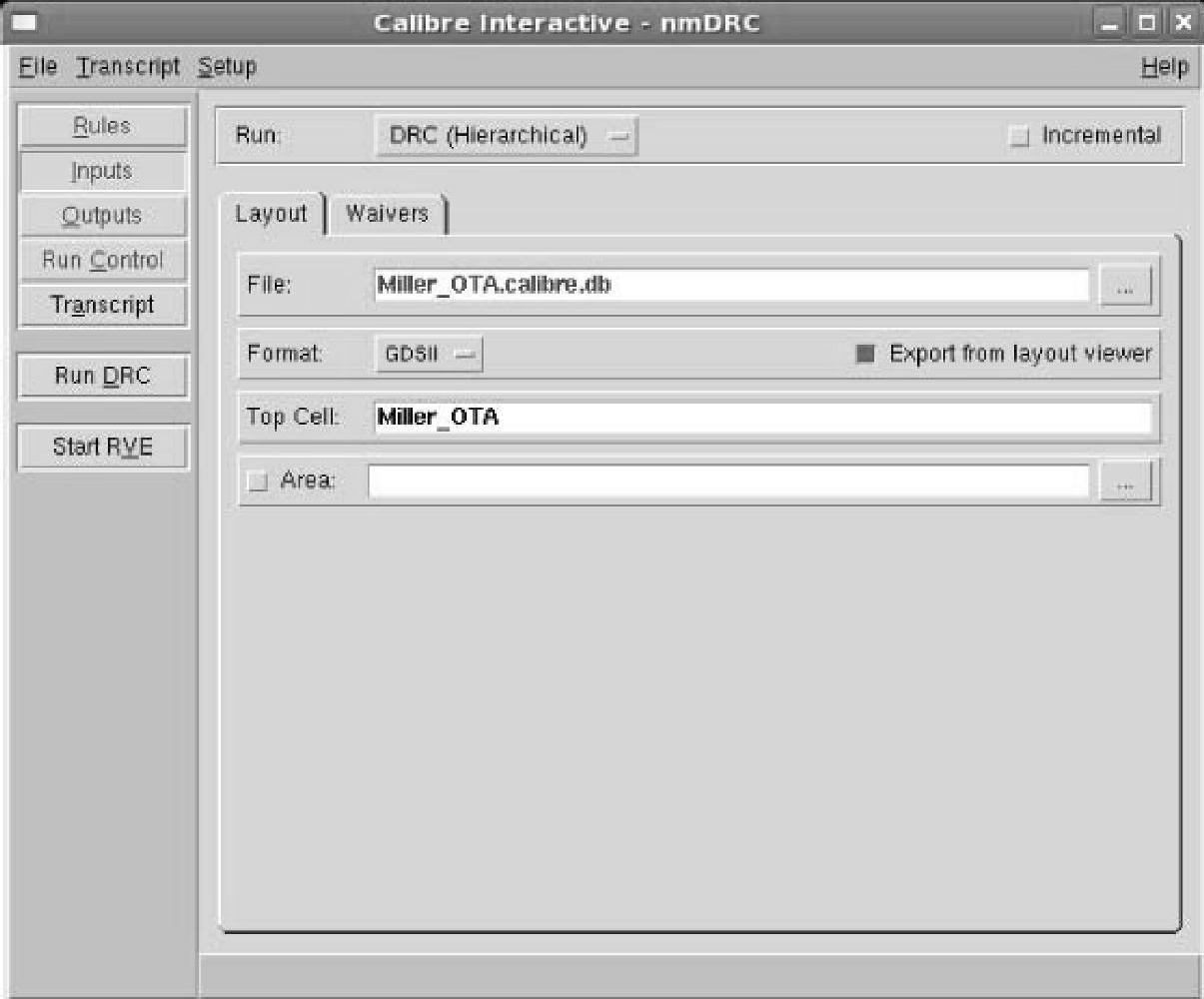

6)选择工具选项菜单中的Inputs,并在Layout选项中选择“Export from layout viewer”高亮,如图4.30所示。

图4.30 Calibre DRC中Inputs子菜单对话框

7)选择工具选项菜单中的Outputs,可以选择默认的设置,同时也可以改变相应输出文件的名称,如图4.31所示。

图4.31 Calibre DRC中Outputs子菜单对话框

8)Calibre DRC工具选项菜单的Run Control菜单可以选择默认设置,单击“Run DRC”,Calibre开始导出版图文件并对其进行DRC,如图4.32所示。

图4.32 Calibre DRC运行中

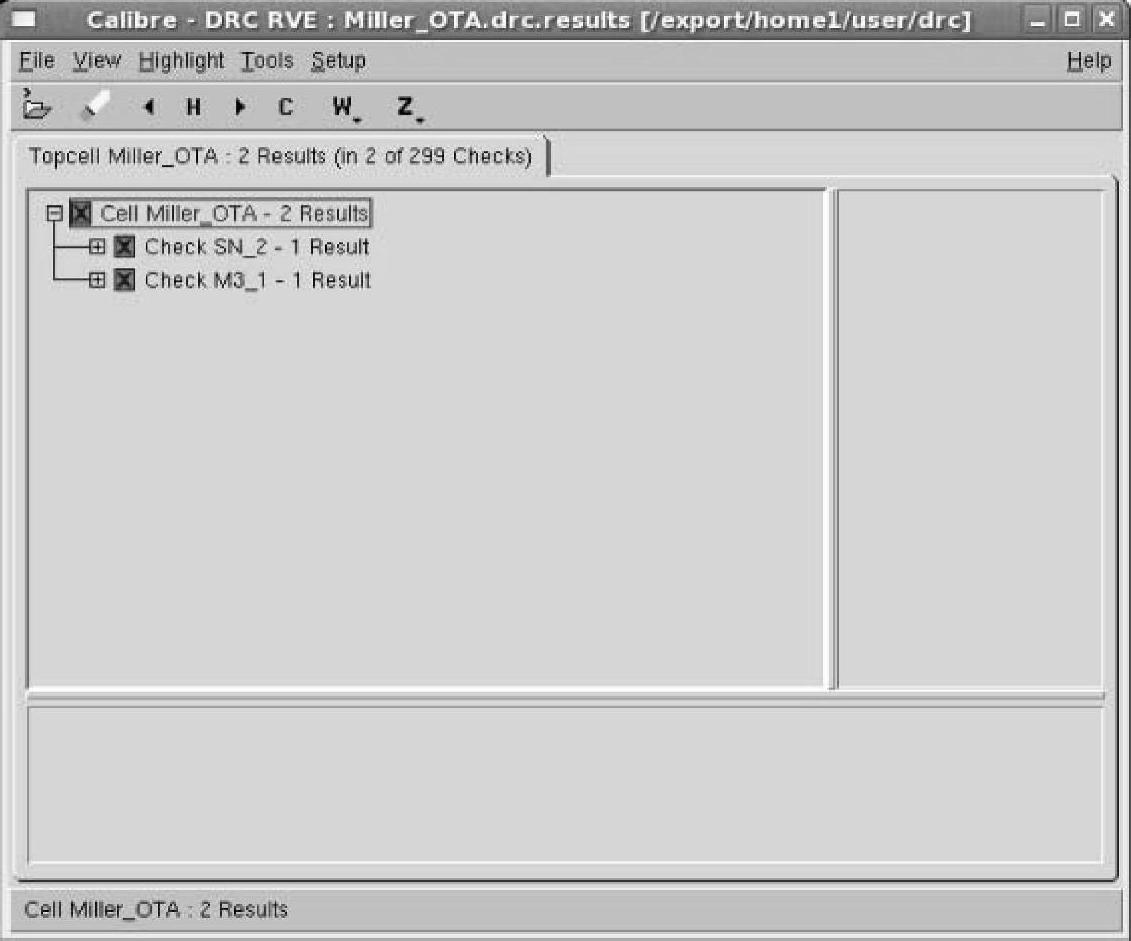

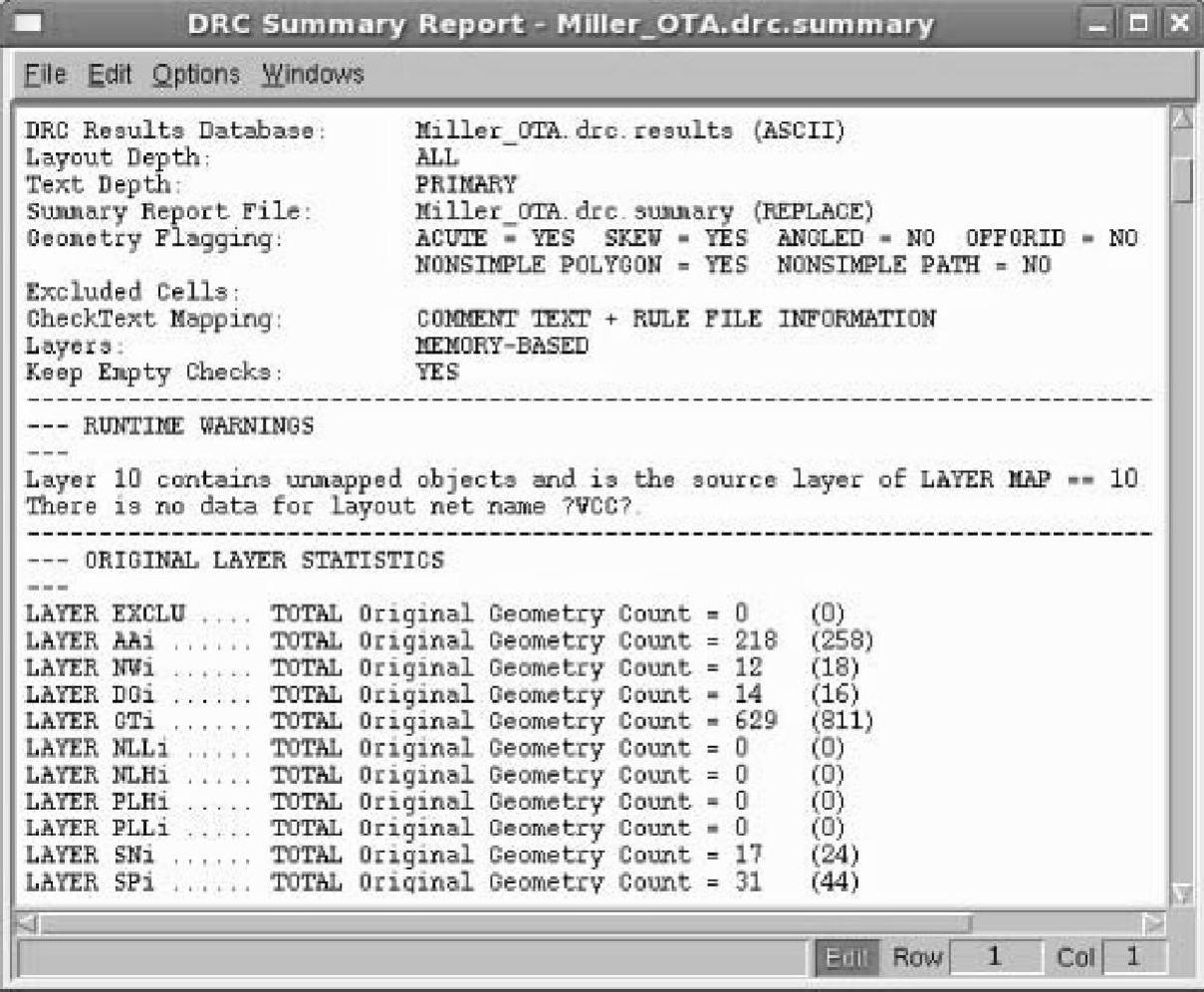

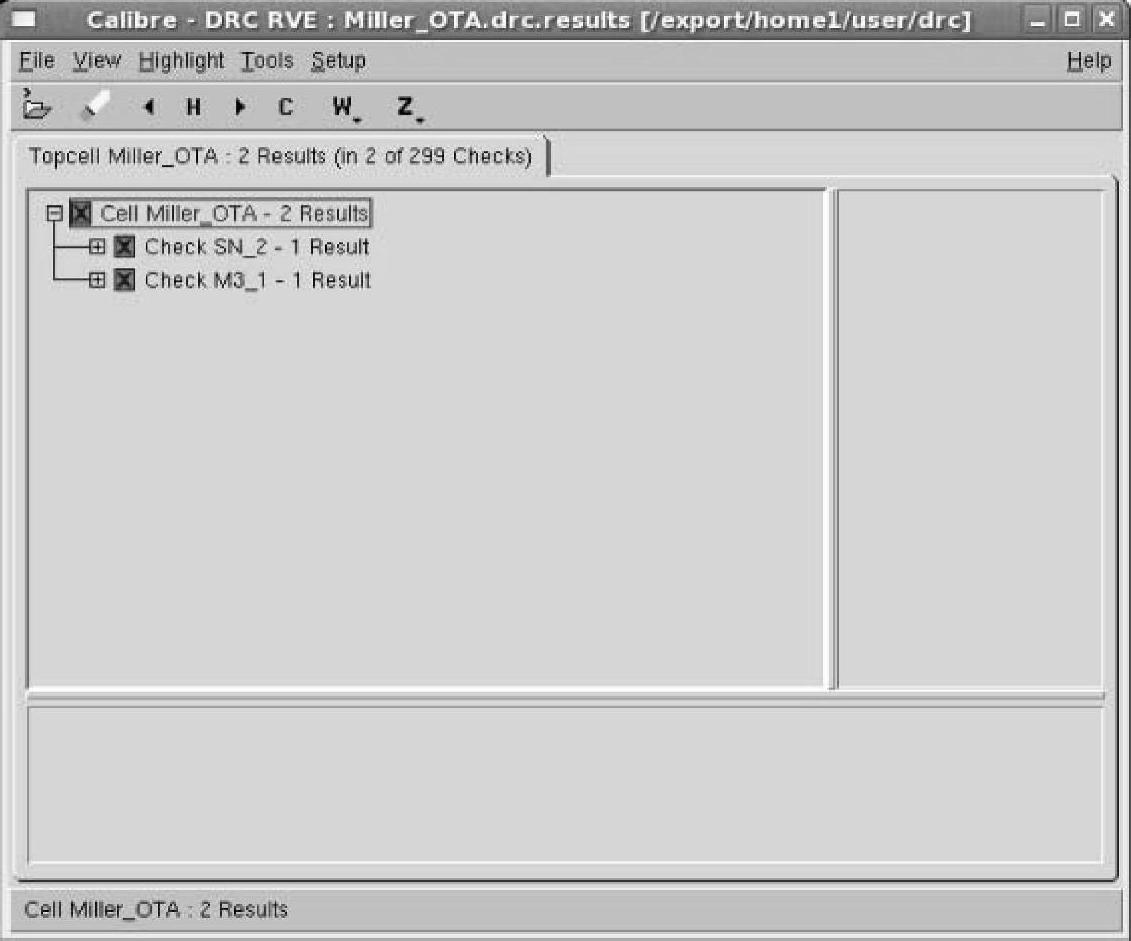

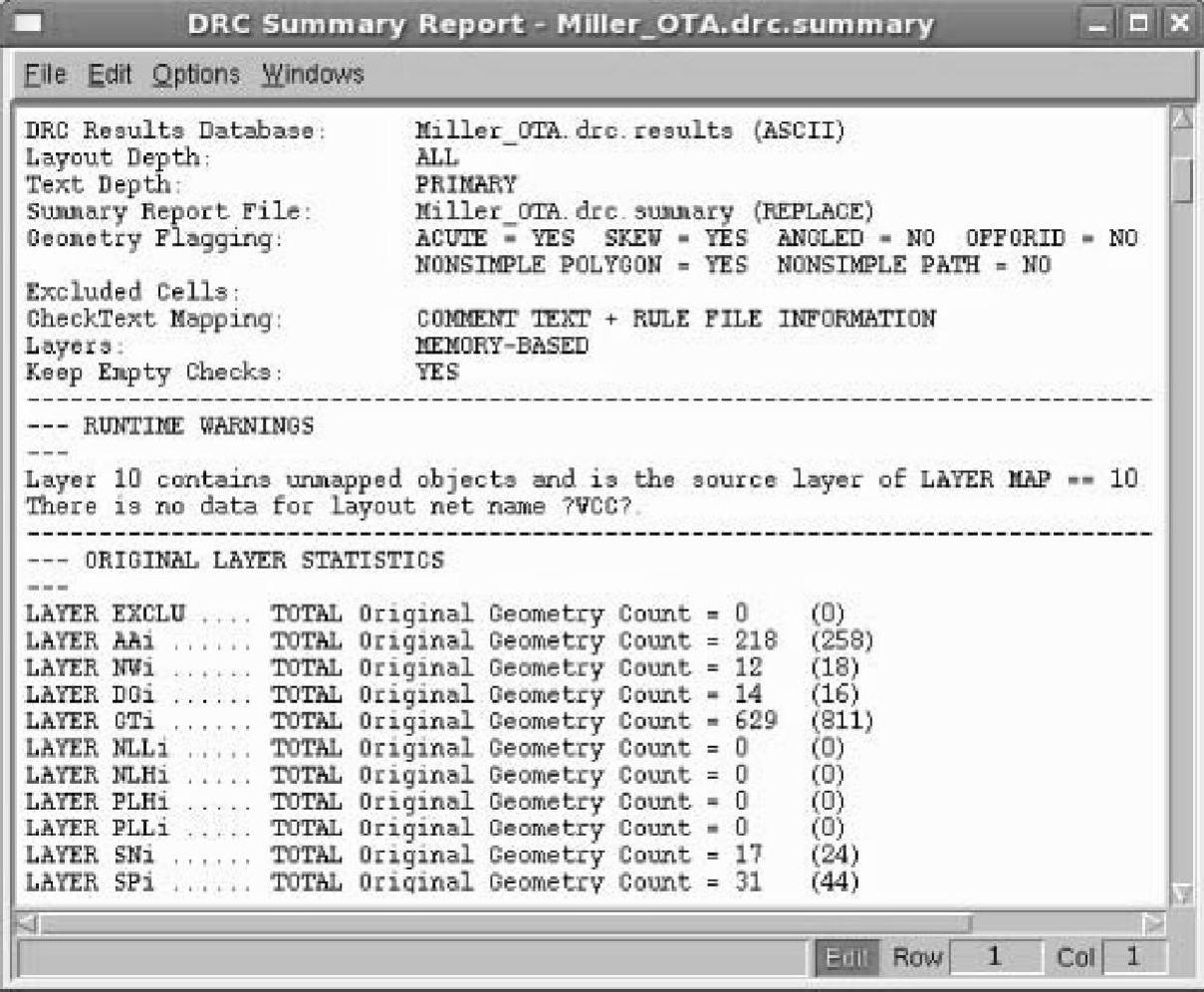

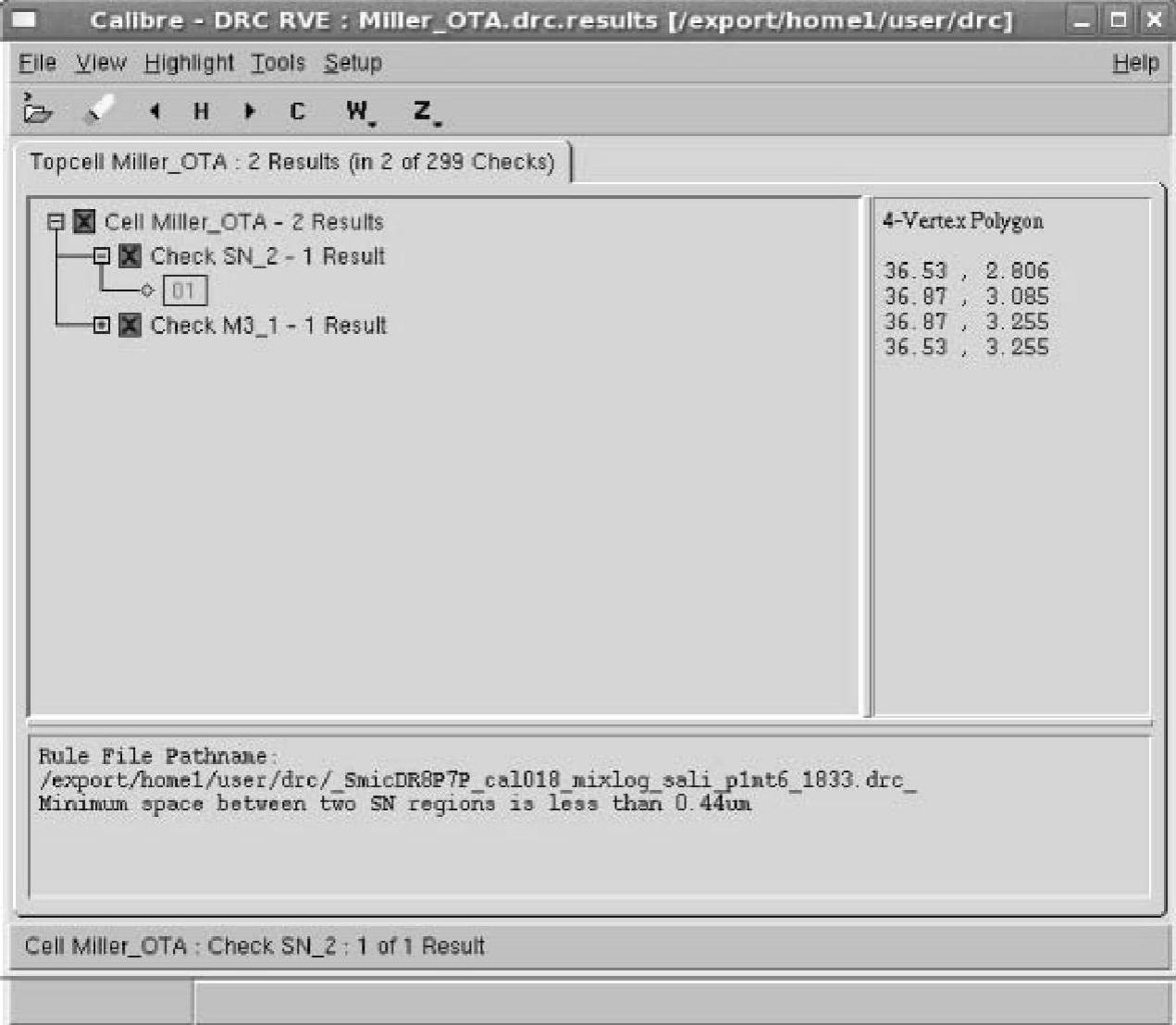

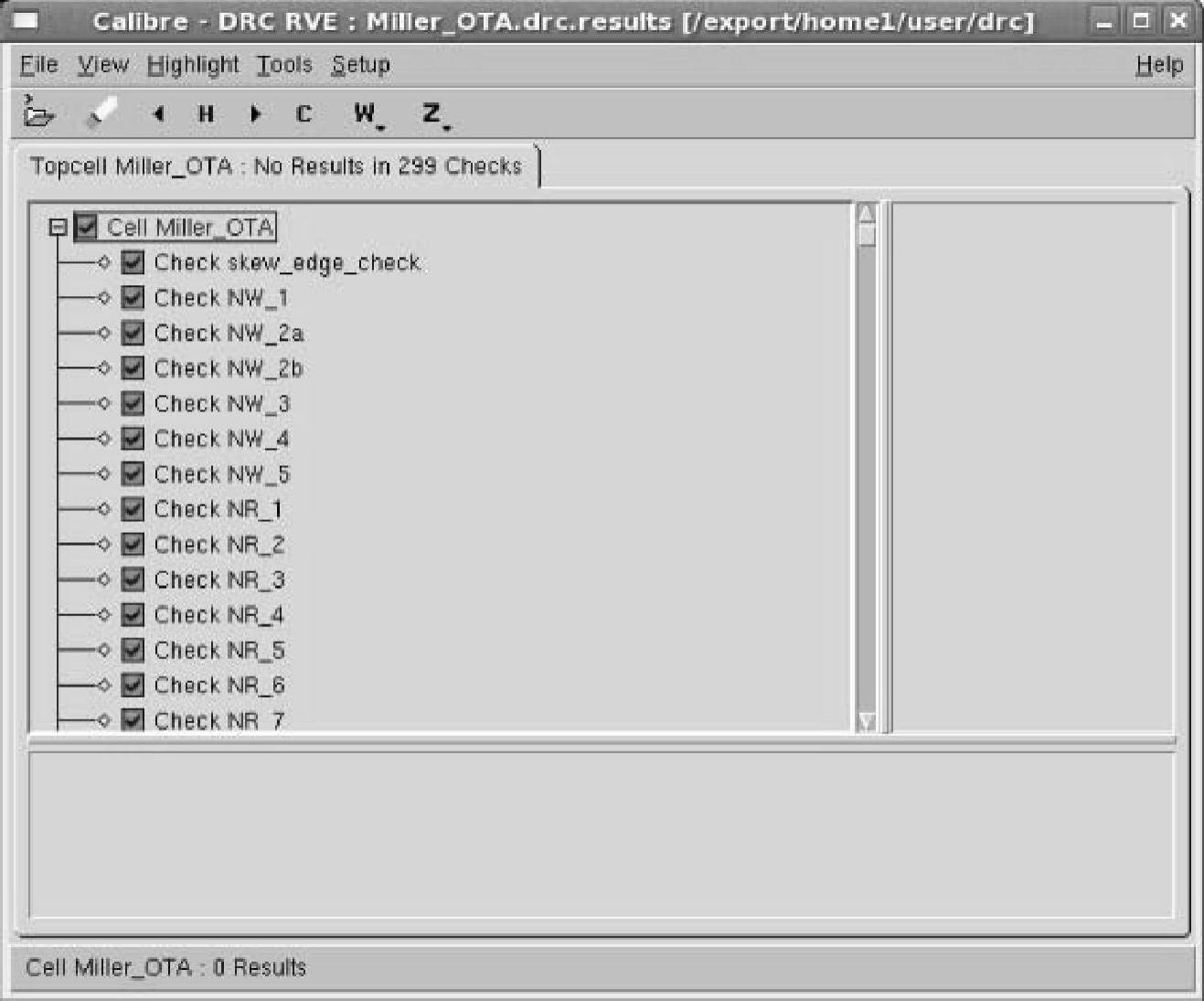

9)Calibre DRC完成后,软件会自动弹出输出结果RVE以及文本格式文件,分别如图4.33和图4.34所示。

图4.33 Calibre DRC结果查看图形界面

图4.34 Calibre DRC输出文本

10)查看图4.33所示的Calibre DRC输出结果的图形界面RVE,查看错误报告窗口表明在版图中存在两个DRC错误,分别为SN2(SN区间距小于0.44μm)和M31(M3的最小宽度小于0.28μm)。

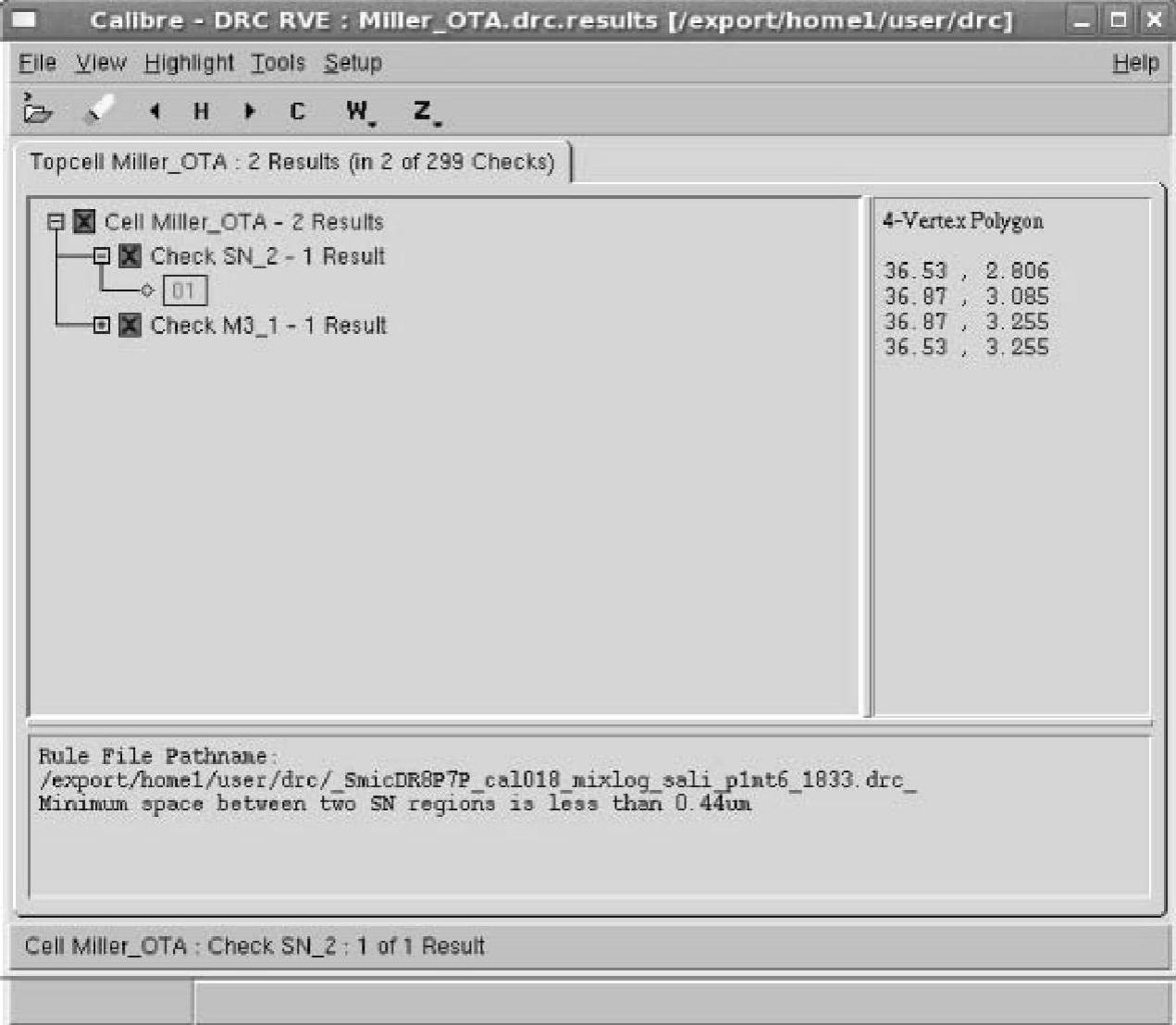

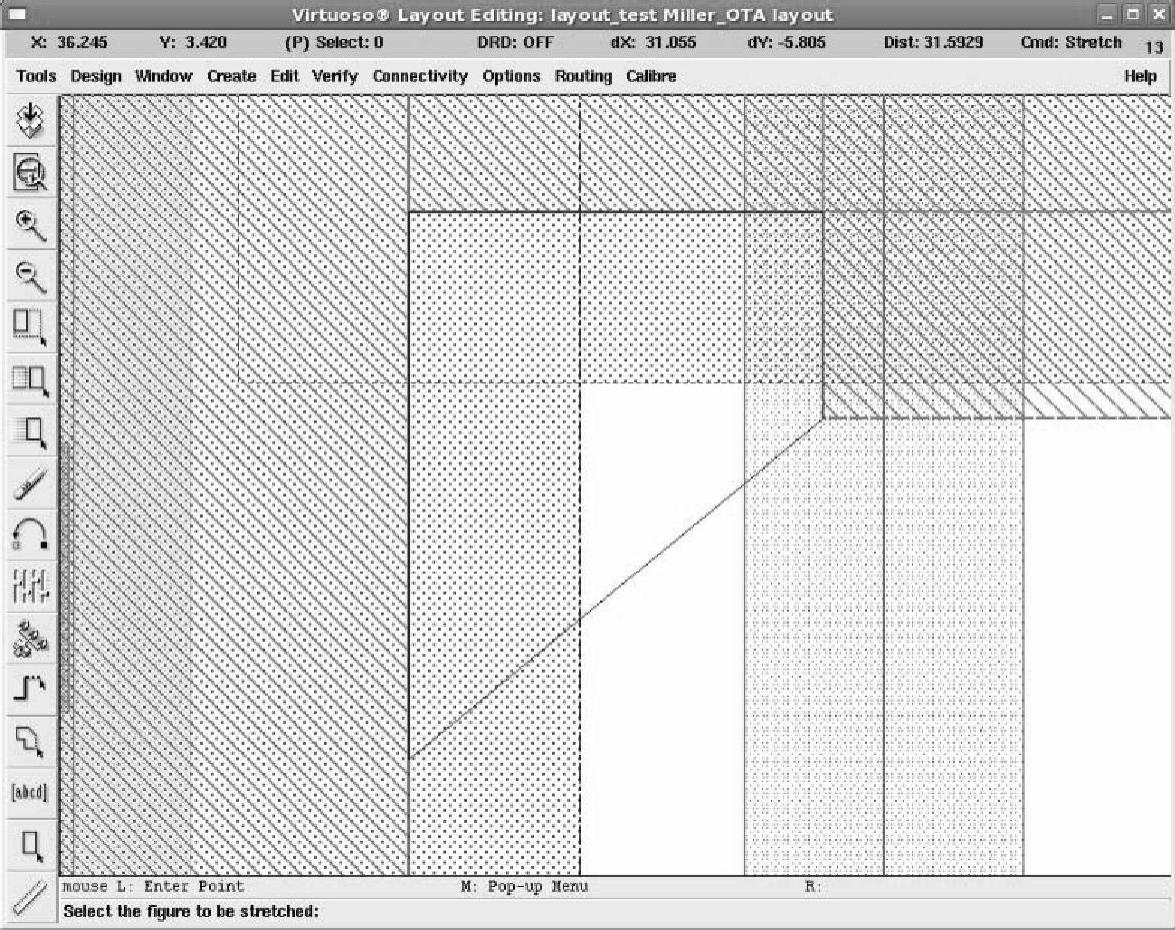

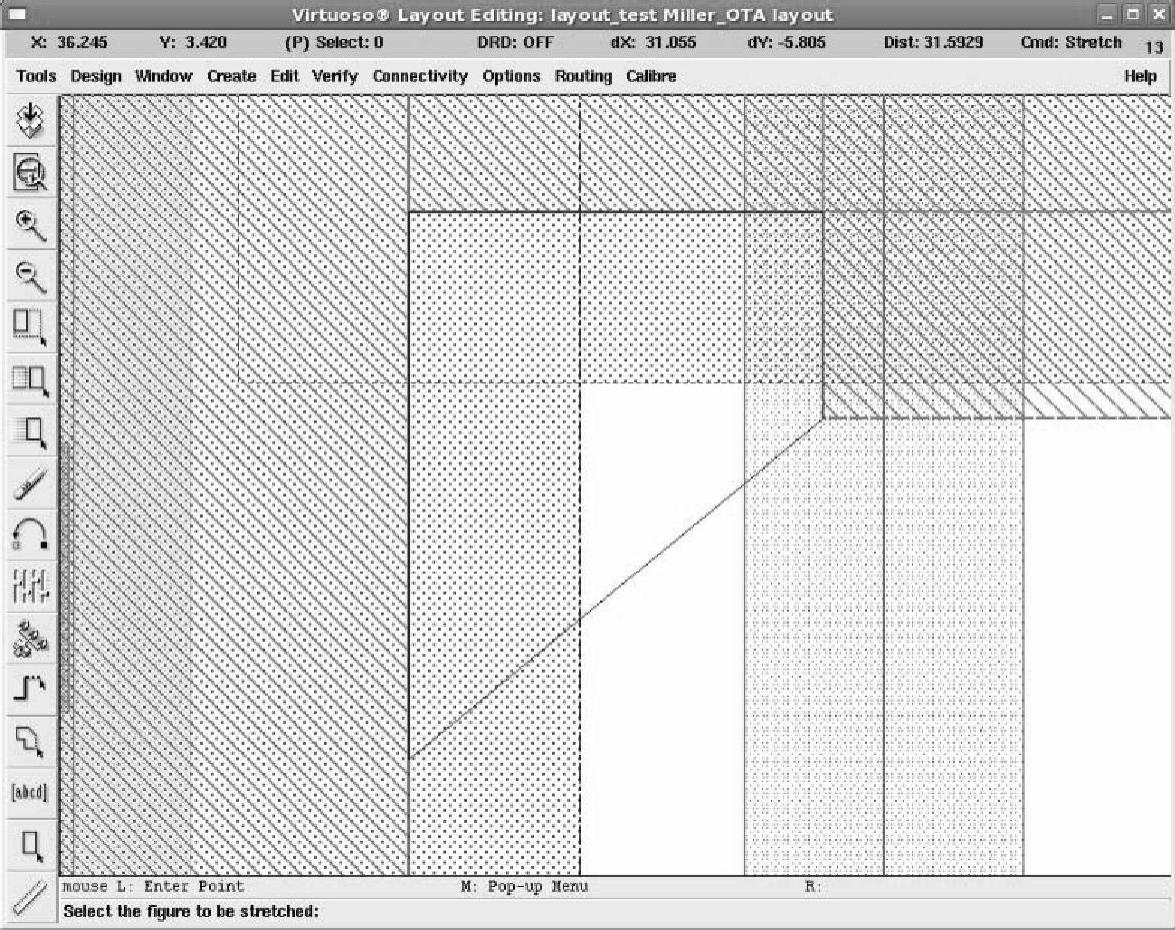

11)错误1修改。鼠标左键单击错误报告窗口Check SN2-1 Result,并双击下属菜单中的01,错误文本显示窗口显示设计规则路径(Rule File Pathname:/export/home1/user/drc/SmicDR8P7Pcal018mixlogsalip1mt61833.drc)以及违反的具体规则(Minimum space between two SN regions is less than 0.44um),DRC结果查看图形界面如图4.35所示,其版图DRC错误定位如图4.36所示。

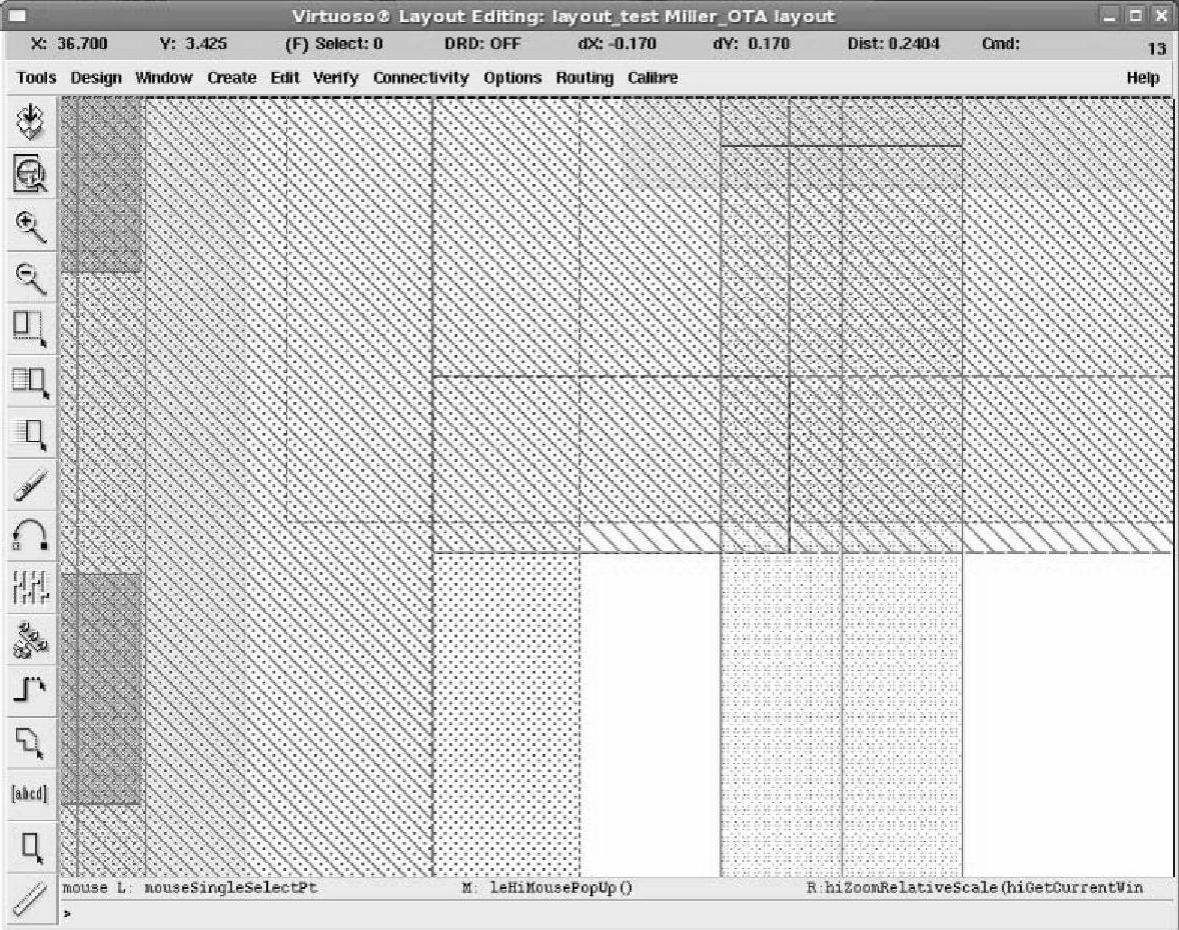

12)根据提示进行版图修改,将两个SN区合并为一个,就不会存在间距问题,修改后的版图如图4.37所示。

13)错误2修改。鼠标左键单击错误报告窗口Check M31-1 Result,并双击下属菜单中的01,错误文本显示窗口显示设计规则路径(Rule File Pathname:/export/home1/user/drc/SmicDR8P7Pcal018mixlogsalip1mt61833.drc)以及违反的具体规则(Minimum width of an M3 region is 0.28um),DRC结果查看图形界面如图4.38所示,版图错误定位如图4.39所示。

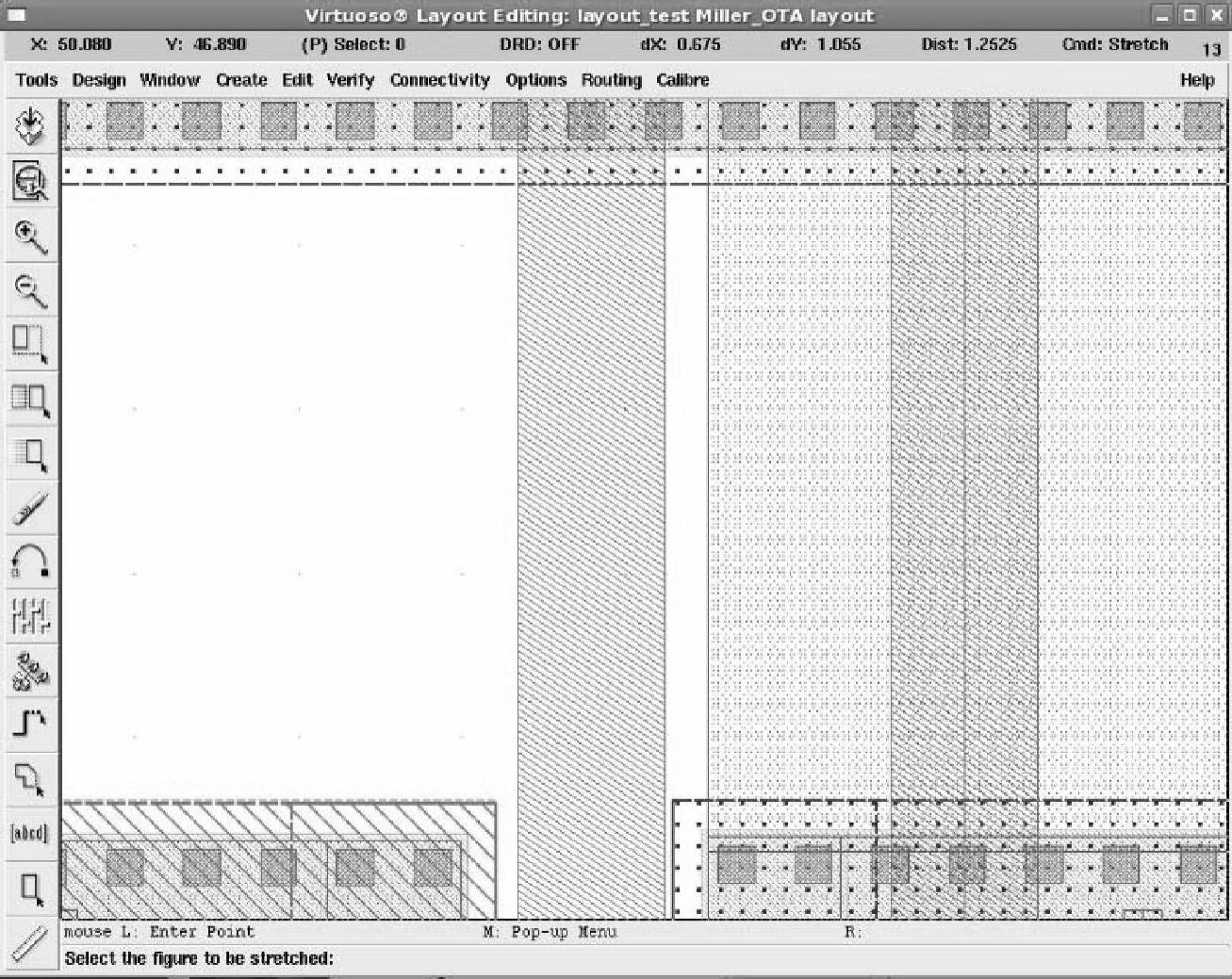

14)根据提示进行版图修改,将M3的线宽加宽,满足最小线宽要求,修改后的版图如图4.40所示。

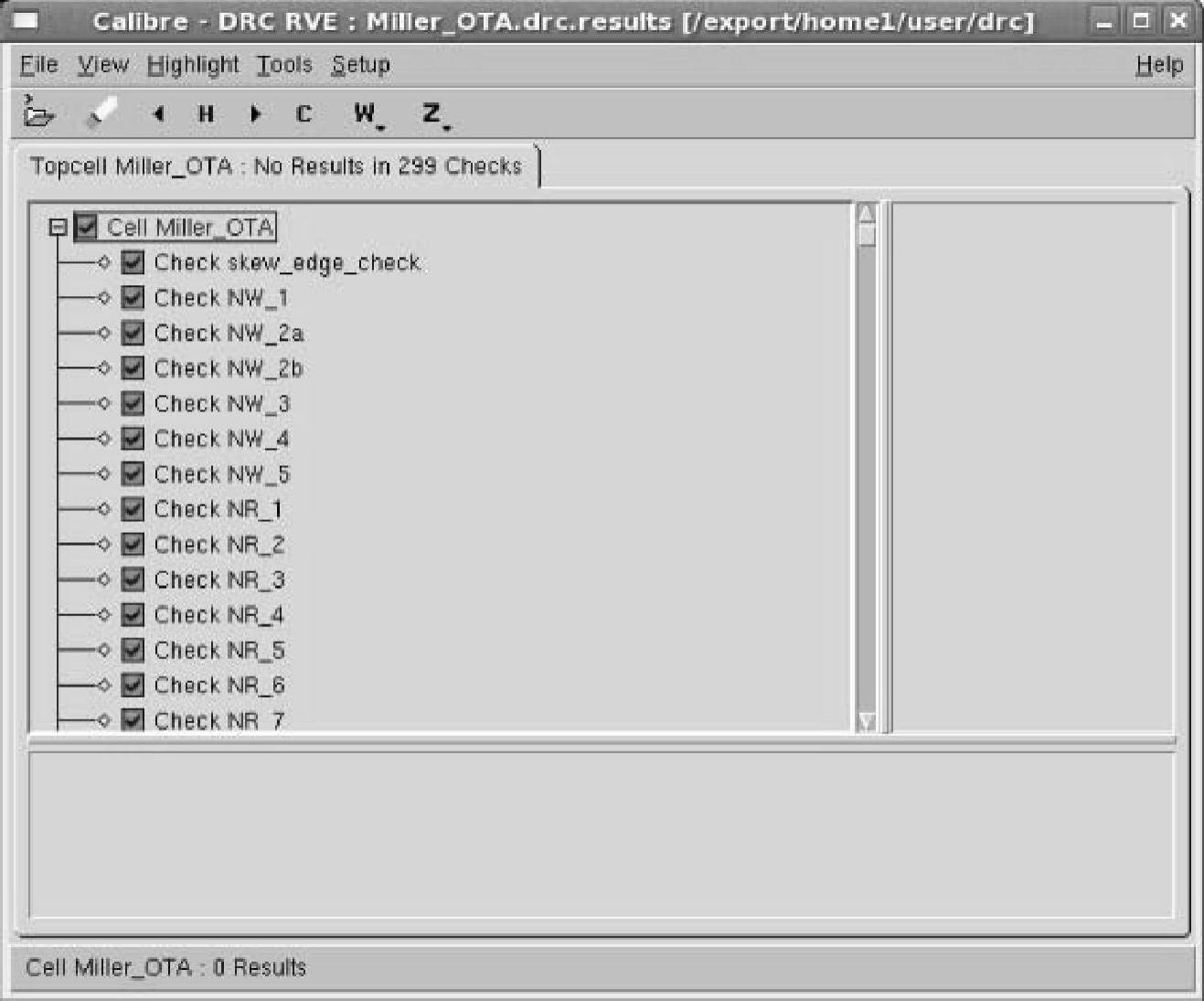

15)DRC错误修改完毕后,再次做DRC,直到所有的错误都修改完毕,直到出现如图4.41所示的界面,表明DRC已经通过。

图4.35 DRC结果查看图形界面

图4.36 相应版图错误定位

图4.37 修改后版图

图4.38 DRC结果查看图形界面

图4.39 相应版图错误定位

图4.40 修改后版图

图4.41 Calibre DRC通过界面

以上完成了Calibre DRC的主要流程。通常设计时会出现多种DRC错误,需要设计者反复性地进行修改。特别要注意的是,在单个电路设计时,往往会出现金属、多晶硅或者电容层密度不足的DRC错误。这时一般可以忽略,待到整体芯片设计时再进行Dummy金属、多晶硅和电容层的填充,使其满足密度的最小规则。

相关推荐