要想彻底理解单片机P0口加上拉电阻的问题,必须要从P0端口的结构及工作原理入手。51系列单片机有4个双向的8位并行I/O端口,分别记作P0、P1、P2、P3,共有32根端口线。这是针对最早的MCS-8051系列来说的,现在国内最新的STC公司生产的12系列、15系列的单片机对此有新的定义,读者可自行查阅相关资料进行了解。......

2023-11-17

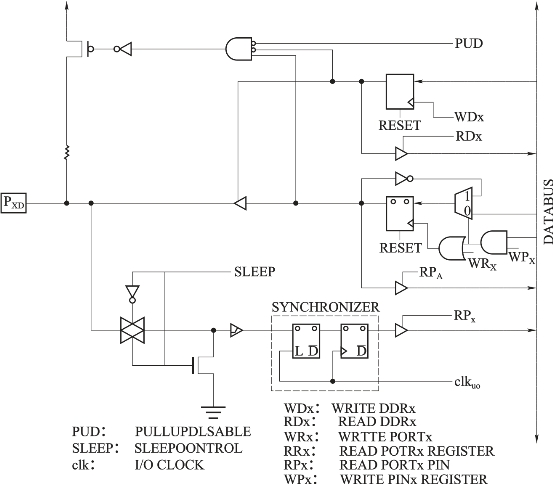

作为通用数字I/O使用时,AVR所有的I/O端口都具有真正的读—修改—写功能。这意味着用SBI或CBI指令改变某些管脚的方向(或者是端口电平、禁止/使能上拉电阻)时不会改变其他管脚的方向(或者是端口电平、禁止/使能上拉电阻)。输出缓冲器具有对称的驱动能力,可以输出或吸收大电流,直接驱动LED。所有的端口引脚都具有与电压无关的上拉电阻,并有保护二极管与V CC和地相连,如图4-41所示。

图4-41 I/O引脚等效原理图

本节所有的寄存器和位以通用格式表示:小写的“x”表示端口的序号,而小写的“n”代表位的序号,但是在程序里要写完整。例如,PORTB3表示端口B的第3位,而本节的通用格式为PORTxn。每个端口都有三个I/O存储器地址:数据寄存器ORTx、数据方向寄存器——DRx和端口输入引脚——INx。数据寄存器和数据方向寄存器为读/写寄存器,而端口输入引脚为只读寄存器。但是需要特别注意的是,对PINx寄存器的某一位写入逻辑“1”将造成数据寄存器相应位的数据发生“0”与“1”的交替变化。当寄存器MCUCR的上拉禁止位PUD置位时所有端口的全部引脚的上拉电阻都被禁止,多数端口引脚是与第二功能复用的。通用数字I/O的端口为具有可选上拉电阻的双向I/O端口。图4-42所示为通用数字I/O。

图4-42 通用数字I/O

说明:(1)WRx、WPx、WDx、RRx、RPx和RDx对于同一端口的所有引脚都是一样的。clk I/O、SLEEP和PUD则对所有的端口都是一样的。

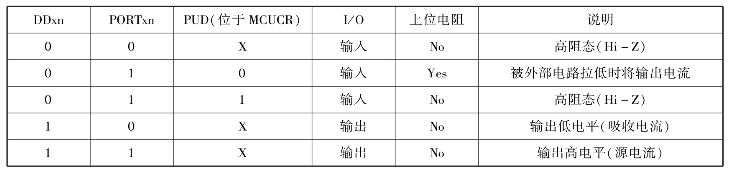

(2)配置引脚每个端口引脚都具有三个寄存器位:DDxn、PORTxn和PINxn,如P75“I/O端口寄存器的说明”所示。DDxn位于DDRx寄存器,PORTxn位于PORTx寄存器,PINxn位于PINx寄存器。DDxn用来选择引脚的方向,当DDxn为“1”时,Pxn配置为输出;否则为输入。引脚配置为输入时,若PORTxn为“1”,上拉电阻使能。如果需要关闭这个上拉电阻,可以将PORTxn清零,或者将这个引脚配置为输出。复位时各引脚为高阻态,即使此时并没有时钟在运行。

(3)当引脚配置为输出时,若PORTxn为“1”,引脚输出高电平(“1”),否则输出低电平(“0”)。使引脚电平交替变化,不论DDRxn是什么内容,向PINxn写逻辑“1”就会使PORTxn的值在“0”和“1”来回变化。注意SBI指令能够用来改变端口的单个位。

(4)输入与输出之间的切换在(高阻态)三态({DDxn,PORTxn}=0b00)和输出高电平({DDxn,PORTxn}=0b11)两种状态之间进行切换时,上拉电阻使能({DDxnPORTxn}=0b01)或输出低电平({DDxn,PORTxn}=0b10),这两种模式必然会有一个发生。通常,上拉电阻使能是完全可以接受的,因为高阻环境并不在乎是强高电平输出还是上拉输出。如果实际应用环境不允许这样,则可以通过置位MCUCR寄存器的PUD来禁止所有端口的上拉电阻。在上拉输入和输出低电平之间切换也有同样的问题。用户必须选择高阻态({DDxn-PORTxn}=0b00)或输出高电平({DDxn,PORTxn}=0b11)作为中间步骤,如表4-15所示。

表4-15 端口引脚配置

有关工业机器人基础的文章

要想彻底理解单片机P0口加上拉电阻的问题,必须要从P0端口的结构及工作原理入手。51系列单片机有4个双向的8位并行I/O端口,分别记作P0、P1、P2、P3,共有32根端口线。这是针对最早的MCS-8051系列来说的,现在国内最新的STC公司生产的12系列、15系列的单片机对此有新的定义,读者可自行查阅相关资料进行了解。......

2023-11-17

1.端口特性每个通用I/O端口包括4个32位配置寄存器、2个32位数据寄存器、1个32位置位/复位寄存器、1个32位锁定寄存器和2个32位复用功能选择寄存器。可为每个I/O选择不同的速度。2.端口使用1)复位后的I/O引脚在复位期间及复位刚刚完成后,复用功能尚未激活,I/O端口被配置为输入浮空模式。这可以确保共用同一个I/O引脚的外设之间不会发生冲突。置位复位寄存器的大小是GPIOx_ODR的2倍。在对GPIOx_ODR进行位操作时,软件无须禁止中断。......

2023-11-21

定时器/计数器2称为专用定时器/计数器,它的输入连接引脚为IO4,而输出引脚连接IO1。定时器/计数器的时钟信号以及使能信号可来自外部I/O引脚,也可由系统时钟分频得到。两个定时器/计数器的时钟速率互相独立。如果一个定时器/计数器被定义来实现一个输出对象或一个正交输入对象,它就不能在同一个应用中被定义为其他的定时器/计数器对象。定时器/计数器I/O对象和并行双向I/O对象的详细介绍请参考相关资料。......

2023-11-22

所谓I/O接口也就是输入/输出接口。根据信号传输方式的不同,I/O接口一般可分为并行接口和串行接口两种方式。通常所说的并行接口一般称为Centronics接口,也称为IEEE1284标准。当传输距离较远、位数又多时,并行接口会导致通信线路复杂且成本提高。图5-13所示为各类并行接口及并行电缆,传输的是数字量和开关量。串行接口按电气标准及协议来分包括RS-232-C、RS-422、RS-485等。......

2023-06-23

函数选板中文件I/O选板上的VI和函数可用于常见文件I/O操作,如读写以下类型的数据:在电子表格文本文件中读写数值;在文本文件中读写字符;从文本文件读取行;在二进制文件中读写数据。可将读取文本文件、写入文本文件函数配置为可执行常用文件I/O操作。如“文件I/O”VI和函数被设置为执行多项操作,则每次运行时都将打开关闭文件,所以尽量不要将它们放在循环中。下面对文件I/O选板中的节点进行介绍。......

2023-11-26

本节讲述PCIe总线定义的各类TLP,并详细介绍这些TLP的格式。在PCIe总线中,存储器读写,I/O读写和配置读写请求TLP由以下几类报文组成。存储器读请求TLP和读完成TLP当PCIe主设备,RC或者EP,访问目标设备的存储器空间时,使用Non-Posted总线事务向目标设备发出存储器读请求TLP,目标设备收到这个存储器读请求TLP后,使用存储器读完成TLP,主动向主设备传递数据。PCIe主设备仅使用存储器写请求TLP即可完成DMA写操作,主设备不需要目标设备的回应报文。......

2023-10-20

具体I/O分配画面布局如图3-3所示。图3-2 I/O分配如果未对点数进行选择,则使用实际安装模块的点数。对于未进行起始XY设置的插槽,则从当前I/O编号的末尾开始以连号方式进行分配。......

2023-06-15

I/O模块是输入模块和输出模块的总称,按实际控制所需的I/O来确定模块规格及数量。实际系统配置时,I/O模块可多可少,但其最大模块数受到CPU单机所能控制的最大I/O点数限制。常见的I/O模块外形如图2-9所示。注意,设定方法请查看本书8.6节4.I/O模块输入响应速度的变更。Q系列PLC常见I/O模块的性能见表2-7。......

2023-06-15

相关推荐