主要用于制作包装箱的高密度聚乙烯钙塑格子板应用广,市场需求大,其生产设备与聚碳酸酯中空格子板生产设备相同,只是工艺流程和工艺设计稍有不同。粒料→塑化→挤出→真空成型→冷却定型→牵引→切割→检验→钙塑格子板。钙塑格子板→分切→模切→印刷→打钉→检验→捆扎→包装箱成品入库。高密度聚乙烯钙塑格子板原料配方(质量份)HDPE,100;改性剂,5~10;CaCO3,20~60;偶联剂,1~5;其他,适量。......

2023-06-15

高密度可编程逻辑器件的编程设计主要采用在系统编程(In System Programmable,ISP)技术。

1)ISP的基本原理和意义

ISP技术不需要编程器,只需要通过计算机接口和编程电缆,就可直接对装配在目标系统或线路板上的PLD器件进行编程。器件成为产品后有些还可反复编程。

通常把一次性编程的(如PROM)称为第一代PLD,把紫外线擦除的(如EPROM)称为第二代PLD,把电擦除的(采用E2CMOS工艺如GAL)称为第三代PLD。第一、第二、第三代PLD器件的编程都是在编程器上进行,第四代PLD器件采用ISP技术编程。

ISP技术主要应用在ISP-PLD(简称ISP器件)器件的编程设计中。ISP器件是一种可由用户根据所设计的数字系统的要求,在开发系统软件的支持下,在系统上直接定义和修改其逻辑功能的高容量的集成电路。第8.2节和第8.3节中介绍过的isp LSP和FPGA器件都属于ISP器件。由于ISP器件能满足现代数字系统的大容量、高速度、先装配、现场反复编程的要求,其应用日趋广泛。

在系统编程时由于器件插在系统的线路板上,器件各端口与电路其他部分相连,编程时须用系统电源使系统处于工作状态,因此在系统编程的关键问题是ISP器件编程时如何与不必要的外部联系脱离。ISP器件都有一个编程使能信号端(isp EN),该端加无效电平时,器件与外电路相连;该端加有效电平时,器件所有I/O端的三态缓冲器皆处于高阻状态,切断了芯片与外电路的不必要的联系,这时即可对芯片进行编程。

编程使能信号、编程数据和其他命令、方式控制信号都是由开发系统软件通过计算机并口提供,用编程电缆连接到器件上。器件在编程时将有关输出反馈给计算机,以便对编程数据进行校验。ISP技术使数字系统设计的程序发生了根本变革,使硬件设计软件化。现代数字系统设计已进入电子设计自动化(Electronic Design Automation,EDA)时代。

利用ISP技术,可以先制作样机底板,并将部件和元器件全部安装在底板上,再用ISP开关器件按预定功能将它们连接起来,并按系统要求现场编程。如想改变设计,无须改变器件和线路,通过开发系统即可很快完成,这就大大缩短设计周期,降低成本。而且,硬件设备可以制成具有一定程度通用性的多功能硬件,利用ISP技术根据具体应用场合即可重构其功能。

高密度PLD器件引脚多、间距密,若多次插接,很容易造成引脚损伤。ISP技术使PLD器件一次安装,避免了引脚损伤,简化了工序,提高了系统可靠性。利用ISP技术,对系统的测试、维护和升级只要在现场用PC机和软件即能实现。

2)ISP器件的编程设计流程

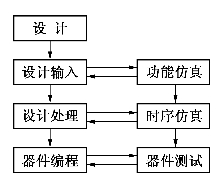

图8.18 ISP器件的编程设计流程

ISP器件的编程设计流程如图8.18所示。下面做进一步说明。

(1)设计阶段。主要是进行设计方案论证、系统设计和器件选择等工作。

数字系统设计可以采用模块设计法、自顶向下(Top-Down)设计法和自低向上设计法。其中,自顶向下设计法是目前常用的设计法,即首先从系统总功能入手,在顶层进行功能划分和结构设计,采用硬件描述语言对高层次的系统进行描述,并在系统级用仿真手段验证设计的正确性,然后再逐级设计至底层。这种层次化设计方法支持模块化设计,底层模块可以反复被调用。

(2)设计输入阶段。设计者须将所设计的系统或电路,按所选用的芯片及其相应可编程逻辑器件开发软件系统所要求的某种形式表示出来,并输入计算机。现在各PLD生产公司的可编程逻辑器件开发软件系统都支持以下方式:

①原理图(Schematic)输入方式:即在开发软件相关界面中使用开发系统提供的元器件库及各种符号和连线画出原理图的输入方式;

②硬件描述语言输入方式:即在开发软件相关界面中采用硬件描述语言例如VHDL、Verilog-HDL、AHDL等行为描述语言描述系统行为的文本输入方式;

③波形输入方式:即在开发软件相关界面中建立和编辑波形设计文件以及输入仿真向量和功能测试向量的输入方式。

以上三种设计输入方式中,第①种方式最直观,容易实现仿真,便于观察信号和调整电路,但在系统复杂时效率低。第②种方式优点最突出,便于实现复杂系统设计,效率高,是当前的使用趋势。

(3)设计处理阶段。通过运行所使用的开发系统中的编译软件,对设计输入文件基本自动地进行下列处理:

①语法检查和设计规则检查:例如检查原理图有无漏连信号线,信号有无双重来源,文本输入文件中关键字有无输错等语法错误;设计规则检验总的设计有无超出器件资源或规定的限制。如有错误,编译过程中会及时列出供设计者修改。

②逻辑优化和综合:编译软件会自动化简所有的逻辑方程式或用户自建的宏,使设计占有资源最少;而且软件会将多个模块化设计文件合并综合为一个网表文件,使层次设计平面化。

③适配和分割:确定优化后的逻辑设计能否与器件的宏单元和I/O单元适配,然后将设计分割为多个便于适配的小逻辑块形式映射到器件的相应宏单元中。如果整个设计不能装入一个芯片,可以将其或自动、或由用户控制(部分或全部)分割成多块装入同系列的多片器件中。

④布局和布线:该项工作是在设计检验通过以后,由软件以最优的方式对所设计的系统进行布局和布线,并最后生成布线报告,提供有关设计中各部分资源的使用情况等信息。

⑤生成编程数据文件:这是编程处理的最后一步,产生可供器件编程用的数据文件,对CPLD器件是产生JEDEC文件;对于FPGA器件是生成位流数据文件(Bitstream Generation)。

(4)功能仿真和时序仿真设计校验:这两项工作是在设计处理过程中同时进行的。

功能仿真在设计输入完成之后,选择具体器件进行编译之前进行,又称前仿真。仿真前,要先利用波形编辑器建立波形文件,或用硬件描述语言建立测试向量,仿真结果将会生成输出信号波形和报告文件,从中可观察到各个节点的信号变化,若发现错误,则返回设计输入中修改设计。

时序仿真是在选择了具体器件并完成布局布线后进行,又称后仿真或延时仿真,这时的仿真,与器件的内部延时、具体的布局布线都密切相关,是与实际器件工作情况基本相同的仿真,对预测所设计的系统的性能和检查消除竞争冒险等很有必要。

(5)器件编程:将器件按编程数据和编程命令选择某种方式进行编程。

3)ISP器件的编程方式

(1)在PC机上利用PC机的接口和下载电缆对ISP器件编程

这种方法适用于多种ISP器件。在ISP器件的相应开发软件支持下,利用一根编程电缆(又称下载电缆)将PC机的接口与系统板上的ISP器件相连,将编程信号通过电缆传送给ISP器件。可以利用串口的BitBlaster串行下载,或利用并口的ByteBlaster并行下载,这对Altera公司的CMOS结构的MAX7000系列器件或SRAM结构的FLEX系列器件都适用。

也可以脱离ISP的开发环境,根据编程时序的要求,利用自己的软件向ISP器件内写入编程数据。这种编程方法多适用于易失性的SRAM结构的FPGA器件。

(2)利用用户系统板上自备的单片机或微处理器对板上的ISP器件编程

这种方法多适用于SRAM结构的FPGA器件。首先将编程数据存储在用户系统板上的EPROM中,板上微机从EPROM中读出编程数据并进行相应转换,ISP信号则由微机地址译码或I/O口产生(应事先对其I/O口进行定义);然后编制读写这些I/O口的程序,使ISP器件编程过程成为软件对这些口的读写过程,当系统板上电时自动对ISP器件进行编程。编程的关键在于提供准确定时的编程时钟。

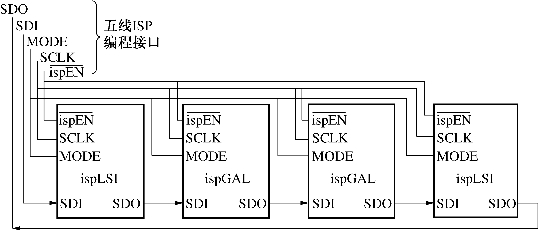

(3)多芯片ISP编程

这种编程方式如图8.19所示,是一种串行编程方式,称为菊花链结构(Daisy Chain),各片ISP器件共用一套ISP编程接口,各ISP器件的输入端SDI和输出端SDO依次串接,构成类似移位寄存器的串行编程方式。

图8.19 多芯片ISP编程

4)ISP器件编程设计的基本过程

(1)计算机在相应开发系统软件环境下运行源程序,产生相应的编程数据和编程命令。

(2)通过编程接口使芯片与计算机相连,接口电路有电源端、接地端、编程使能信号端![]() 模式控制信号端MODE、串行时钟输入端SCLK、串行数据和命令输入端SDI以及串行数据输出端SDO。

模式控制信号端MODE、串行时钟输入端SCLK、串行数据和命令输入端SDI以及串行数据输出端SDO。

(3)器件按编程数据和编程命令编程。![]() 为低电平时,芯片进入编程状态,此时所有IOC的输出三态缓冲器均被置为高阻态;

为低电平时,芯片进入编程状态,此时所有IOC的输出三态缓冲器均被置为高阻态;![]() 为 高电平时,芯片处于正常工作状态。SCLK为片内接受输入数据的移位寄存器和控制编程操作的时序逻辑电路提供时钟信号。

为 高电平时,芯片处于正常工作状态。SCLK为片内接受输入数据的移位寄存器和控制编程操作的时序逻辑电路提供时钟信号。

在MODE和SDI信号控制下,计算机运行编程数据和命令,以串行方式进入芯片内的控制编程操作的时序逻辑电路。数据在写入的同时,又以串行方式从SDO读出并送回计算机,以便进行校验和发送下面的命令和数据。

有关数字电子技术的文章

主要用于制作包装箱的高密度聚乙烯钙塑格子板应用广,市场需求大,其生产设备与聚碳酸酯中空格子板生产设备相同,只是工艺流程和工艺设计稍有不同。粒料→塑化→挤出→真空成型→冷却定型→牵引→切割→检验→钙塑格子板。钙塑格子板→分切→模切→印刷→打钉→检验→捆扎→包装箱成品入库。高密度聚乙烯钙塑格子板原料配方(质量份)HDPE,100;改性剂,5~10;CaCO3,20~60;偶联剂,1~5;其他,适量。......

2023-06-15

高密度聚乙烯燃气管概述 高密度聚乙烯燃气管主要用作输送煤气、液化气和天然气。表3-16 高密度聚乙烯燃气管专用树脂的性能要求生产设备 高密度聚乙烯燃气管生产中用的挤出机为单螺杆挤出机,螺杆结构采用等距不等深渐变型螺杆,长径比L/D为25~35,压缩比为2~3。表3-17 高密度聚乙烯燃气管生产中异常现象、产生原因及解决方法④为提高HDPE燃气管的强度,管坯成型后应采用迅速冷却降温法,可使管材结晶度小,制品表面有光泽。......

2023-06-15

X射线衍射仪必须要有合适的X射线源,不同的样品对X射线源有不同的要求。X射线光源可分为普通X射线源和同步X射线源。目前世界上的第三代光源共有14台,包括位于上海浦东的同步辐射光源。图4-6上海光源结构平面示意图与一般X射线源相比较,同步辐射光源有如下特征:高强度(高亮度):图4-7为各种不同类型的X射线的亮度比较。图4-7同步辐射光源光子亮度的进展和比较......

2023-06-20

从式可以看到,电流正反馈Ui的作用相当于增加了转速给定值,因此称为电流补偿控制。因为βcr受放大倍数和电阻等诸多因素的影响,这些因素稍有变化,全补偿状态就可能被破坏,使系统不稳定,所以通常只使用欠补偿控制。关于电流补偿控制的讨论如下:1)电流补偿只是针对负载扰动的一种补偿措施。这时,电流正反馈补偿不仅没有抑制转速上升,反而是助长了转速上升,起了相反的作用。补偿控制也常用于温度等其他控制场合。......

2023-06-19

焊接工装是焊接设备为满足产品结构要求确保正常运转的关键手段,是保证生产有序开展的重要环节。根据TSGG0001《锅炉安全技术监察规程》中第4.3.2条规定的焊接工艺评定范围:“锅炉产品焊接前,施焊单位应当对以下焊接接头进行焊接工艺评定:①受压元件......

2023-07-02

测试步骤①标准液的配制:准确称取5 mg牡荆素、牡荆素鼠李糖苷和异牡荆素,转移至100 mL容量瓶中,加入60 mL甲醇,超声5 min,冷却后加入甲醇至刻度,摇匀即可注射。UPLC的条件色谱柱:Acquity UPLCBEH C18,1.7μm,2.1×100 mm流速:0.4 mL/min注射量:1μLUV检测波长:340 nm移动相A:0.1%磷酸水溶液移动相B:130 mL甲醇加70 m L乙醇柱温:45℃梯度:图4-15山楂标准品的色谱图结果计算牡荆素鼠李糖苷、异牡荆素的计算公式同上。......

2023-07-02

装配协调方案的内容包括结构介绍、装配方案、协调方案三部分。图6-2装配顺序图表格式主要零件、组件、分部件的定位基准及定位方法①装配基准的选择:确定以骨架为基准或以蒙皮为基准的装配。②零组件、分部件、部件协调互换部位的余量大小及容差。③采用数值量协调方法的范围、协调内容及与模拟量传递协调方法的衔接关系。④标准实样的协调内容及取制条件。③零件在检验工装内的定位基准、检查部位、检查方法及检验容差。......

2023-07-18

相关推荐