图1-12所示为屏蔽同轴电缆的图形符号,它是由表示屏蔽的符号要素“”与同轴电缆的基本图形符号“”组成的。......

2023-06-23

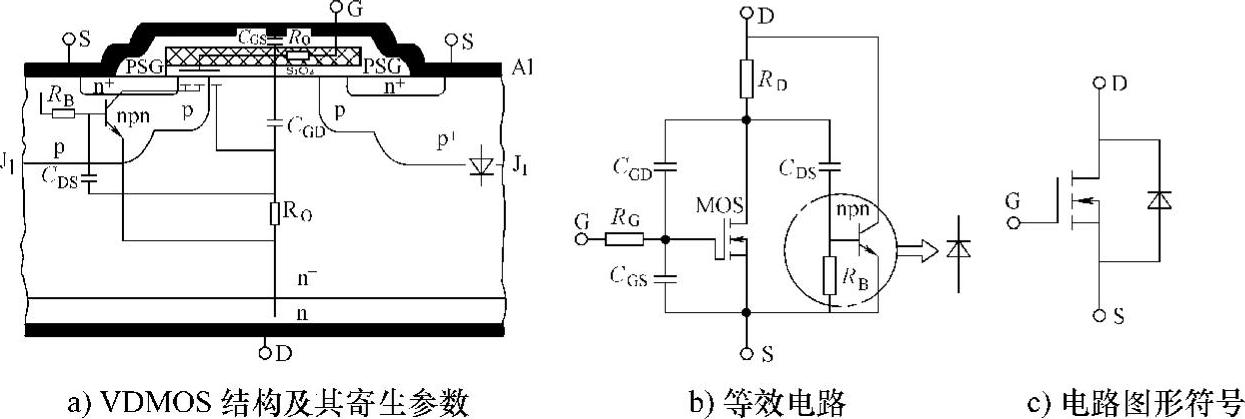

VDMOS结构的等效电路及电路图形符号如图4-5所示。除了有一个寄生的npn晶体管外,还有一些寄生电容和电阻。其中npn晶体管的发射区、基区及集电区分别为n+源区、p体区及漏区。寄生电容包括栅-源电容CGS、栅-漏电容CGD、漏-源电容CDS,寄生电阻包括多晶硅栅极电阻RG、npn晶体管的p体区横向电阻RB及n-漂移区电阻RD。当VDMOS工作时,如果寄生的npn晶体管导通,会导致其栅极失控而失效。为了避免寄生的npn晶体管导通,通常将p体区和发射区通过源区金属化短路,并缩小源区尺寸,或者在元胞制作之前先通过B+注入或扩散形成一个较深的p+阱区(见图4-5a),以限制其p体区的横向电阻RB。由于这种设计要求,使得VDMOS的源极与漏极之间寄生了一个pin二极管,其中p+阱区为阳极,n+漏极区为阴极,通常称该二极管为体二极管。当VDMOS漏、源之间加很高的正向电压时,体二极管首先发生穿通击穿,可以起到过电压保护作用;当漏、源之间加反向电压时,体二极管导通,可以起到续流作用。为了减小体二极管的反向恢复特性对VDMOS开关特性的影响,需要对其中的少子寿命进行控制,或采用肖特基接触代替源极欧姆接触而形成MPS二极管[12,13]。

图4-5 VDMOS的寄生参数、等效电路及电路图形符号

此外,因VDMOS采用多个元胞并联,由栅极下方的n-漂移区和两侧的p体区自然形成了一个JFET结构(其中p体区相当于JFET的栅极,n-漂移区相当于沟道),因为在任何工作条件下JFET都不会工作,它只是作为一种寄生电阻效应而存在,故在图4-5a、b中没有标出。

当RB很小时,npn晶体管不工作,相当于一个体二极管(见图4-5b),于是VDMOS相当于一个MOSFET与二极管的反并联,其电路图形符号如图4-5c所示。

有关电力半导体新器件及其制造技术的文章

为了明确和认识光伏电池的光—电转换原理和影响光—电转换效率的因素,必须了解光伏电池的基本结构和特性。若将光伏电池的PN结两端短路,则就会在内部形成短路电流Isc。光伏电池的I-U输出特性如图5-1所示。由图可看出,光伏电池的温度主要影响其开路电压,而对短路电流的影响较小。所以,在PN结为理想状态的情况下,光伏电池可等效为电流源和一个理想二极管的反并联电路。光伏电池的等效电路一般可用图5-4来描述。......

2023-06-23

电路板是电磁炉的重点部件,约有200个元器件。图1-16所示为电磁炉电路板外形。其中,电流互感器是检测电路中电流大小的器件,是将电路中电压量转换为电流量的器件,是控制稳定工作电流的检测部分;二极管的主要作用是将交流转换为直流;电阻的作用是调节反馈电流的比例,从而达到稳定功率的目的。......

2023-06-20

静态分析的任务就是求出IB、IC、UCE,看放大电路是否工作在放大区,是否取得合适的静态工作点。但这种信号可以看成是由许多不同幅值、不同频率的正弦波叠加而成的,所以在调试或测试放大电路时通常都用正弦信号作为输入信号。在实际应用中常用放大电路的微变等效电路分析如图5-15所示。这时要考虑放大电路本身对前后级的影响。......

2023-06-28

图解演示电工原理图也称为电工电路图,也是一种采用图形符号、线条、文字标注等元素组成的一种电路结构,主要用来表现某个设备或系统的基本组成、连接关系以及工作原理的电路图,图3-3所示为典型的电动机点动控制的电工原理图。如测试系统出现故障时,应根据电工原理图的工作过程,分析可能产生故障的大体部位,然后依次对其可能产生故障的元器件进行检测。......

2023-06-24

为了便于光伏电站选用逆变器,这里对方波逆变器、正弦波逆变器和几种功率转换电路作进一步简要说明。但是这种模拟式正弦波逆变器电路结构复杂,电子元件数量多,整机工作可靠性低。图4-24全桥式逆变器电路原理框图高频升压逆变电路。......

2023-07-02

它是由表示屏蔽的符号要素“”与同轴电缆的基本图形符号“”组成的。认识常用电子元器件的图形符号电子元器件是构成电工电路中的基本电子器件,在电路中常见的电子元器件有很多种,且每种电子元器件都用其自己的图形符号进行标识。......

2023-06-22

图2-13 对称三相电压相量图图2-14 三相电源联结电路a)联结 b)△联结基本概念。图2-15 三相对称电源电压相量图图2-16 三相负载联结电路a)-联结 b)△-△联结1)电流:相电流就是线电流。......

2023-11-24

相关推荐