在满足要求的前提下简化结构、减轻重量,使双向DC-DC变换器、测控电路与辅助电源三部分的总重量不大于500 g。制作时应合理设置测试点,以方便测试;为方便测重,应能较方便地将双向DC-DC变换器、测控电路与辅助电源三部分与其他部分分开。......

2025-09-29

基本信息

续表

一、设计方案工作原理

1.方案比较与选择

(1)宽带通道放大器

方案1:OPA690固定增益放大。由于待测信号频率范围广,电压范围大,所以选用宽带运算放大器OPA690,对所有待测信号进行较大倍数的固定增益。对于输入的正弦波信号,经过OPA690的固定增益,小信号得到放大,大信号削顶失真,所以均可达到滞回比较器电路的窗口电压。

方案2:基于VCA810的自动增益控制(AGC)。AGC电路实时调整高带宽压控运算放大器VCA810的增益控制电压,通过负反馈使得放大后的信号幅度基本保持一致。

尽管方案1中的OPA690是高速放大器,但是单级增益仅能满足本题基本部分的要求,而在放大高频段的小信号时,增益带宽积的限制使得该方案无法达到发挥部分在频率和幅度上的要求。

方案2中采用VCA810与OPA690级联放大,并通过外围负反馈电路实现自动增益控制。该方案不仅能够实现稳定可调的输出电压,而且可以避免高频小信号单级放大时的带宽问题。因此,采用基于VCA810的自动增益控制方案。

(2)正弦波整形电路

方案1:采用分立器件搭建整形电路。由于分立器件电路存在着结构复杂、设计难度大等诸多缺点,因此不采用该方案。

方案2:采用集成比较器运放。常用的电压比较器运放LM339的响应时间为1 300 ns,远远无法达到发挥部分100 MHz的频率要求。因此,采用响应时间为4.5 ns的高速比较器运放TLV3501。

(3)主控电路

方案1:采用诸如MSP430、STM32等传统单片机作为主控芯片。单片机在现实中与FPGA连接,建立并口通信,完成命令与数据的传输。

方案2:在FPGA内部利用逻辑单元搭建片内单片机Avalon,在片内将单片机和测量参数的数字电路系统连接,不连接外部接线。

在硬件电路上,用FPGA片内单片机,除了输入和输出显示等少数电路外,其他大部分电路都可以集成在一片FPGA芯片中,大大降低了电路的复杂程度、减小了体积,电路工作也更加可靠和稳定,速度也大为提高。且在数据传输上方便、简单,因此主控电路的选择采用方案2。

(4)参数测量方案

频率等参数的测量采用闸门时间为1 s的等精度测量法。闸门时间与待测信号同步,相比于传统方案,避免了对被测信号计数所产生±1个字的误差,有效提高了系统精度。测量频率时,在闸门时间内同时对待测信号和标准信号(时钟信号)计数,标准信号计数值除以待测信号计数值乘上时钟周期即为待测周期;测量两个信号的时间间隔时,通过异或门将时间间隔转化为周期脉冲信号,通过对脉冲信号等精度测量得到间隔时间。

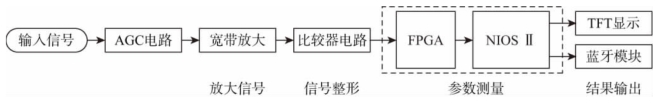

2.系统总体方案描述

系统总体框图如图F-6-1所示,待测信号首先进入自动增益电路,其输出电压增益到一个大于后级滞回比较器窗口电压的固定值,经过比较器电路后,输出给FPGA进行相关参数的测量,并最终显示在屏幕上。在FPGA内部,数字电路系统与片内单片机通信,基于闸门时间为1 s的等精度测量算法,测算相关参数。

图F-6-1 系统总体框图

二、核心电路设计

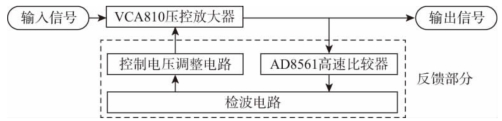

1.宽带通道放大器分析

本设计的宽带通道放大器如图F-6-2所示,是一个自动增益控制模块。

图F-6-2 自动增益模块流程图

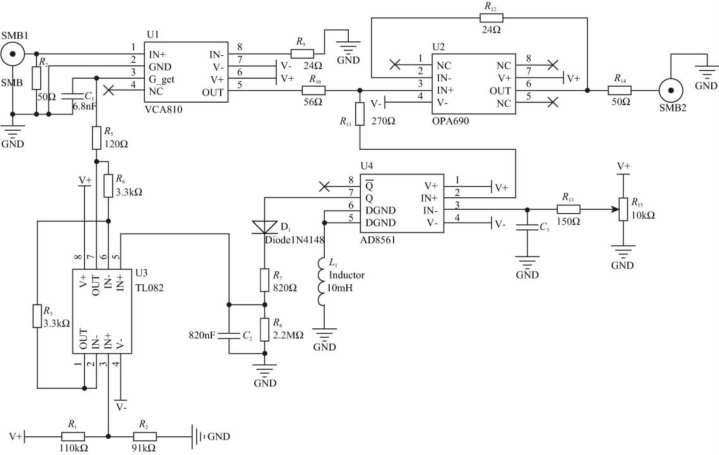

压控放大器VCA810依靠反馈得到的控制电压控制放大倍数;高速比较器AD8561比较的是VCA810输出信号和预设电压,使用二极管和RC对比较器的输出信号进行检波;TL082将检波得到的电压转换至VCA810的控制电压范围内,使得VCA810能够正常工作。具体电路连接如图F-6-3所示。

2.正弦波整形电路

正弦波经过AGC电路后,进入如图F-6-4所示的滞回比较器,整成方波。该电路的窗口电压为![]() ,可有效避免一部分信号干扰。

,可有效避免一部分信号干扰。

图F-6-3 自动增益模块电路图

图F-6-4 滞回比较器

三、系统软件设计分析

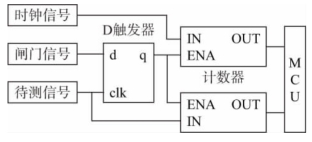

1.频率、周期测量模块

如图F-6-5所示,频率测量模块主要由D触发器和两个带使能端的计数器组成。测量时,采用闸门时间为1 s的等精度测量法。D触发器的应用可确保待测信号的第一个上升沿与闸门信号同步,避免了被测信号计数时产生±1个字的误差,有效提高了系统精度。在闸门时间内同时对待测信号和标准信号(时钟信号)计数,时钟信号计数值除以待测信号计数值乘上时钟周期即为待测信号周期,对周期求倒数即为待测信号的频率。

图F-6-5 频率、周期测量模块

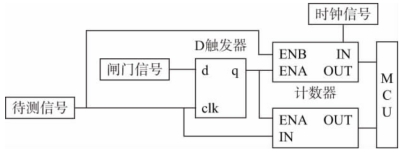

2.方波占空比测量

占空比测量模块在上述方波周期测量模块的基础上又加入了如图F-6-6所示的脉冲宽度测量模块。将待测信号连接到时钟脉冲计数器的使能端上,使得时钟信号计数器只在待测信号正周期的情况下进行计数。

(https://www.chuimin.cn)

(https://www.chuimin.cn)

图F-6-6 脉冲测量模块

从而可以计算方波的占空比。

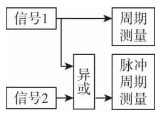

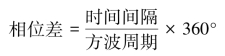

3.时间间隔、相位差测量

如图F-6-7所示,两路同频率方波信号经过一个异或运算模块,得到一路占空比随时间间隔变化的倍频方波信号。用上文所述的脉冲宽度测量模块,对该路信号的脉冲宽度进行测量,所得脉宽时间即为两路信号的时间间隔。

图F-6-7 时间间隔、相位差测量模块

在测量脉冲周期的同时,对任一路信号的周期进行测量,从而可得两路信号的相位差:

四、竞赛工作环境条件

1.设计分析软件环境

TINA,Multisim,FilterPro,Quartus II,NIOS II,Altium Designer。

2.仪器设备硬件平台

(1)信号源:RIGOL DG4102 100 M信号发生器;

(2)示波器:RIGOL DS2202A 200 M数字示波器;

(3)万用表:FLUKE 18B万用电表;

(4)电源:自制±5 V稳压电源。

五、作品成效总结分析

1.基本部分

(1)频率和周期测量功能:被测信号为正弦波,频率范围为1 Hz~10 MHz;有效值电压范围为50 mV~1 V,测量相对误差的绝对值不大于10-4。实测数据完全符合要求。

表F-6-1 频率误差实测数据

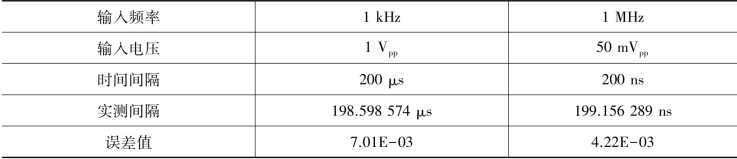

(2)时间间隔测量功能:被测信号为方波,频率范围为100 Hz~1 MHz;峰峰值电压范围为50 mV~1 V;被测时间间隔的范围为0.1 μs~100 ms;测量相对误差的绝对值不大于10-2。实测数据符合要求,如表F-6-2所示。

表F-6-2 时间间隔误差实测数据

(3)测量数据刷新时间不大于2 s,测量结果稳定,并能自动显示单位。实际刷新时间约为1 s。

2.发挥部分

(1)频率和周期测量的正弦波信号频率范围为1 Hz~100 MHz,其他要求同基本要求(1)和(3)。由表F-6-1可知,实测数据满足要求。

(2)频率和周期测量时被测正弦信号的最小有效值电压为10 mV,其他要求同基本要求(1)和(3)。由表F-6-1可知,实测数据满足要求。

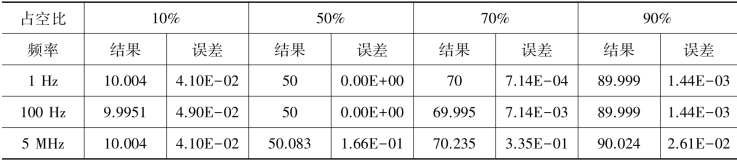

(3)增加脉冲信号占空比的测量功能,要求:a.被测信号为矩形波,频率范围为1 Hz~5 MHz;b.被测信号峰峰值电压范围为50 mV~1 V;c.被测脉冲信号占空比的范围为10%~90%;d.显示的分辨率为0.1%,测量相对误差的绝对值不大于10-2,如表F-6-3所示。

表F-6-3 占空比误差实测数据

3.其他自行发挥部分

(1)频率测量时,即使是微弱信号也可以准确测量。在1 Hz~100 MHz整个频段,输入信号有效值最低可降为5 mVrms;在中频段和低频段,输入信号有效值最低可降为0.7 mVrms;

(2)所有参数测量均采用等精度测量法和自动增益控制,频率测量精度高于发挥部分万分之一的要求,对于大部分频率测量精度可以达到十万分之一;

(3)方波测量占空比和时间间隔时,最低测量的峰峰值可降为10 mV;

(4)频率、时间间隔测量分辨率远超发挥部分要求;

(5)除使用键盘进行人机交互外,增加了蓝牙通信功能,可实现无线控制功能,切换仪器测量模式。

六、参考资料

[1]张永瑞.电子测量技术基础[M].西安:西安电子科技大学出版社,2009

[2]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2013

[3]侯伯亨.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2009

[4]Sergio,Franco.基于运算放大器和模拟集成电路的电路设计[M].西安:西安交通大学出版社,2004

相关文章

在满足要求的前提下简化结构、减轻重量,使双向DC-DC变换器、测控电路与辅助电源三部分的总重量不大于500 g。制作时应合理设置测试点,以方便测试;为方便测重,应能较方便地将双向DC-DC变换器、测控电路与辅助电源三部分与其他部分分开。......

2025-09-29

图9-8 电压均衡电路在这种均压电路中,双向buck-boost变换器分别与相邻的两个超级电容器相连。在第一个充放电循环中,一部分器件可能会超过最大允许电压,但经过几十个充放电循环之后,这组超级电容器至少在满充状态时所有单体的电压可以达到均衡,此后,均压电阻就不再需要了。......

2025-09-29

电解槽的形式多采用矩形。翻腾式的极板采取悬挂方式固定,防止极板与池壁接触,可减少漏电现象,更换极板较回流式方便,也便于施工维修。图3-18电解槽回流式(平面图);翻腾式极板间距对电耗有一定的影响。电源的整流设备应根据电解所需的总电流和总电压进行选择。另外在单极性电解槽中,有可能由于极板腐蚀不均匀等原因造成相邻两块极板碰撞,会引起短路而发生严重安全事故。图3-19电解槽的极板电路单极性电解槽;双极性电解槽......

2025-09-29

密封材料的部分物理性质列于5.7.1节的表格中。添加无机填充物时,粘合剂必须严格是导热的;而添加的金属装料必须是导电并且导热的。此外,在某些条件下,金锡合金可不使用助焊剂,降低了芯片安装时的污染风险。AlN的热导率一般比氧化铝大5~10倍,但因成本较高而应用较少。随着LED功率的增加,就5.2.6.1节中介绍的板上芯片系统而言,衬底的材料从FR4聚合物演变为绝缘金属基板和DBC。但由于有效区与基座上的焊点距离较近,会引发热机械问题。......

2025-09-29

直流电路常见故障有电压、电流过大或过低。交流电路故障及产生原因电子电路中交流电路的故障最容易发生,也是最复杂的,查找这类故障难度更大。这要根据现象和电路原理等具体情况深入进行分析,才能找到故障原因。1)直流故障检查检查直流电路故障有两种情况。一种是新装配的电路,首先要检查是否存在直流电路故障;另一种情况是已经工作的电路出现了故障,要从直流电路方面检查其原因。......

2025-09-29

直流输电系统的发电端与电力输送端之间安装的换流站为整流装置,主要是将交流电转换成直流电,以实现直流电能传输。对输送端而言,作为整流的换流站相当于交流系统的一个负载;而电力接受端和负载用户端之间的换流站为逆变装置,主要用于将直流电逆变成交流电,以便向负载供电。而直流的过载能力往往受制于换流站。如果需要更大的过载能力,则必须在设备选型时预先考虑换流站的容量,但这将会增加建设所需设备的投资。......

2025-09-29

常温下铜的热导率比铁大8倍,在1000℃时铜的热导率比铁大11倍。常用的铜及铜合金有纯铜、黄铜、青铜和白铜等四种。除铍青铜外,其他青铜的导热性比纯铜和黄铜低几倍至几十倍,而且结晶区较窄。......

2025-09-29

图1.43所示是晶闸管-直流电动机开环直流调速系统主电路模型,模型中主要模块提取路径见表1.11。现以例1.2的双闭环控制直流调速系统为例说明。......

2025-09-29

相关推荐