在绘制原理图库时应了解基本绘制工具的用法。这样能保证原理图绘制时引脚连线能连接,且为直线。图5-7 有源晶振图5-8 编辑设置1完成图5-7后会进入图5-9所示的设置界面。图5-9 编辑设置2注意在“Default Dsignator”中输入的是原理图绘制中的位号,这里的命名格式为:“位号名+‘?’”,“?”......

2023-06-23

1.构建层次原理图

图3-45中包含8个集成元件和若干个独立元件,如果要绘制在一张原理图中,显得比较拥挤。此处可以用层次原理图绘制来解决。

首先在DXP软件下新建一个名为单片机系统的PCB工程文件,再添加一个空白原理图,命名为主图,如图3-46所示。

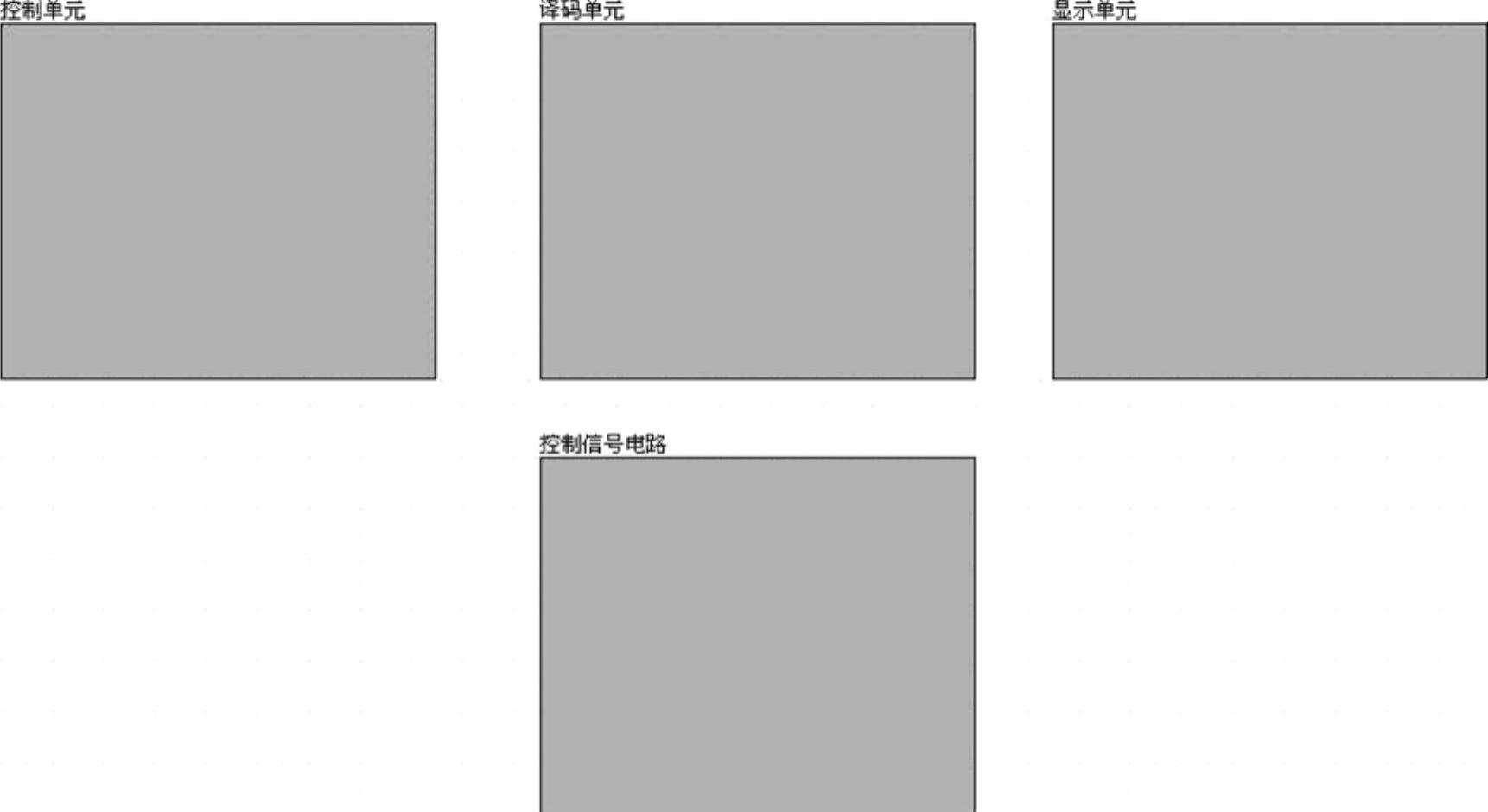

接下来在主图中创建框图符号(Sheet Symbol),如图3-47所示。

图3-46 新建项目和原理图文件

图3-47 新建框图符号

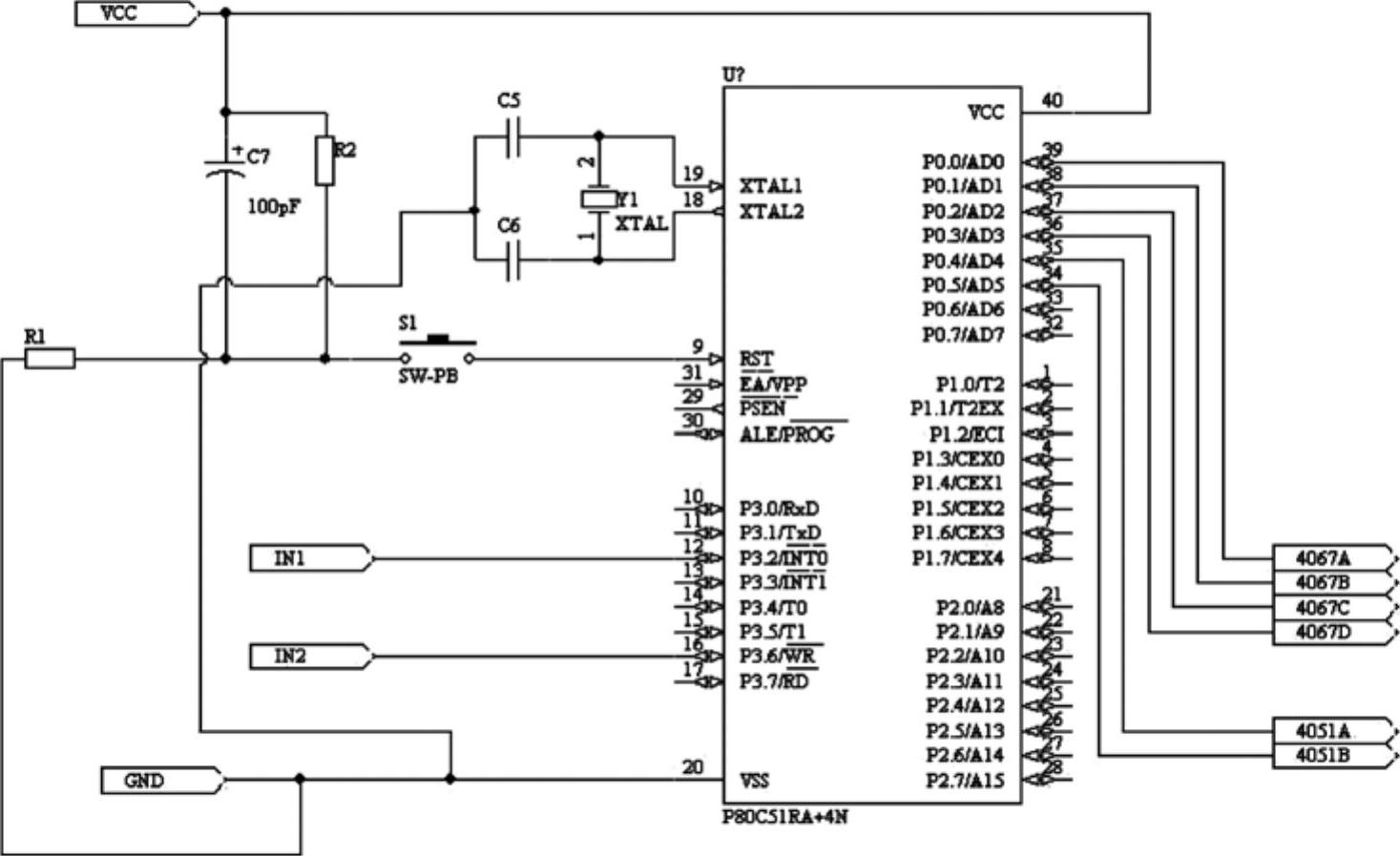

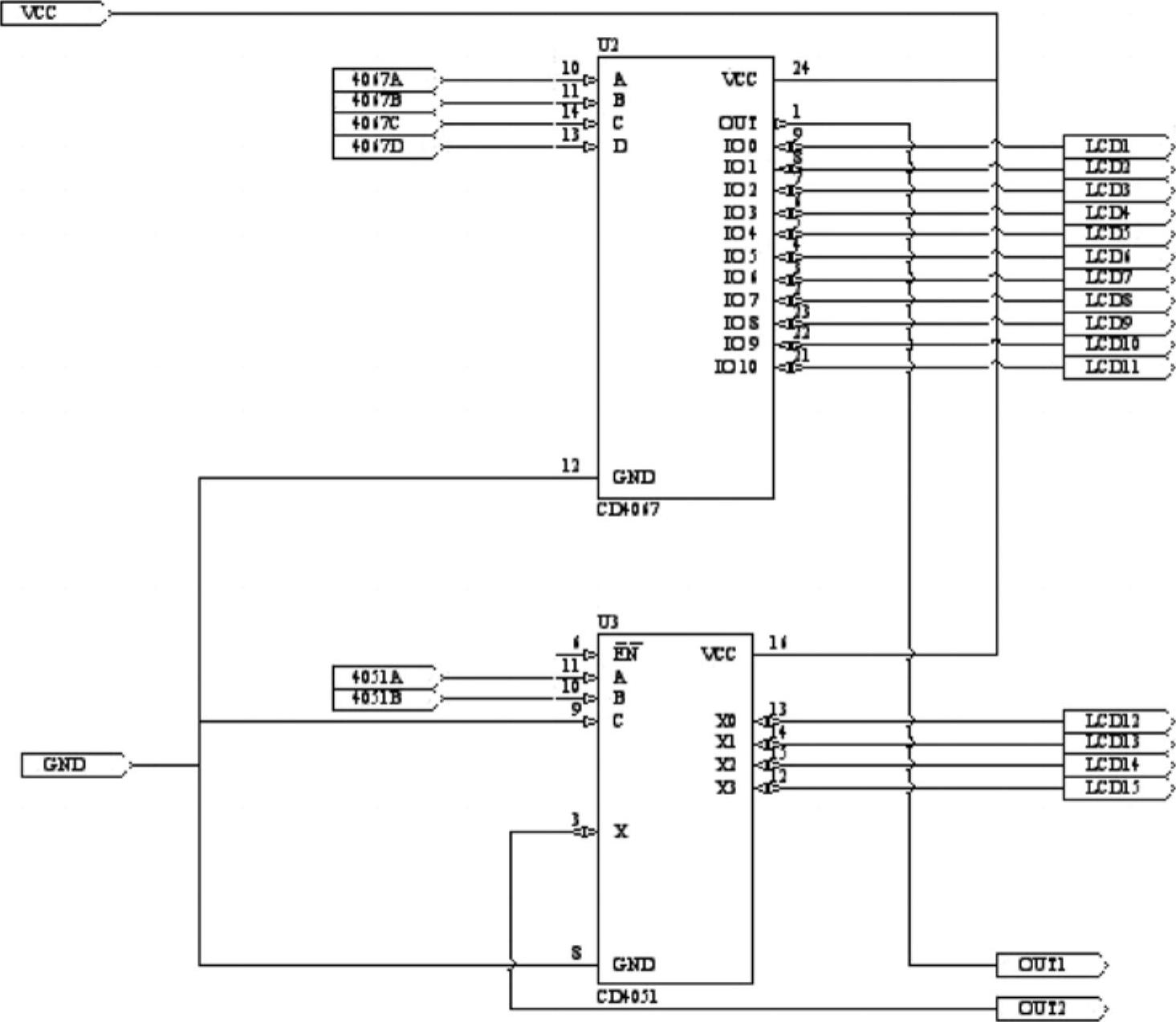

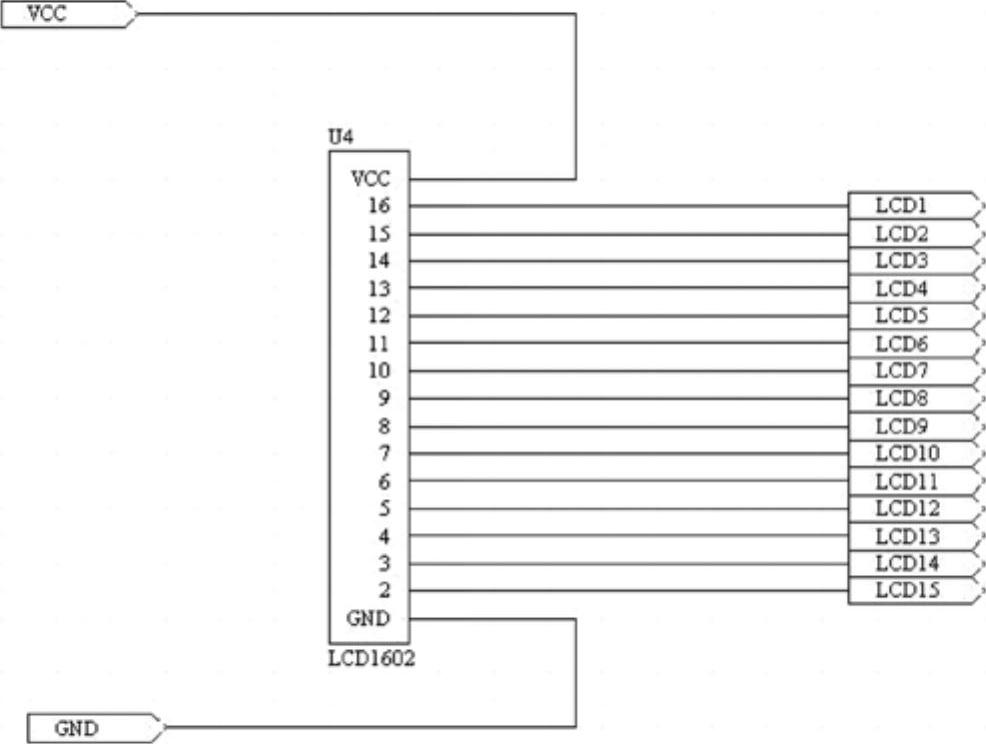

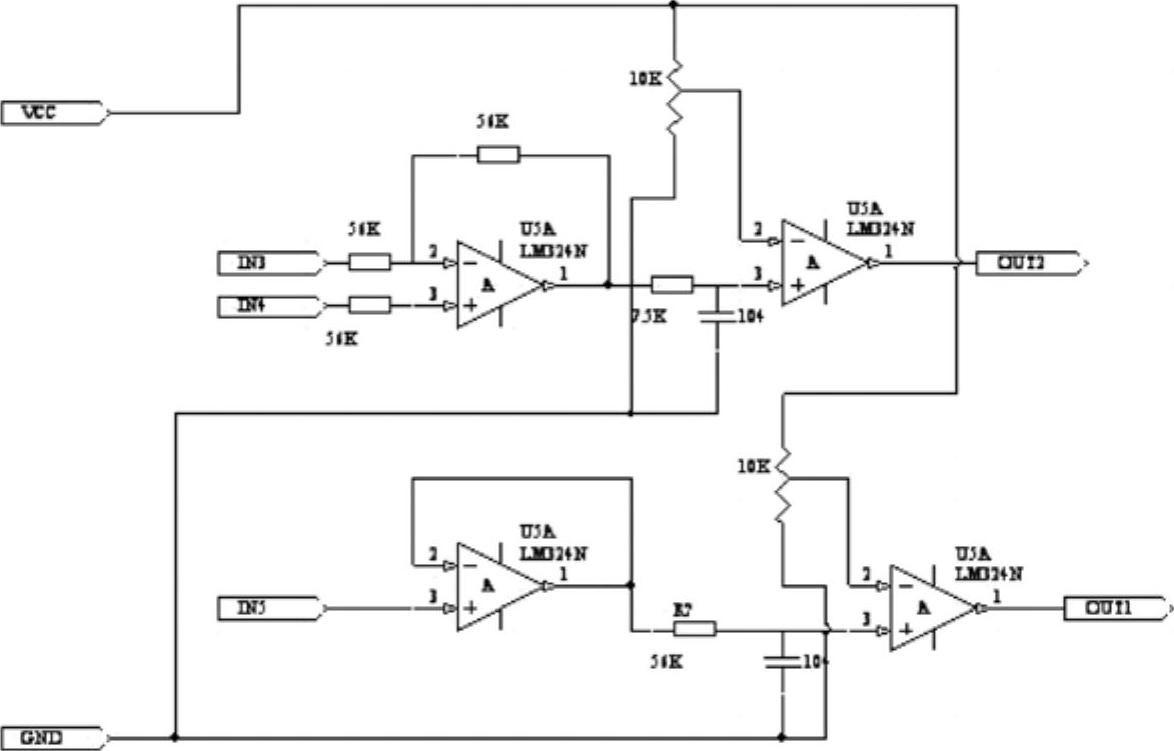

根据电路示意图3-45的连接关系,确定每个框图的接口(Port)数目。例如控制单元由单片机最小系统构成,对外输出引脚6个,输入引脚两个;译码单元由CD4051和CD4067组成,共6个输入,17个输出;显示单元由LCD1602组成,共15个输入;控制信号由4个运放LM324组成,共3个输入,两个输出。

需要注意的是,虽然原理图内部相同网络名代表存在实际的电气连接,但是框图符号不能通过同名网络连接,而必须通过接口连接,从属于同一个原理图的各层次图即使有相同的网络名(如VCC,GND),也不存在实际的电气连接。所以要使用“Place”→“Add Sheet Entry”命令,加上接口的框图符号如图3-48所示。

这里VCC和GND是每个框图都有的网络名,但是由于处于不同框内,没有实际的电气连接,所以需要导线将相关的端口连接起来,如图3-49所示。

图3-48 加上接口的框图符号

图3-49 加上连接的框图符号

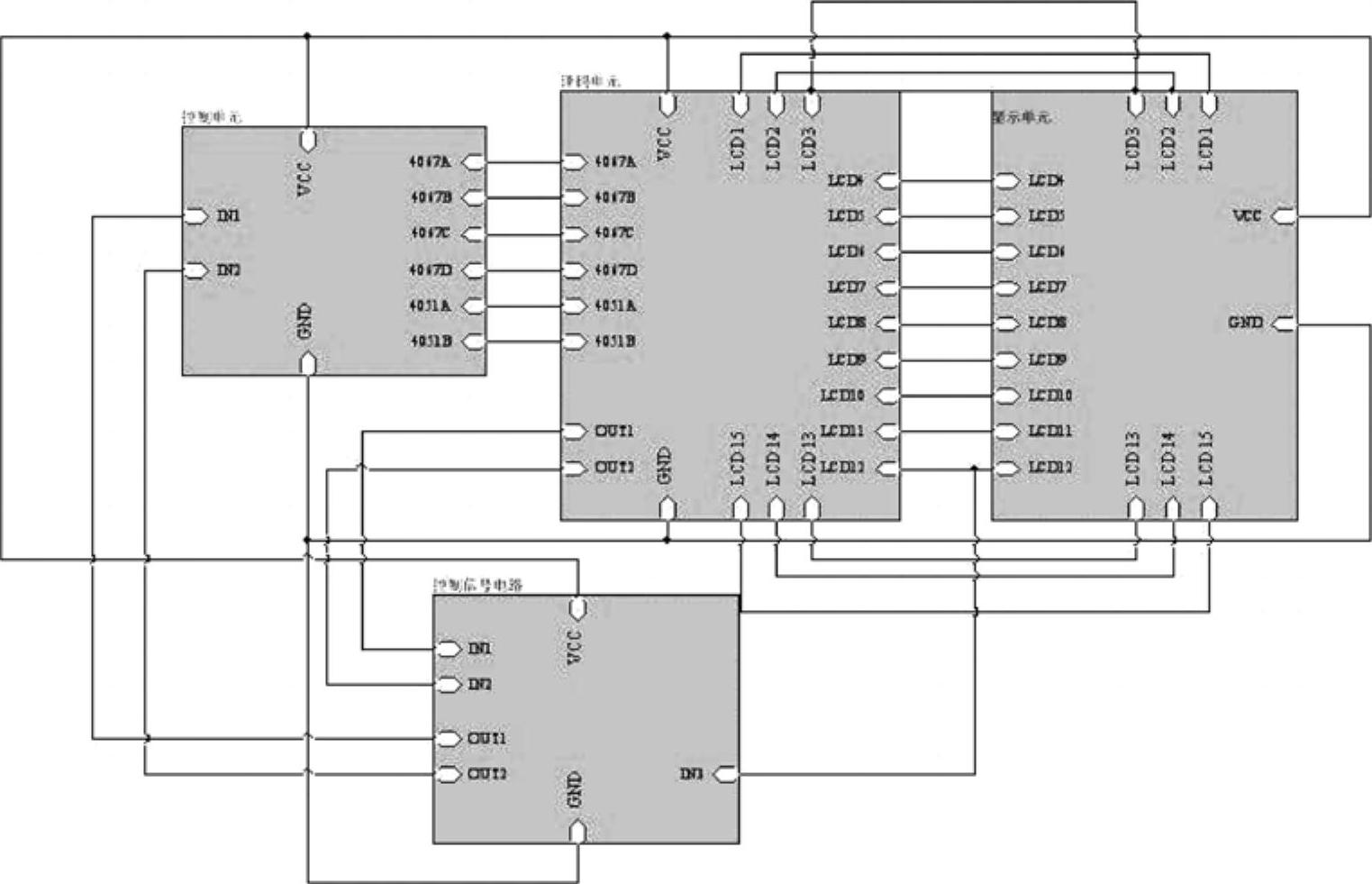

接下来,根据输入、输出关系规定各个接口的I/O属性。然后,用“Design”→“Create Sheet From Symbol”命令,进行各个框图的原理图编辑,即子图,如图3-50至图3-53所示。

图3-50 控制单元子图

图3-51 译码单元子图

图3-52 显示单元子图

图3-53 控制信号单元子图

这样就将一个复杂的原理图电路变成了一个层次图,如图3-54所示。

图3-54 层次图文件窗口

2.原理图编译错误报告

原理图的所有报错都来自于一个错误报告表,单击原理图“Project”→“Option”命令,即可调出“错误报告”对话框,如图3-55所示。

图3-55 “错误报告”对话框

这个对话框report子项下面列举了6大类、共67个不同的检查项,对应的“Report Mode”有4种报告方式:Fatal Error(致命错误)、Error(错误)、Warning(警告)、No Report(不报告),这些报告方式可以通过用鼠标单击进行切换,即可以手动调整报错的程度。

下面给出Error Reporting错误报告的中英文对照

A:Violations Associated with Buses 有关总线电气错误的各类型(共12项)

Bus Indices Out of Range 总线分支索引超出范围

Bus Range Syntax Errors 总线范围的语法错误

Illegal Bus Range Values 非法的总线范围值

Illegal Bus Definitions 定义的总线非法

Mismatched Bus Label Ordering 总线分支网络标号错误排序

Mismatched Bus/Wire Object On Wire/Bus 总线/导线错误的连接导线/总线

Mismatched Bus Widths 总线宽度错误

Mismatched Bus Section Index Ordering 总线范围值表达错误

Mismatched Electrical Types On Bus 总线上错误的电气类型

Mismatched Generics On Bus(First Index) 总线范围值的首位错误

Mismatched Generics On Bus(Second Index) 总线范围值末位错误

Mixed Generics And Numeric Bus Labeling 总线命名规则错误

B:Violations Associated Components 有关元件符号电气错误(共20项)

Component Implementations with Duplicate Pins Usage 元件引脚在原理图中重复被使用

Component Implementations with Invalid Pin Mappings 元件引脚在应用中和PCB封装中的焊盘不符

Component Implementations with Missing Pins in Sequence 元件引脚的序号出现序号丢失

Component Containing Duplicate Sub-Parts 元件中出现了重复的子部分

Component with Duplicate Implementations 元件被重复使用

Component with Duplicate Pins 元件中有重复的引脚

Duplicate Component Models 一个元件被定义多种重复模型

Duplicate Part Designators 元件中出现标示号重复的部分

Errors in Component Model Parameters 元件模型中出现错误的的参数

Extra Pin Found in Component Display Mode 多余的引脚在元件上显示

Mismatched Hidden Pin Component 元件隐藏引脚的连接不匹配

Mismatched Pin Visibility 引脚的可视性不匹配

Missing Component Model parameters 元件模型参数丢失

Missing Component Models 元件模型丢失

Missing Component Models in Model Files 元件模型不能在模型文件中找到

Missing Pin Found in Component Display Mode 不见的引脚在元件上显示

Models Found In Different Model Locations 元件模型在未知的路径中找到

Sheet Symbol With Duplicate Entries 框图中出现重复的端口

Un-designated Parts Requiring Annotation 未标记的部分需要自动标号

Unused Sub-Part in Component 元件中某个部分未使用

C:Violations Associated with Document 相关的文档电气错误(共10项)

Conflicting Constraints 约束不一致的

Duplicate Sheet Symbol Name 层次原理图中使用了重复的框电路图

Duplicate Sheet Numbers 重复的原理图图样序号

Missing Child Sheet For Sheet Symbol 框图没有对应的子电路图

Missing Configuration Target 缺少配置对象

Missing Sub-Project Sheet for Component 元件丢失子项目

Multiple Configuration Targets 无效的配置对象

Multiple Top-Level Document 无效的顶层文件

Port Not Linked To Parent Sheet Symbol 子原理图中的端口没有对应到总原理图上的端口

Sheet Enter Not Linked To Child Sheet 框电路图上的端口在对应子原理图中没有对应端口

D:Violations Associated With Nets 有关网络电气错误(共19项)

Adding Hidden Net To Sheet 原理图中出现隐藏网络

Adding Items From Hidden Net To Net 在隐藏网络中添加对象到已有网络中

Auto-Assigned Ports To Device Pins 自动分配端口到设备引脚

Duplicate Nets 原理图中出现重名的网络

Floating Net Labels 原理图中有悬空的网络选项卡

Global Power-Objects Scope Changes 全局的电源符号错误

Net Parameters With No Name 网络属性中缺少名称

Net Parameters With No Value 网络属性中缺少赋值

Nets Containing Floating Input Pins 网络包括悬空的输入引脚

Nets With Multiple Names 同一个网络被附加多个网络名

Nets With No Driving Source 网络中没有驱动

Nets With Only One Pin 网络只连接一个引脚

Nets With Possible Connection Problems 网络可能有连接上的错误

Signals With Multiple Drivers 重复的驱动信号

Sheets Containing Duplicate Ports 原理图中包含重复的端口

Signals With Load 信号无负载

Signals With Drivers 信号无驱动

Unconnected Objects In Net 网络中的元件出现未连接对象

Unconnected Wires 原理图中有没连接的导线

E:Violations Associated With Others 有关原理图的各种类型的错误(3项)

No Error 无错误

Object Not Completely Within Sheet Boundaries 原理图中的对象超出了图样边框

Off-Grid Object 原理图中的对象不在格点位置

F:Violations Associated With Parameters 有关参数错误的各种类型

Same Parameter Containing Different Types 相同的参数出现在不同的模型中

Same Parameter Containing Different Values 相同的参数出现了不同的取值

3.层次原理图编译常见错误

一般来讲,划分的子图越多,单个子图的内容就越少,但是框图太多,会引起网络重名错误的发生概率增高,例如电阻、电容,在每个子图中的编号顺序都是1,2……,而从整体图的角度来看,就发生了重命名,报告“Duplicate Net Label”错误,所以,应在每个子图中对相同类型元件进行区别编号。

层次原理图中容易出现引脚电气属性与框图接口的电气属性冲突的现象,报“Contains Power Pin And(Input/Output)Fntry”错误,这时只要将引脚属性改为“Passive”即可。原则上,只要不仿真,都可以用“Passive”属性引脚。

编译层次原理图应先编译工程文件,再编译各子图。如果直接编译子图,还未建立层次关系,则VCC端口和GND端口会报告错误:“Contain Power Pin And Input/Output Port”,含义是该连接电源的引脚仅与一个电源接口相连,这是因为这些接口(Port)没有与主图的“Entry”发生联系,所以造成假电源错误。

在绘制原理图库时应了解基本绘制工具的用法。这样能保证原理图绘制时引脚连线能连接,且为直线。图5-7 有源晶振图5-8 编辑设置1完成图5-7后会进入图5-9所示的设置界面。图5-9 编辑设置2注意在“Default Dsignator”中输入的是原理图绘制中的位号,这里的命名格式为:“位号名+‘?’”,“?”......

2023-06-23

1)按照2.8.2节中的方法把图2.8-11中后肋板的轴面投影图导入到UG中。3)绘制前肋板横截面,以正导叶前面为草图平面进行绘制,外圆直径是460mm,内圆直径是335mm,如图2.8-14所示。图2.8-13 后肋板回转图2.8-14 前肋板横截面图图2.8-15 前肋板横截面拉伸5)最后进行“求和”,对所有部件进行求和,完成径向导叶绘制。......

2023-06-26

齿轮的齿廓曲线大都是渐开线。渐开线的作图步骤如下。图1-26椭圆的近似画法图1-27圆的渐开线画基圆并将其圆周n等分。将基圆周的展开长度πD也分成相同等份。过基圆上各等分点按同一方向作基圆的切线。,πD,就可得到基圆的渐开线。......

2023-06-28

绘制剖视图必要的定位线。图9-85偏移复制后的效果参照绘制左视图过程中步骤的方法,画出表示抱箍板上的螺孔的虚线,效果如图9-86所示。执行两次镜像命令,初步得到剖视图图形。图9-86俯视图的一部分关闭“中心线”层,然后对表示架板剖面的部分进行图案填充,填充图案为ANSI31,填充比例取2。......

2023-06-21

本节范例介绍一种常见整流桥的绘制步骤,完成的整流桥如图10-18所示。图10-18 整流桥电路图图10-19 半导体二极管一般符号在“修改”面板中单击“旋转”按钮,将整个半导体二极管一般符号旋转180°,旋转结果如图10-20所示。绘制好相关直线段后,可以使用相关的修改工具来调整某些线段的位置等。图10-22 连线图10-22 连线图10-23 添加相应的文字符号图10-23 添加相应的文字符号......

2023-06-20

网络图的绘制一般可分为任务的分解与分析、绘制网络图和事项编号三个步骤。如图8-3所示,由于图中出现回路,所以该图画的不正确。如图8-4a所示的网络图,两个事项之间的箭线有3条,所以是错的。图8-4 合理使用虚工作图8-5 合理使用暗桥的网络图任何一支箭线和它相关的事项,即○→○只能代表一项工作。表8-3 工作明细表解:按照上面介绍的画图步骤,勾画出网络图,如图8-8所示。......

2023-07-15

相关推荐