图4-14 阶沃尔什基函数对于N阶沃尔什变换基,定义在N点间隔内过零次数的一半定义为列率。由表4-1可看出,按列率排列的沃尔什基序号k是过零次数,故对应列率k/2;反之,沃尔什基的沃尔什变换是仅在列率为k/2时非零的N向量。性质1:两个不同列率的沃尔什基形成完备正交系,即基相乘产生列率搬移。表4-2 N=8列率搬移性质2:信号并元移位s的沃尔什变换等于信号沃尔什变换与列率s和沃尔什基乘积。......

2025-09-29

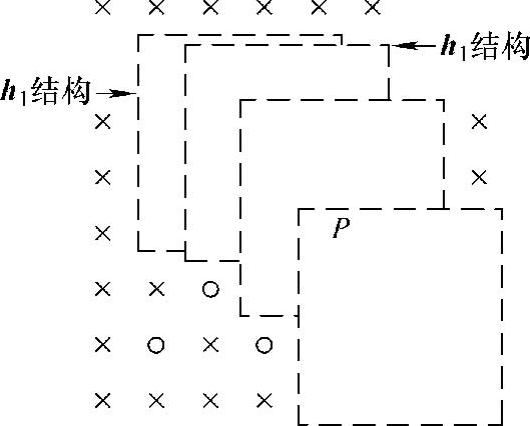

按照4×4分割的子图像窗口在行列方向上移动产生相互重叠的其他位置子图像,与其中某像素P有关的共有16个,遍及在原始图像中7×7像素的范围内。

如图8-3所示,图中没有把与像素P相关的16个子图全部画出,只列出了4个子图像。对与像素P相关即包含其在内的16个子图像经过二维低通滤波器处理后的输出值平均值(这种平均可以是加权平均)即为重叠滤波器的输出。显然,采用这种重叠滤波器内插就可以消除高列率谱的混叠。如图8-3所示,对于1/2取样图像,相邻的子图像反复出现h1和h2结构,这两种结构的高列率分量幅度近似相等而相位相反,所以在重叠相加时基本上对消,从而有效地克服了按子图分块滤波恢复拼接时的边缘效应。

图8-3 4×4子图像重叠滤波的构成

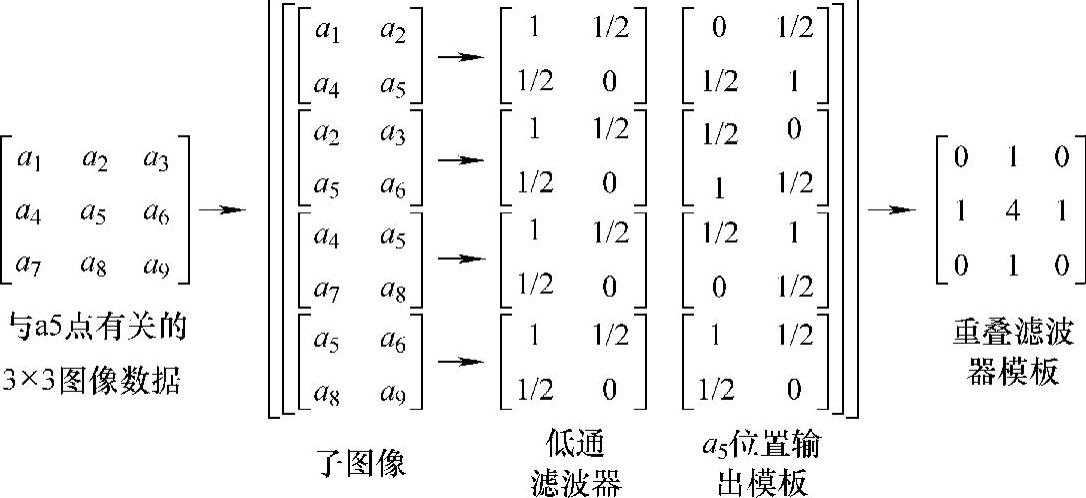

下面讨论最简单的子图像为2×2的二维低通重叠滤波器。如图8-4所示,与像素a5相关的图像共有4个子块Xi,其包含的像素分别为[ai,ai+1;ai+3,ai+4](i=1,2,4,5)。

图8-4 对应2阶低通列率滤波器的3阶重叠模板构造

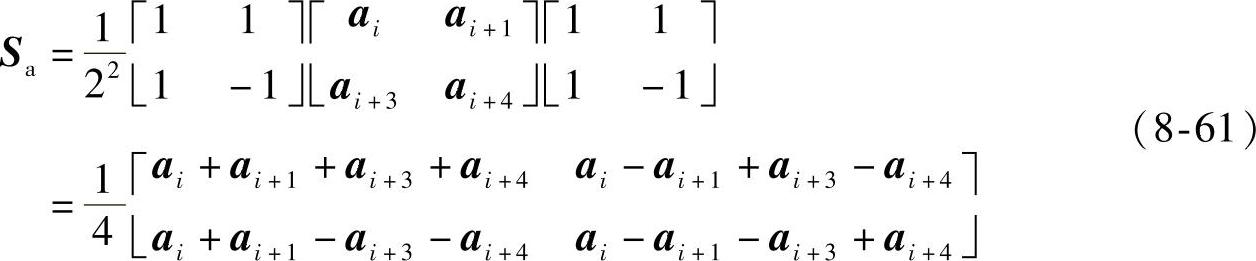

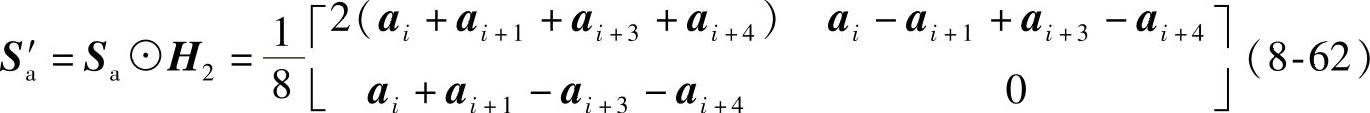

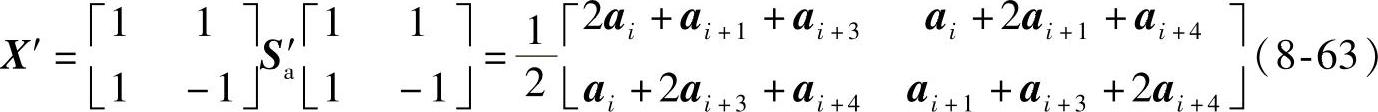

某个2×2的子图像a经过二维沃尔什变换后为

经过滤波器H2后变为

再经过二维沃尔什反变换得到内插恢复的子图像a′如下:

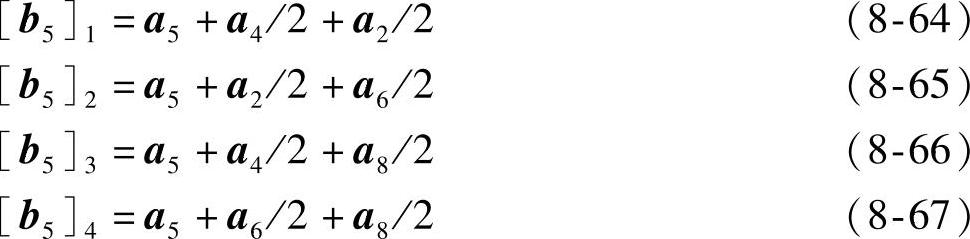

当i=1~4,对应点a5的输出分别如下:

上面4个表达式(8-64)~式(8-67)的输出和的平均就是重叠滤波器输出b5,即

式(8-68)可用一个模板来表示为(https://www.chuimin.cn)

模板与图像做尺寸为3×3的卷积即得重叠滤波的全部输出,其结果与全部2×2子图像逐行逐点移动作低通滤波器后的叠加输出平均相同。这种基于模板的内插方法计算简单,对于1/2抽取后保留的像素内插后处理不变,对于内插产生的新像素值等于周围4个像素的平均值。

以上分析的子图像尺寸是2×2,当图像尺寸为N×N时,与某样点相关的子图像有N2个,它们分别滤波后并进行叠加的平均输出,可以表示成一个尺寸大小为(2N-1)×(2N-1)的模板,这个模板与图像的逐点卷积即得重叠滤波的全部输出。显然,这就是我们在第5章中设计的二维全相位滤波器或称全相位内插模板。

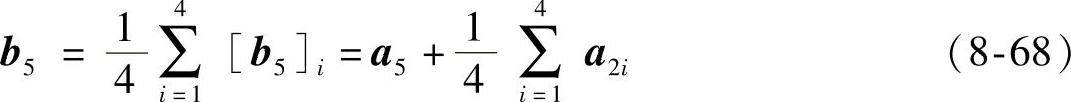

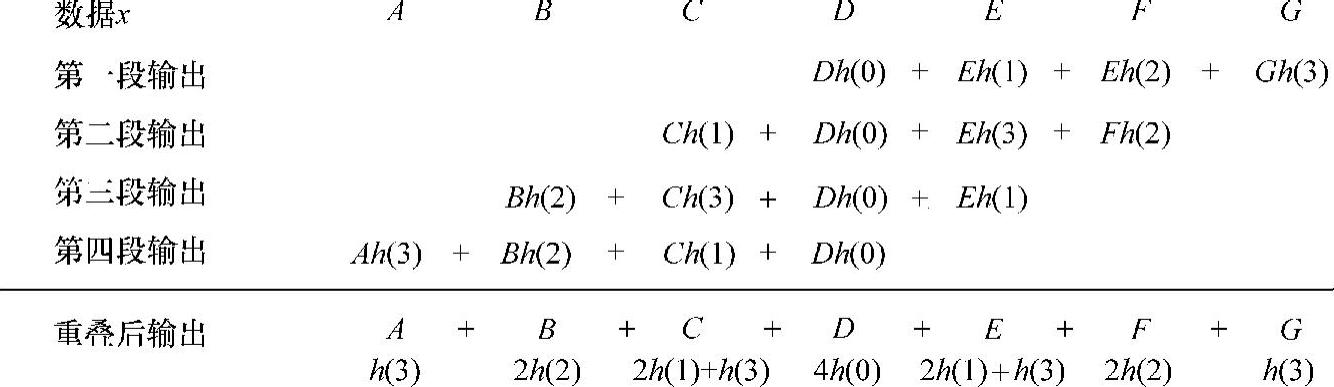

全相位沃尔什内插模板的设计就是给定低通滤波器H求出模板T的过程。以一维N阶沃尔什变换域列率滤波器为例,若输入数据为x(n),列率滤波器的变换域特性为H(k),滤波后输出应为x与h的并元卷积。每一子段经过H滤波的输出重叠过程如图8-5所示。

图8-54 阶并元移位及重叠

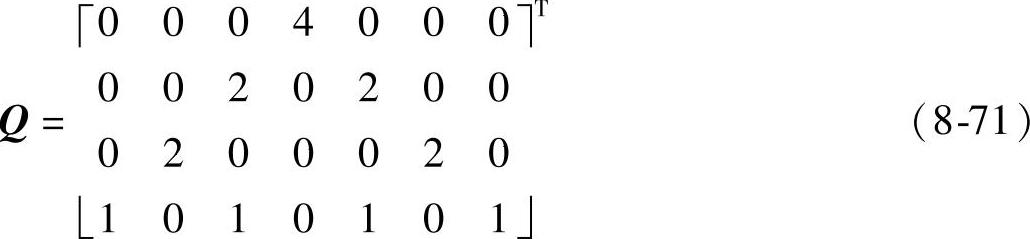

由图8-5重叠输出结果可以看出,一维全相位内插模板可以表示成矩阵Q与h相乘的形式:

式(8-70)中,W是沃尔什基矩阵;Q是并元移位叠加矩阵,定义如下:

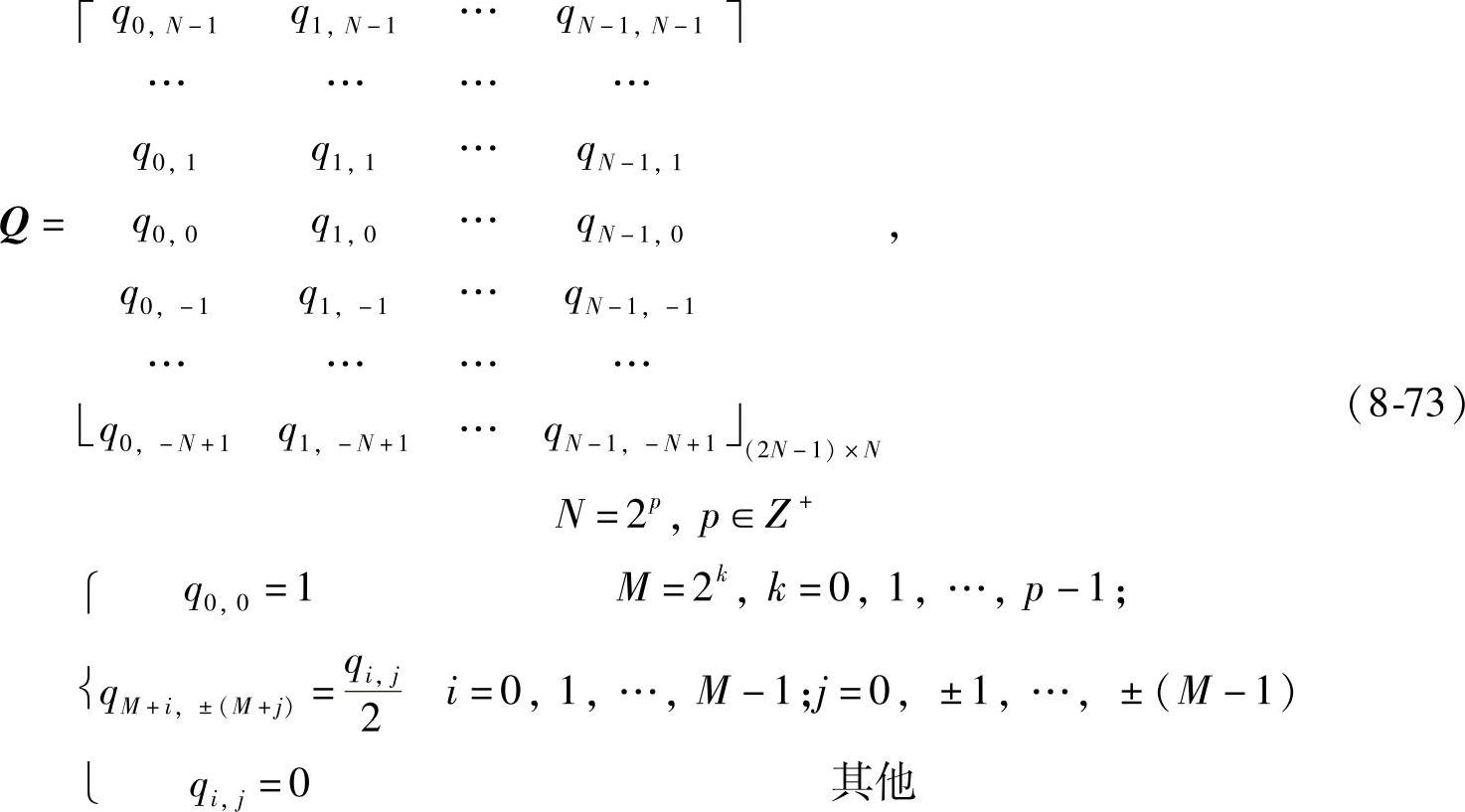

总结以上,对于N阶二维沃尔什全相位滤波,从传输矩阵H求出模板T的过程如下:

式中,W是N阶沃尔什基矩阵;Q是N×(2N-1)并元移位叠加矩阵,定义如下:

根据式(8-72),如果已知模板T,可通过下式求其对应的传输矩阵H:

H=W·Q·T·(Q)T·W (8-74)

式中,Q是并元移位叠加矩阵Q的伪逆。

相关文章

图4-14 阶沃尔什基函数对于N阶沃尔什变换基,定义在N点间隔内过零次数的一半定义为列率。由表4-1可看出,按列率排列的沃尔什基序号k是过零次数,故对应列率k/2;反之,沃尔什基的沃尔什变换是仅在列率为k/2时非零的N向量。性质1:两个不同列率的沃尔什基形成完备正交系,即基相乘产生列率搬移。表4-2 N=8列率搬移性质2:信号并元移位s的沃尔什变换等于信号沃尔什变换与列率s和沃尔什基乘积。......

2025-09-29

沃尔什基矩阵与一维变换时相同,由沃尔什函数产生。由沃尔什矩阵可以构成二维沃尔什函数的基本图像。表5-24 阶沃尔什基本图像矩阵与傅里叶基本图像不同的是,沃尔什变换等其他正交变换基图像均是实矩阵。二维哈达玛变换基矩阵与沃尔什基矩阵只是行向量排列顺序不同,正反变换形式相同。......

2025-09-29

由第5章内容可知,二维DCT运算可以转化成DFT运算,然后取结果的实部作为DCT变换的结果。DCT基可以设计任何大小的内插模板,而不限于2的整数次幂。以上面傅里叶基构造的结果直接得到DCT基滤波器H和对应的非重叠模板。图8-1c对应的定制H1/3如下,其反变换即为非重叠模板T1/3。......

2025-09-29

正交基为傅里叶算子时,模板设计过程与上面沃尔什算子基本相同,不同之处在于卷积类型变为循环卷积。傅里叶基设计的特点是可以构造任何大小的内插模板,而不限于2的整数次幂。......

2025-09-29

图8-1腐蚀原电池示意图电极反应如下:总反应为腐蚀电池的电极阳极发生的是氧化反应,即被腐蚀的电极,阴极发生的是还原反应。②标准电极电位标准电极电位是指参加电极反应的物质都处于平衡状态时得到的电势。表示电极电位与极化电流密度或极化电流强度之间关系的曲线称为极化曲线。......

2025-09-29

功率MEMS是能够发电或进行电能转换的微机电系统。涡轮机的转子直径为8mm,每分钟旋转三百多万转,能够产生几十瓦的机械功率,而释放的尾气温度超过1500℃。如果与一个牙钻相连,这个发电机在400000r/min时可以产生5W的功率,在1000000r/min时则能产生20W的功率。......

2025-09-29

假设输入图像大小为N×N,则在某正交变换对α和β下1/K内插模板设计过程如下:1)写出1/K单位抽取算子d,d中只有N2/K个元素为1而其余为0。离散沃尔什变换简单、直观,其正交基只有两种状态,用它来表示图像的物理性质较为清楚,因此用沃尔什变换设计的各种图像处理模板系数都是有理数,且规则性强、易于归纳总结。用离散傅里叶变换设计的模板系数是无理数,但它却有明确的物理意义。......

2025-09-29

将φ 乘以Boltzmann方程的两边,对整个颗粒脉动速度空间积分,获得φ 的输运方程。因此,可以通过假设颗粒的速度分布函数获得颗粒流的应力和能量通量等的表达式,或者用统计平均的办法建立各类守恒型方程来描述颗粒流的平均运动。因此,需要通过一定假设,建立泥沙颗粒相的本构关系。......

2025-09-29

相关推荐