二维全相位在各种正交变换的基础上进行了全相位信号处理,一方面扩展了输入信号信息,另一方面对于不同相位信号进行不同权值的加权,从而使二维全相位信号处理在保留传统分块固有性质的同时也具备了一些特殊性质。可把基窗分解成若干个子基窗,从而得到信号不同加权情况下的全相位处理输出,其特性取决于子基窗的形状。以式中低通特性HLL为例,为保持全相位处理的严格零相位特性,仍使子基窗满足中心对称。......

2023-06-23

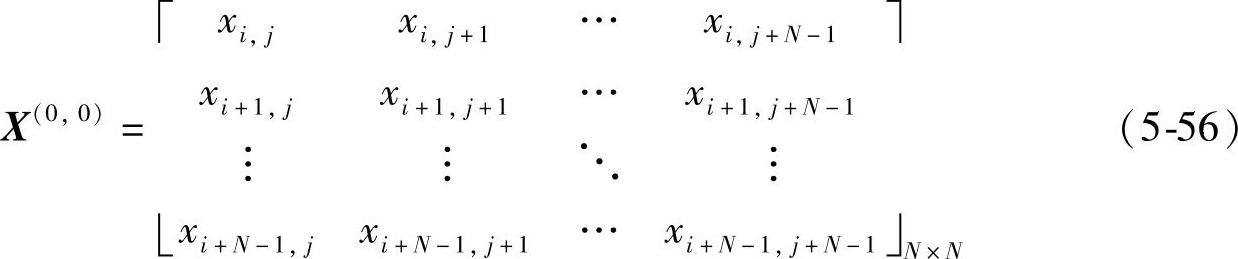

参考图4-12,假设变换域系统H是N×N维的,对于任意元素xij在原点位置时对应的输入矩阵X(0,0)定义如下:

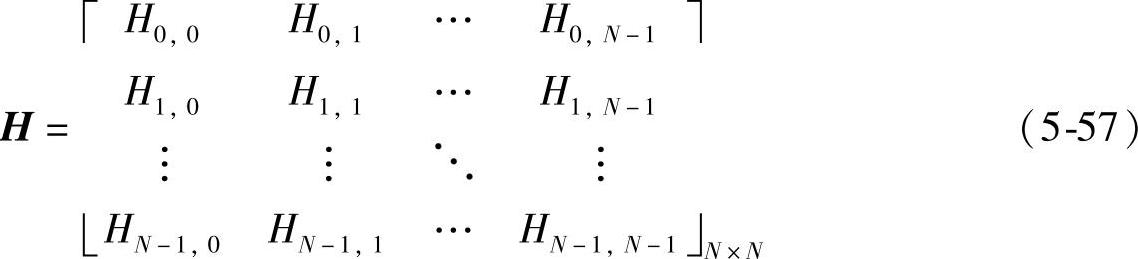

传输特性序列H定义如下:

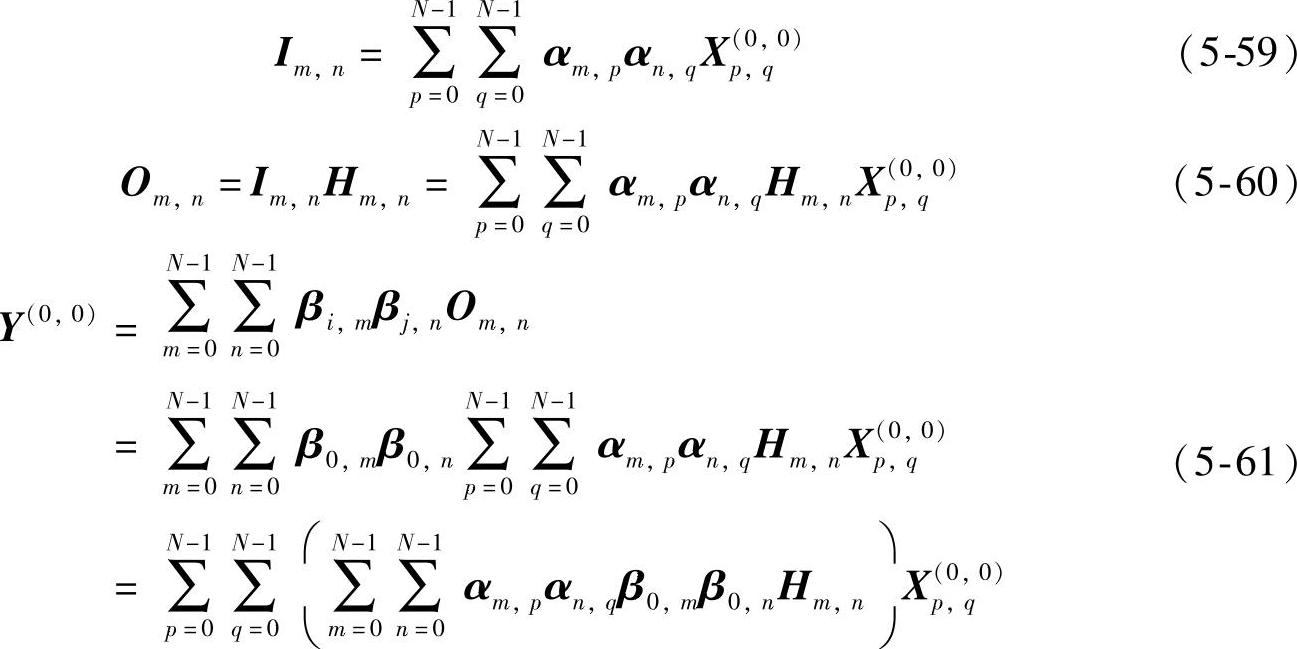

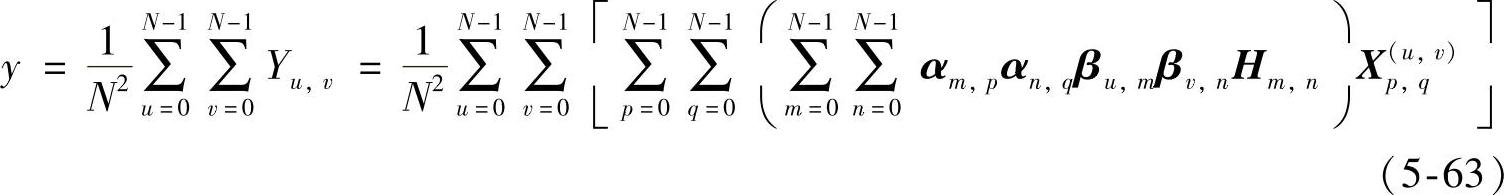

由上面5.1节介绍的正交变换可得输出Y为:

Y=β[(α X(0,0)αT) H]βT(5-58)

H]βT(5-58)

结合图4-12,有

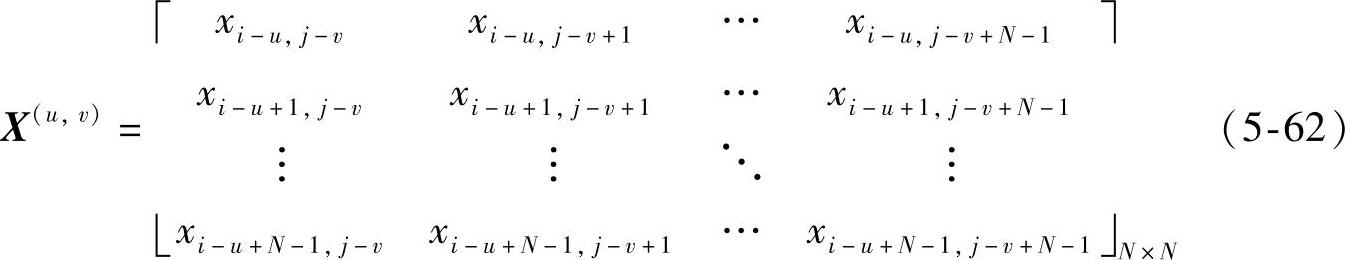

对于输入X(0,0),对应xi,j的输出是(u=0,v=0)位置的Y0,0(0,0)。二维全相位数字处理的输入是xi,j遍历N×N个位置的N2个矩阵,输出则是对应X(u,v)在位置(u,v)处N2个输出Yu,v(u,v)的和的平均。由式(5-56)可知遍历矩阵X(u,v)为

结合式(5-61)和式(5-62),可知二维全相位信号处理输出为

观测式(5-62)易知:

令

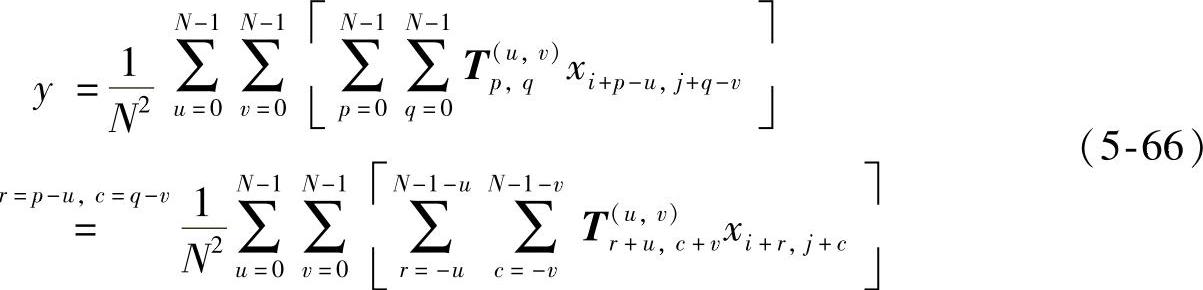

把式(5-64)和式(5-65)代入到式(5-63)得:

分别交换r与x和c与y的求和顺序后得:

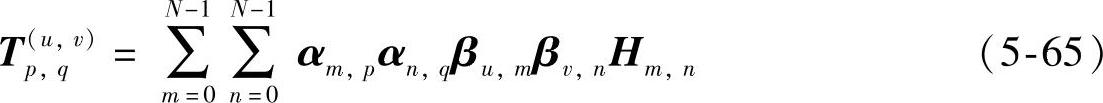

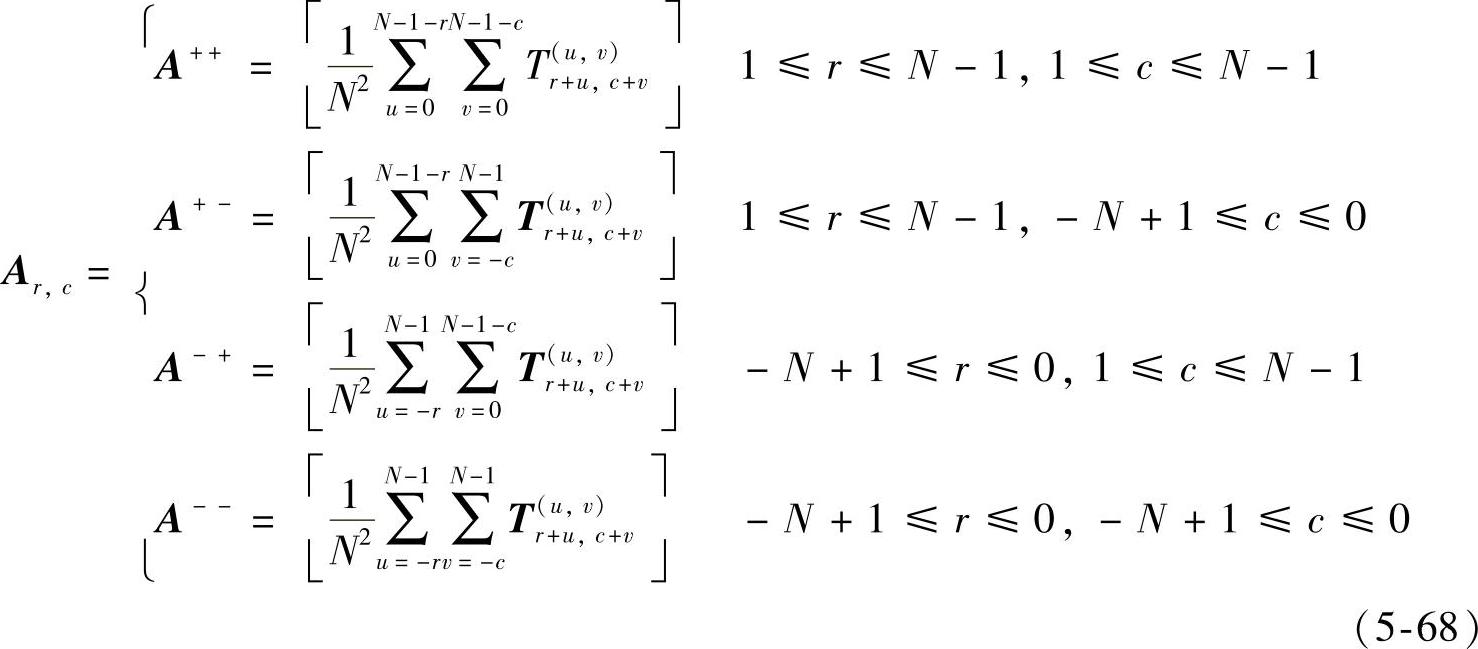

观察式(5-65),矩阵T是由正交变换正反核与特性矩阵共同定义,它是数据xi,j移动到(u,v)时对应输入X的加权,称T为二维全相位变换核。观察式(5-67),对于不同区间的(r,c),定义变量如下:

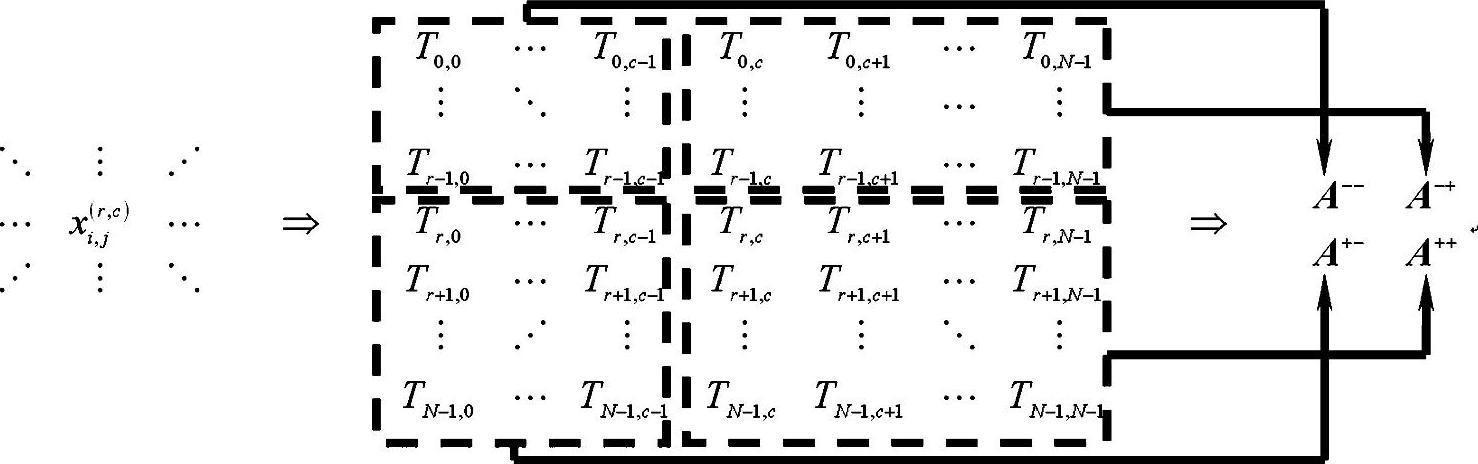

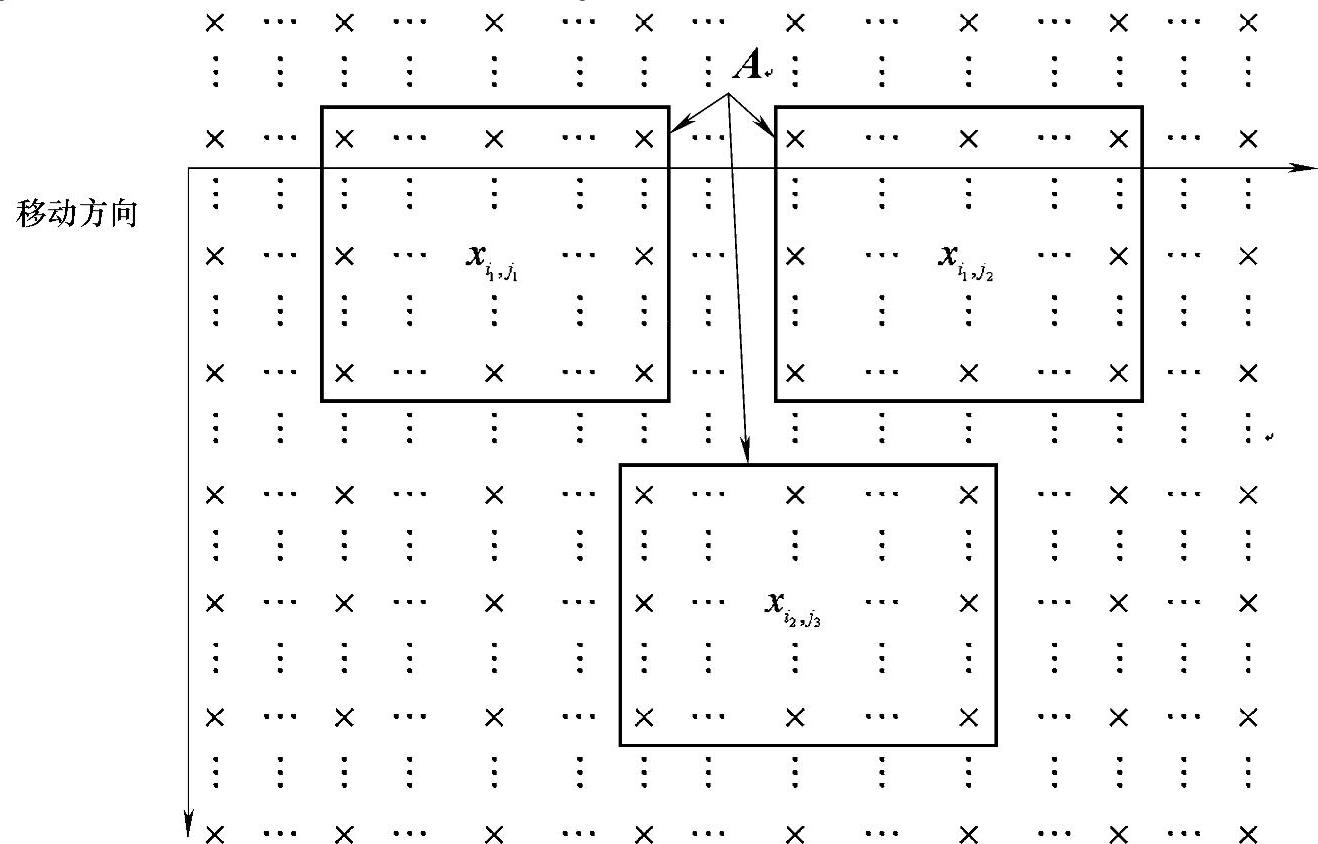

由式(5-68)可以看出,矩阵A是通过对不同区间的全相位变换核求和得到,它包含四个子矩阵即A++、A+-、A-+和A--,其物理意义是数据xi,j由(0,0)位置逐点移动到(N-1,N-1)过程中,以数据xi,j划分的T的4个区间内各自数据之和即得到A的4个子矩阵,形成过程如图5-7所示。

图5-7 矩阵A形成过程

由图5-7可以看出,四个子矩阵A++、A+-、A-+和A--的维数分别是N×N、N×(N-1)、(N-1)×N和(N-1)×(N-1),所以矩阵A的维数是(2N-1)×(2N-1)。把式(5-68)代入到式(5-67)得:

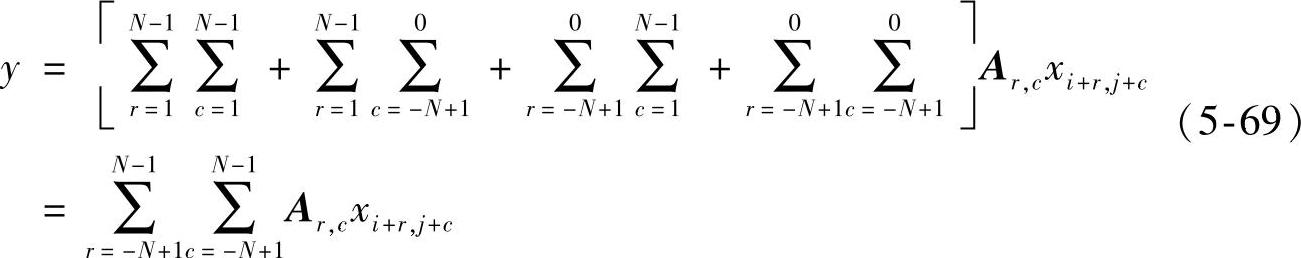

式(5-69)表明,二维全相位信号处理对应xi,j的输出等于在行列方向上以xi,j为中心的共(2N-1)2个数据以A为加权的总和。式(5-69)称为二维全相位变换,A是全相位变换基矩阵。

参考图5-1的信号移动规律,二维全相位信号处理可以按照行或者列优先的方式来实现,下面以行优先为例给出实现原理图。行方向上块处理方式如图5-8所示。

图5-8 二维全相位行信号处理框图

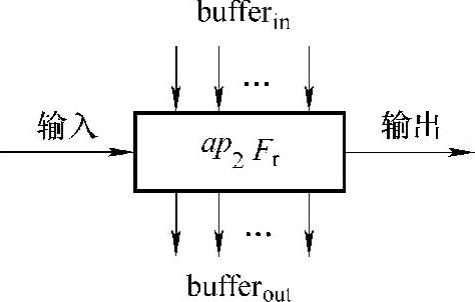

图5-8中,输入是按照行方向移动的大小为N×N的数据块,假设待处理图像大小为M×L,且进行边界扩展成(M+2N-1)×(L+2N-1)以保证输出图像大小不变。Zc是行方向移动的单位延迟。图5-8工作方式是,按照间隔Zc顺序输入的N个起始方块经过正交变换、H加权和反变换后依次进入延迟分别为iZc(i=N-1,N-2,…,0)的缓存器中,X(0,N-1)处理后的N个数据块同时进入加法器上方的单位延迟缓存器,同时断开各路开关。后续的X(0,N)即对应xi,j+1的输入处理结果将直接进入最左边直通通路而顺序产生M个对应输出y(0,v),并把M+N-1个处理结果存入buffer中。封装图5-8成子系统如图5-9所示。

图中bufferout是本模块处理的所有中间结果,buff-erin是下一行模块处理的所有中间结果作为当前模块处理时初始状态值,存入加法器上方的N个单位延迟缓存器中。这样,与xi,j相关的N行并行处理系统可设计成如图5-10所示的结构。

图5-9 二维全相位行信号处理封装模块

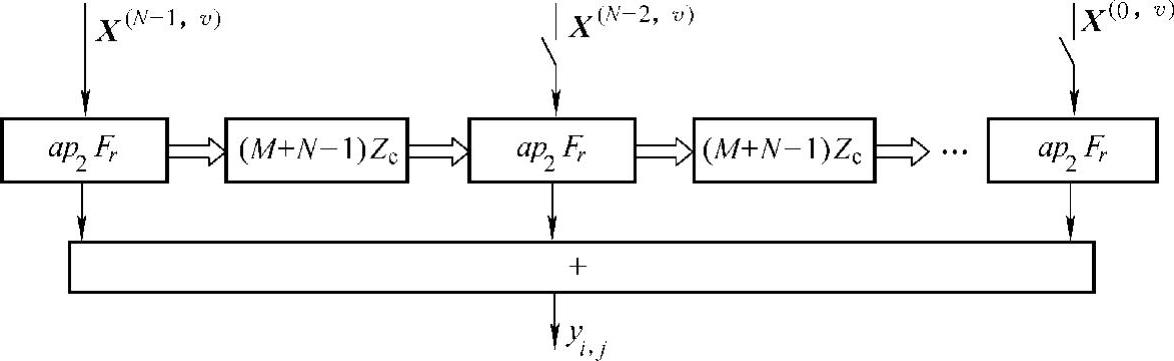

图5-10 二维全相位信号处理系统图

图5-10工作流程是,初始N个数据块输入后,断开所有开关。N列并行处理,经过(M+N-1)Zc时间后,所有行均完成处理并输出N个结果,这样对应xi,j的N2个数据和即为输出yi,j。以上是按照式(5-63)的实现过程,与其等价的式(5-69)实现方式只需用全相位变换基按照行或列优先逐点移动处理来完成。一种直接方式如图5-11所示。

图5-11 全相位基滑动处理图

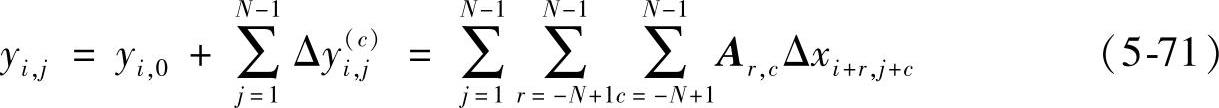

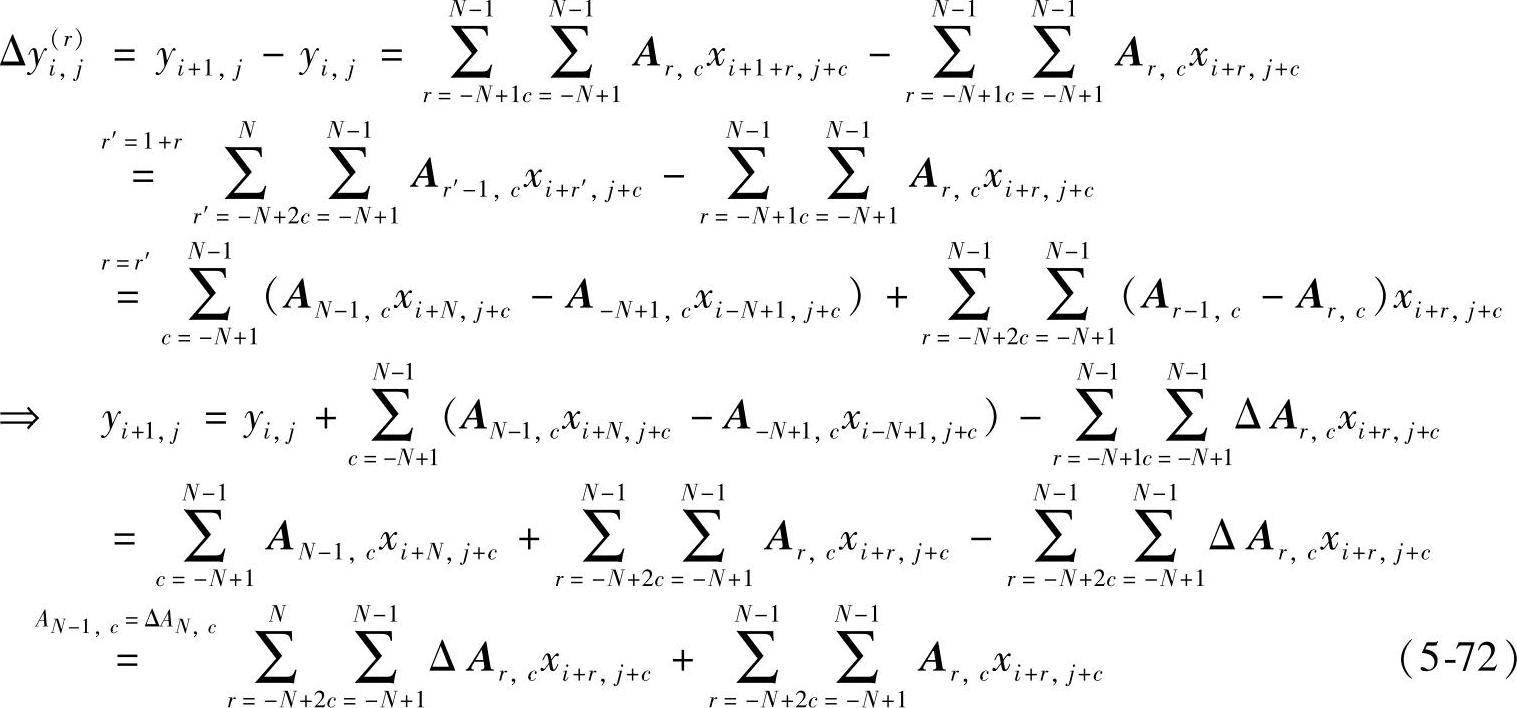

由图5-11所示的处理过程可以看出,通过滑动全相位基矩阵A来对准某像素xi,j后按照式(5-69)即得到对应输出yi,j。考虑到图像信号的空间相关性以及为充分利用相邻行或列的重复部分,可做进一步优化处理。对于同行的相邻点xi,j和xi,j+1,由式(5-69)可知对应输出yi,j和yi,j+1具有如下关系:

即相邻像素的全相位处理输出差分正比于对应输入块X的差分。由此可推导出同一行的任意点输出为

对于同列相邻点xi,j和xi+1,j,由式(5-69)可知对应输出yi,j和yi+1,j具有如下关系:

式(5-72)表明,隔行的输出由两部分组成,第一部分是新增行与全相位基行差分与X(i+1,j)的加权和,第二部分是上一行元素全相位处理中全相位基与X(i,j)的加权和中除去第一行之和。其中第二部分已经在上一行处理中计算出来,因此可重复利用。利用全相位基的对称性可进一步优化计算过程,下面针对DFT、DWT和DCT三个变换域分别展开讨论。

有关全相位数字信号处理方法及MATLAB实现的文章

二维全相位在各种正交变换的基础上进行了全相位信号处理,一方面扩展了输入信号信息,另一方面对于不同相位信号进行不同权值的加权,从而使二维全相位信号处理在保留传统分块固有性质的同时也具备了一些特殊性质。可把基窗分解成若干个子基窗,从而得到信号不同加权情况下的全相位处理输出,其特性取决于子基窗的形状。以式中低通特性HLL为例,为保持全相位处理的严格零相位特性,仍使子基窗满足中心对称。......

2023-06-23

对于ap2 DCT的全相位变换核,有式中符号表示异或运算。基于此结论的ap2 DCT和ap2 DWT的全相位变换基也具有对称性。以图5-20给出的3种卷基窗分别形成的二维apDCT传输特性如图5-21所示。图5-21 ap2nsd DCT特性曲面及曲线图从图中可看出apDCT的平滑性好于apDFT,ap2d DCT的衰减特性比ap2n DCT低20dB,但由于采用与ap2n DCT和ap2s DCT相同的归一化条件,峰值幅度低于1且过渡带宽度增大。......

2023-06-23

图4-12 变换域信号处理图对于N阶系统,时刻n输入xn=[x,x(n-1),…其中X1是1维N阶全相位输入信号,即式就是全相位数字信号处理得到的输出与输入的数学关系表达。把式称为全相位变换,矩阵A称为全相位变换基,矩阵T则为全相位变换核。综合以上,变换域全相位数字信号处理一种可能实现如图4-16所示。......

2023-06-23

针对不同类型的信号,信号处理涉及的内容主要包含滤波、变换、检测、谱分析、估计、压缩、识别等方面。滤波的主要任务是设计特性数字滤波器以得到不同频率成分的信号分量,如高通滤波可得到信号的高频成分,中值滤波则可降低高频分量起到平滑的效果。检测和估计主要是从受噪声干扰的杂波中利用信号的统计特性得到有用信号的过程。压缩是信号处理的一个重要方面,它主要是消除信号自身的相关性从而达到减少数据量的效果。......

2023-06-23

用参数模型法进行谱估计首先要选择一种适合被测信号的参数模型,其次用适当的方法估计出模型的参数,最后利用所得到的模型参数计算出信号的谱。因此能否正确选择信号的模型,确定模型的阶数,以及估计模型的参数是决定参数模型法谱估计质量的关键。实际中的许多随机离散时间信号x,都可以表示为有理参数模型。有理系数模型中最常用的是AR模型。,q,则称这种模型为AR模型。......

2023-06-23

长度为N的单边带H0按上面3种方法设计生成的ap半带滤波器H的长度为2N-1。在满足条件1、2、3下,ap1 nsd半带滤波器H、单边带H0和卷积窗C的零点分布如图7-22所示。ap1ns半带滤波器的H零点由单位圆上和内及对应的倒数组成,而ap1 d半带滤波器的H零点只由单位圆内及对应的倒数组成。即把半带滤波器H进行分解后找到所有圆内的零点就可以确定分析低通滤波器h0,再按照PR条件即式关系依次求出分析高通滤波器h1,综合滤波器f1和f2。......

2023-06-23

20世纪70年代初,滤波器组首先在语音编码和多路复用中得到了应用。所谓滤波器组就是将信号按不同的频带分解成一组信号,并将分解得到的子带信号重新合成原信号的处理系统。80年代后期,M.J.Smith等人提出了运用谱分解法设计无失真地重建原始信号的滤波器方法,但存在相位失真。......

2023-06-23

由于不同的分段起点,可能存在N个不同的数据段都包含待插值的样点I,即将产生N个不同的插值结果,全相位插值就是取这N个插值的均值作为最终结果。正反变换定义如下:式中Walsh变换基只有±1离散值,傅里叶变换基有复数,因此选择DCT基作为插值的正交变换。图8-23 八点全相位DCT内插核时频图(N=5)对与上面实验中相同的Chirp信号进行插值重建,实验结果如图8-24所示。......

2023-06-23

相关推荐