将n=1.8,Q=0.8 eV/原子的值代入该公式所得出的结果,被证实远远高估了倒装芯片焊点在高电流密度的平均失效时间。表9.2所示为倒装芯片焊点在三种不同的电流密度与温度下平均失效时间的计算值和测量值。这些发现表明倒装芯片焊点的平均失效时间对电流密度的微小增量都十分敏感。例如,在电流密度为2.25×104 A/cm2,温度为125℃时,无铅焊料的平均失效时间为580 h,而锡铅焊料却只有43 h。......

2023-06-20

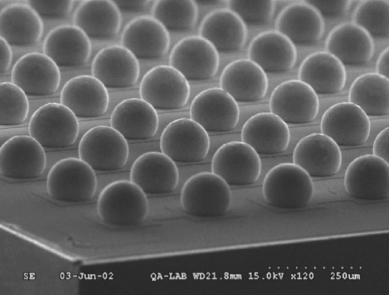

在像服务器这样的大型计算机上,连接硅芯片与基板之间的焊料接头是非常复杂的。我们先来看看芯片上互连的两个简单例子来了解它的复杂性。目前超大规模集成芯片电路(Very-large-scale Integration,VLSI)上的铝或者铜互连线的宽度为0.5μm(或更小)。假设两条平行的互连线间的间距也为0.5μm,那么两条互连中心线间的距离就是1μm。因此,在1 cm2的芯片上可以布置104条每根长度为1 cm的线。这意味着在单层布线时,线的总长度可达到100 m。由于一块芯片上有6~7层布线,再加上层间的通孔长度,在1 cm2芯片上的互连线长度可达1 km。我们需要这么多的互连线来连接芯片上的数百万个晶体管,以便它们可以共同发挥作用,这是芯片与基板互连复杂的第一个原因。同时,为了给芯片上的所有这些互连线提供外部通电引脚,一个逻辑芯片的表面可能需要几千个输入/输出(Input/Output,I/O)焊盘。目前,提供如此高密度I/O焊盘的唯一方法是使用面阵列焊料小球。将直径为50μm的焊料小球以50μm的间距进行放置,则两球之间的中心距为100μm,那么在1 cm长度方向上可放置100个焊料小球,或在1 cm2的面积可以放置10 000个焊料小球。因此,在芯片和基板之间互连复杂的第二个原因是在芯片表面需要10 000个I/O端子或者焊料小球。由于预期使用尺寸很小、数量巨大的焊料小球,国际半导体技术蓝图(International Technology Roadmap for Semiconductors,ITRS)自1999年以来就将“倒装芯片技术中的焊料接头”在制造过程中的良品率和使用可靠性作为一个重要的研究课题。实际上,现在正在开发直径为25μm的焊料小球。

什么是芯片的倒装?它是一种在硅芯片与陶瓷基板或印制电路板之间实现连接的方法。硅芯片表面朝下以使超大规模集成电路面向基板,通过芯片和基板之间布置的面阵列焊料小球来实现电连接。不同于引线键合由芯片周边引出互连线,倒装芯片互连是面阵列焊料凸点,覆盖整个或大部分芯片表面。

图1.4为将硅芯片和引线框架互连的引线键合示意。框架上的引脚通过表面贴装技术或者针通孔插装技术焊接到电路板上。芯片上载有超大规模集成电路的一面在引线键合过程中朝上,这是因为引线键合需要超声波振动,键合过程中所施加的应力可能会损坏键合区域周边及内部的结构,所以必须在芯片的边缘进行,以便能远离芯片中间部分的功能性超大规模集成电路区域。这样,即使我们采用20μm的引线以及20μm的引线间距进行布线,那么在1 cm2大小的芯片边缘也只能引出大约1 000个I/O端子,这个数量远小于在同样大小芯片表面采用沉积或电镀工艺布置的焊料小球数量(10 000个)。由于引线键合焊盘占据了芯片的边缘,因此也浪费了大量的芯片表面。

若将焊料小球直接放置在功能性超大规模集成电路区域并布置于整个硅芯片的表面,是不会产生应力问题的。芯片表面的焊料小球面阵列如图1.7所示。为了将芯片连接到基板上,芯片会被倒置,这样芯片上载有超大规模集成电路的一面会面向基板。

通常,倒装芯片技术的优点是封装尺寸小,I/O引脚数量大,性能好。在封装尺寸几乎与芯片尺寸相同的小尺寸封装中,已经实现无边缘键合区域的小的封装尺寸。较多的I/O引脚数是靠面阵列互连焊点实现的;由于位于中心区域的凸点允许器件在较低电压和较高速度下工作,因而可获得更好的性能。对于需要具备这些性能特点的器件而言,例如手持式电子器件,倒装芯片是目前唯一可提供所需可靠性的技术。

图1.7 芯片表面的焊料小球面阵列

国际半导体国际技术蓝图[12]预计,在可预见的未来(约2015年),硅芯片技术仍能够每两到三年推进新一代产品。为了跟上硅芯片技术的发展,芯片封装技术也要不断进步。因此,封装基板上布置的电路密度以及I/O引脚的数量必须增加。对于未来的使用的技术和产品必须要讨论其可靠性问题。

倒装芯片互连技术已经在大型计算机中使用了30多年。它起源于19世纪60年代开始在陶瓷基板上封装芯片所使用的“可控塌陷芯片互连”技术(简称“C-4”技术)[13-14]。关于可控塌陷芯片互连技术的详细讨论及其发展历史,读者可以参考Puttlitz和Totta所写的文献综述[1]。

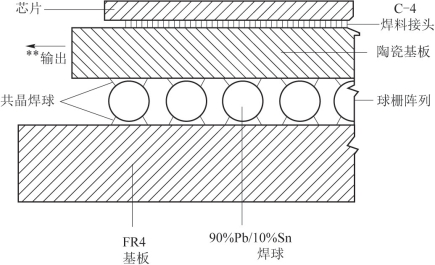

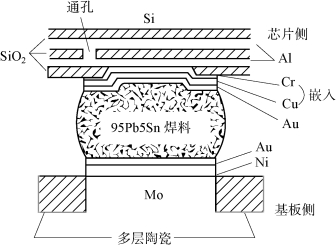

开发超大规模集成电路芯片技术时需要考虑封装中的高密度布线和互连。这促进了用于大型计算机中的多层金属陶瓷组件和多芯片组件的发展。在多层金属-陶瓷基板中,多层的金属钼线被埋在陶瓷基板中。每一个基板可以搭载多达100个芯片。多个陶瓷组件被连接到大的印制电路板上时,即可形成如图1.8所示的用于大型计算机中的两层互连的封装结构。它包括第一层的芯片与陶瓷基板的封装组件和第二层的陶瓷组件与印刷线路板的封装体。在第一层封装中,芯片上焊料UBM层由Cr/Cu/Au的三层金属薄膜组成。实际上在这三层中,Cr/Cu是一种嵌入相的微结构(作为黏附层,Cr嵌入Cu膜的结构),以改善Cr和Cu之间的结合力,增强其对焊料反应的抵抗能力,使其可经受多次回流。陶瓷表面的键合焊盘材料是Ni/Au,十分典型。连接UBM层和焊盘的焊料是高铅合金,如95Pb5Sn或97Pb3Sn。倒装芯片焊料接头的横截面示意如图1.9所示。芯片上的焊料凸点采用蒸发技术进行沉积并通过刻蚀技术进行图案化获得,目前采用选择性电镀沉积法进行制备。高铅焊料凸点的熔点高于300℃。第一次回流(约350℃)过程中,在UBM层上会获得球形凸点。由于SiO2的表面不能被熔融焊料润湿,熔化的焊料凸点的底部形状由UBM层的接触开口形状确定,因此熔化的焊料凸点在UBM层上形成小球状凸点。所以,当给定焊球体积时,UBM层便控制了焊球的尺寸(高度和直径)。通常,UBM被称为“限制焊料小球的金属化”(Ball-limiting Metallization,BLM)。BLM控制着固定体积焊球熔化时的高度,这是所谓“可控塌陷芯片互连”中“可控”的含义。如果没有这一控制,焊球将润湿铺展,那么芯片和基板之间的间隙就会变得特别小。

图1.8 大型计算机中芯片、陶瓷基板及印刷线路板之间两层互连的封装结构的横截面示意

为了将芯片连接到一块陶瓷基板上,需要进行第二次回流。在第二次回流期间,熔融的焊料凸点的表面能提供自动对准力,使芯片自动定位在基板上。当焊料熔化从而将芯片连接到基板上时,芯片将略微下降并稍微旋转。下降和旋转是由于熔融的焊料小球表面张力的减少,这实现了芯片与基板之间的对准,因此被称为可控塌陷工艺。

我们注意到,虽然高铅焊料是高熔点焊料,但是芯片和陶瓷基板均可承受回流时的高温而不会出现问题。此外,高铅焊料与Cu反应会形成层状Cu3 Sn,其可以持续多次回流而不发生失效。此外,Cr/Cu/Au三种金属的选用都有其特别的原因。首先,焊料不能与Al线润湿,因此利用Cu与Sn可反应形成金属间化合物而选择Cu。其次,Cu不能很好地黏附到SiO2的电介质表面,因此,选择Cr作为黏附层促进Cu与SiO2黏附。现在已经开发了Cu-Cr嵌入相的UBM以改善Cu和Cr之间的黏附性。由于Cr和Cu是不互溶的,当共沉积时它们的晶粒会形成相互嵌套的微结构。嵌入相的Cu-Cr微观结构的晶格照片将在第2章中给出。在这种嵌入相的微观结构中,Cu更好地黏附在Cr上,使其在回流过程中更难扩散脱离界面而与Sn形成金属间化合物。此外,嵌入相的微结构提供了金属间化合物的一种机械卡咬。最后,Au用作表面钝化涂层以防止Cu氧化或腐蚀,它还作为表面光洁剂来增强焊料润湿。

在第二级的陶瓷基板与印制线路板的封装中,为了将陶瓷基板连接到聚合物电路板,在陶瓷基板的背面上设计了另外一个焊料互连面阵列。它们被称为球栅阵列(Ball-grid-array,BGA)焊球,其直径比C-4焊球大得多,通常约为760μm。它们为共晶锡铅焊料,熔点较低(183℃),可在220℃左右回流。有时也会使用高铅和锡铅共晶焊料的复合焊球,其中高铅为焊球核心。很明显,在这次回流时(第三次),第一级封装中的高铅焊料接头不会熔化。

总之,在C-4倒装芯片连接中需要三步。第一步是通过电镀或通过丝印工艺在芯片表面形成面阵列焊料凸点,接着是将焊料凸点通过回流工艺转变成焊料小球。第二步是采用第二次回流工艺将芯片以倒装芯片形式键合到基板上。基板面阵列布置的焊盘承接芯片上的焊球。第三步是用环氧树脂填充芯片和基板之间的间隙。然而,第二级的BGA封装并没有进行底部填充。

图1.9 倒装芯片焊料接头的横截面示意

有关电子软钎焊连接技术 材料、性能及可靠性的文章

将n=1.8,Q=0.8 eV/原子的值代入该公式所得出的结果,被证实远远高估了倒装芯片焊点在高电流密度的平均失效时间。表9.2所示为倒装芯片焊点在三种不同的电流密度与温度下平均失效时间的计算值和测量值。这些发现表明倒装芯片焊点的平均失效时间对电流密度的微小增量都十分敏感。例如,在电流密度为2.25×104 A/cm2,温度为125℃时,无铅焊料的平均失效时间为580 h,而锡铅焊料却只有43 h。......

2023-06-20

在倒装芯片焊料接头中,虽然这两种反应分别发生在间隔约100μm的焊料接头两侧,但由于Cu及其他贵金属和近贵金属可在很短的时间内扩散穿过100μm厚的焊料接头,因此这两个反应之间并不是互相独立的。回流过程中,焊料处于熔融状态的时间约为30 s,因此对于焊料凸点两侧的Cu原子而言,它们有足够的时间通过扩散而到达对侧,并实际影响对侧的化学反应。......

2023-06-20

采用GaN LED倒装芯片的结构可以从根本上消除上述问题。图1-19 LED倒装芯片的结构示意图5.芯片键合技术光电子器件对所需要的材料在性能上有一定的要求,通常都需要有大的带宽差和在材料的折射指数上要有很大的变化。......

2023-06-15

图9.2焊点电流分布焊点电流分布二维仿真示意;焊点电流分布三维示意图9.3所示为倒装芯片焊点中电迁移损伤的一组SEM照片。由于孔洞的形成只能发生在硅晶片与阴极的接触一侧,也就是电子流入焊点的地方,所以说倒装芯片焊接中的电迁移失效模式是很独特的。......

2023-06-20

我们测试两种焊料凸点并比较它们的电迁移现象。第一次回流在把焊料凸点印刷在芯片上后完成,第二次回流是为了组装芯片和印刷线路板。为了对焊料凸点电迁移进行实时观测,在电迁移测试之前,我们采用机械和化学方法将一对焊料凸点切为截面并抛光。为了可以进行观察,要时常暂停电迁移试验,所以观察是不连续的且在不同的时间下重复进行的。图9.8观察电迁移时所用倒装芯片焊点两个横截面的原理......

2023-06-20

为了快速解决此类问题,现在的物理实现工具均具有ECO功能,所谓ECO是指工程改变命令,常见用于时序修复的EDI ECO指令有ecoAddRepeater、ecoChangeCell和ecoDeleteRe-peater三条。在定义eco-cell之后后端读入ECO网表,和ECO之前的place和route,可以进行正常的后端ECO处理流程。......

2023-06-26

因此,进行水下焊接与切割作业时,必须切实遵守水下焊接和切割的安全规定,确保施工安全。水下焊接与切割时,要注意保护作业人员的眼睛。水下焊接舱内不能放置涂料、熔剂等可能放出有毒或刺激性气体的物质。局部干法水下焊接的安全防护要求与湿法水下焊接的要求相同。......

2023-06-26

超高频脉冲TIG焊电弧形态如图8-12所示。图8-12 超高频脉冲TIG焊电弧形态图8-13 不锈钢管与球面相贯的低频焊缝图8-14 高频脉冲加低频调制波形直流双脉冲TIG焊,又可以叫作高频脉冲加低频调制,其电流脉冲波形如图8-14所示。......

2023-06-30

相关推荐